系統(tǒng)時鐘優(yōu)化可以提升系統(tǒng)的性能,但也頗具挑戰(zhàn)性。為模數(shù)轉(zhuǎn)換器設(shè)計抖動為350飛秒(fs)的編碼電路是相對容易的,但這是否能夠滿足當(dāng)今的高速需求?例如,測試AD9446-100(16 bit 100 MHz ADC)時,在Nyquist區(qū)使用100 MHz的采樣時鐘頻率,350 fs的抖動將使信噪比(SNR)下降約3 dB。如果在第三Nyquist域中使用105 MHz的模擬輸入信號測試相同的設(shè)備,SNR下降可達(dá)10 dB。為了將時鐘抖動減少到100 fs或更少,設(shè)計者需要理解時鐘抖動來自哪里,以及ADC能夠允許多大的抖動。如果在電路設(shè)計完成后才發(fā)現(xiàn)時鐘電路性能受抖動的限制,并且在設(shè)計階段中本可以很容易地避免該問題發(fā)生,這時已經(jīng)太晚了。

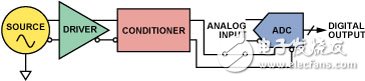

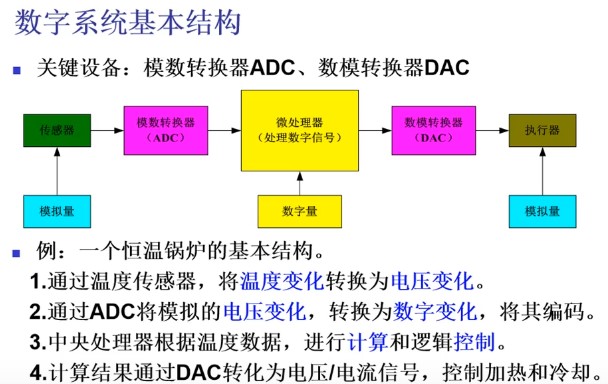

在這里我們將討論相關(guān)的時鐘參數(shù)和方法以實現(xiàn)高速轉(zhuǎn)換器預(yù)期的性能,為此要用到一些技術(shù)訣竅和經(jīng)驗。首先從典型的ADC時鐘方案開始,如圖1中所示,我們將焦點放在信號鏈路中每一級的可用于優(yōu)化時鐘的技術(shù),并且指明一些應(yīng)避免使用的常用技術(shù)。

?

圖1. 典型的時鐘信號鏈路

什么是抖動?

抖動是系統(tǒng)時鐘電路設(shè)計中最重要的參數(shù),因此了解某些基礎(chǔ)知識并且理解術(shù)語的含義是十分重要的。許多技術(shù)文獻(xiàn)描述了關(guān)于抖動的十分精確的數(shù)學(xué)模型,但是設(shè)計性能優(yōu)良的轉(zhuǎn)換器并非全部取決于精確的抖動描述。設(shè)計人員必須理解抖動如何進(jìn)入系統(tǒng)以及如何使抖動的影響最小。

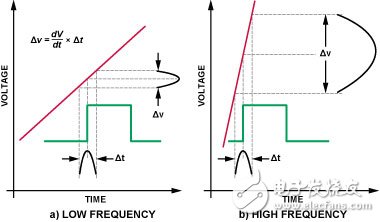

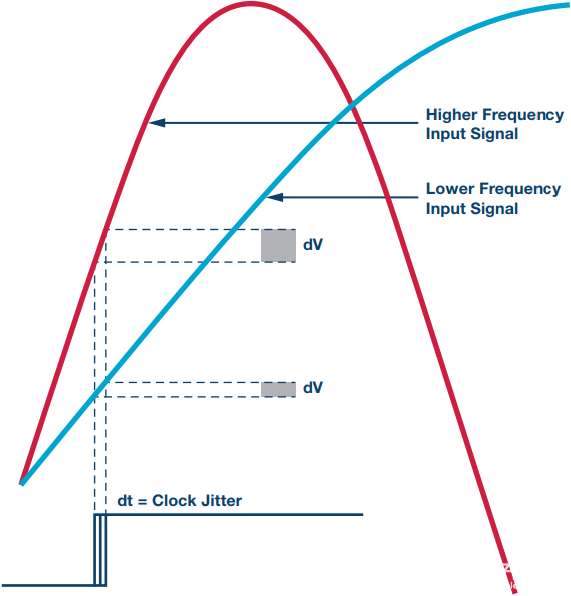

抖動是時鐘邊沿的位置變化,這將產(chǎn)生定時誤差,直接導(dǎo)致轉(zhuǎn)換幅度精度的誤差(圖2a)。模擬輸入頻率的增加導(dǎo)致輸入信號的斜率增加,這將使轉(zhuǎn)換誤差放大(圖2b)。應(yīng)當(dāng)注意,轉(zhuǎn)換誤差的度量是相對的,10 bit器件0.5 LSB(最低有效位)的轉(zhuǎn)換誤差等效于16 bit器件32 LSB的誤差。這意味著隨著ADC分辨率和模擬輸入頻率的增加,抖動變得更加引人注意。

圖2. 轉(zhuǎn)換誤差是時鐘抖動和模擬輸入頻率的函數(shù)

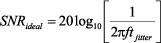

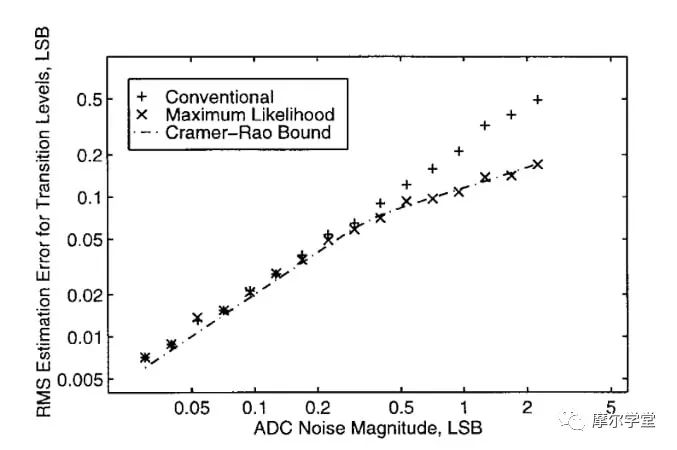

直觀上看,它們之間的關(guān)系是非常明顯的,因此工程師可以通過分析ADC性能和編碼時鐘抖動之間的關(guān)系,最終確定可接受的抖動量。式1定義了理想ADC(具有無窮大分辨率)SNR(dB)與頻率的關(guān)系,而式2定義了N(10、12、14或16)bit理想ADC的SNR(dB)。

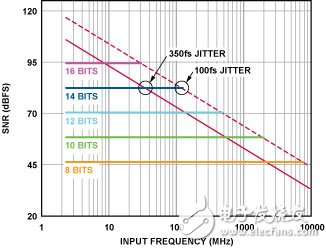

參看圖3的斜線

參看圖3的水平線

圖3是由這兩個公式畫出的曲線圖。用戶可以在曲線交點處確定給定模擬輸入信號頻率時可容忍的總時鐘抖動量。在低頻下,精度受到轉(zhuǎn)換器分辨率的限制。然而,隨著輸入信號頻率的增加,在大于某個頻點之后,ADC的性能將受控于系統(tǒng)的總時鐘抖動。位于該頻點左側(cè)的輸入信號頻率,無須考慮小抖動的問題。

?

圖3. 理想ADC的SNR vs. 模擬輸入信號頻率和抖動

然而,如果信號頻率在該頻點附近或者在其右側(cè),則必須降低頻率或分辨率,或者必須提高抖動指標(biāo)。因此,抖動越大,SNR性能受控于時鐘系統(tǒng)抖動的頻點就越低。

例如,如果使用具有350 fs抖動的時鐘測試14 bit ADC,為了避免性能下降,輸入信號頻率必須低于35 MHz(14 bit水平線與350 fs斜線的交點)。如果抖動為100 fs,則輸入信號頻率可以達(dá)到125 MHz。

實際上,當(dāng)模擬測試頻率接近交點時,使用該一階近似的簡化模型便喪失了有效性。為了全面地理解時鐘抖動對ADC性能的影響,除了分辨率以外,還要考慮量化噪聲和模擬輸入幅度(式3,基于參考文獻(xiàn)9)。

其中

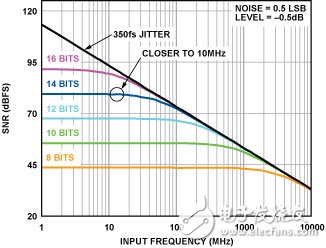

例如,假設(shè)ADC具有0.5 LSB的量化噪聲,并且在測試時模擬輸入幅度比滿刻度低0.5 dB。圖4結(jié)合了式2和式3,相比于簡化模型,編碼時鐘抖動將在更低的頻率處影響SNR性能。

圖4. SNR是模擬輸入頻率、時鐘抖動和量化噪聲的函數(shù)

前面的示例中,模擬輸入信號頻率接近35 MHz時,具有350 fs抖動的時鐘不會影響14 bit ADC的SNR。但是在考慮量化噪聲、輸入信號頻率和輸入幅度的影響后,10 MHz的信號頻率就應(yīng)被注意。同樣地,抖動為100 fs的時鐘會在低于100 MHz的頻率下引起SNR的下降。

消除抖動

在回顧有關(guān)抖動的基礎(chǔ)知識之后,我們將考慮抖動的源。能夠使得ADC時鐘沿變換的任何因素都將引入或影響抖動。這些因素包括串?dāng)_、EMI(電磁干擾)、地效應(yīng)和電源噪聲。

串?dāng)_引起的抖動可以出現(xiàn)在任意兩條相鄰的走線上。如果一條走線承載信號,而附近的平行走線承載變化的電流,則信號走線中會感生電壓。如果該信號是時鐘信號,則時鐘邊沿發(fā)生點的時刻將發(fā)生變化。

EMI輻射引發(fā)敏感信號走線上的抖動。EMI由開關(guān)電源、高壓輸電線、RF信號和其他類似的源產(chǎn)生。與串?dāng)_類似,EMI通過電磁耦合調(diào)整了信號或時鐘的時序。

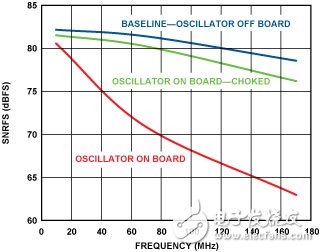

圖5說明了電磁干擾對SNR的影響。藍(lán)色曲線表示AD9446基線SNR vs. 頻率的關(guān)系,其中AD9446使用外部時鐘和線性電源。時鐘未以任何方式連接到評估板。紅色曲線給出了將相同的時鐘電路固定或焊接到評估板后出現(xiàn)的性能下降,其中時鐘電路由開關(guān)電源供電。綠色曲線給出了,如果對電源噪聲進(jìn)行濾波,則可以顯著改善轉(zhuǎn)換器的性能。

圖5. 轉(zhuǎn)換器性能 vs. 振蕩器電源配置和頻率

由開關(guān)電流或者不適當(dāng)?shù)慕拥匾鸬牡貜椧部赡軒矶秳印.?dāng)許多門電路同時切換時,開關(guān)電流會變大。這可能在電源平面和地平面上產(chǎn)生電流尖峰,使時鐘電路的閾值電壓或模擬輸入信號的電平移位。例如:

考慮PCB走線和接收門電路的輸入端,門電路輸出會具有10 pF的負(fù)載。當(dāng)門電路切換時,10 mA的動態(tài)電流流入或流出每個輸出端。[10 mA得自10 pF×1 V/ns,即CMOS門電路的典型擺率(I=C dV/dt)。] 因此,如果12個門電路同時切換,則動態(tài)電流可能累積達(dá)到120 mA。這將需要電源引腳提供很大的電流尖峰,而其中一個引腳是接地的。由引線電阻引起的瞬時壓降(跳動)將影響所有以該引線作為參考地的電路。

為了減少這些源引起的抖動,應(yīng)使用良好的布線和適當(dāng)?shù)碾娐凡季帧V匾囊稽c是將模擬電路和數(shù)字電路限制在其各自的區(qū)域中。為確保良好的隔離,每個電路層都應(yīng)遵循該原則。理解回流如何相對于源來流動以及如何避免模擬和數(shù)字電路之間的越界或交叉是十分重要的。總而言之,必須使敏感的模擬輸入和時鐘走線遠(yuǎn)離其他電路和走線,以免受到這些電路和走線的影響。

改善抖動意味著改善擺率

前面已討論了抖動的基礎(chǔ)知識及其可能帶來的影響,現(xiàn)在的問題是:如何改進(jìn)系統(tǒng)時鐘或時鐘電路以減少抖動?

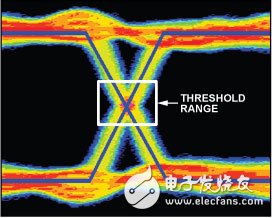

回顧之前的討論,當(dāng)抖動出現(xiàn)在轉(zhuǎn)換過程或者時鐘的閾值周期中時,抖動或噪聲僅能破壞ADC的時序,如圖6中所示。通過增加擺率使該邊沿(并且因此使閾值周期)更快,將會使閾值周期中可能出現(xiàn)噪聲的時間量變小,并使引入系統(tǒng)中的rms(均方根)抖動量變小。

圖6. 差分時鐘的閾值/轉(zhuǎn)換區(qū)域的放大示圖

應(yīng)當(dāng)注意,擺率的增加不會影響原始信號質(zhì)量,僅會影響通過閾值區(qū)域的轉(zhuǎn)換時間。為了證實這一點,參考圖2b。應(yīng)當(dāng)注意,信號擺動越快,在轉(zhuǎn)換區(qū)域中花費(fèi)的時間就越少。圖7說明了抖動和擺率之間成反比。與前面的示例結(jié)合考慮,對于12 bit ADC,輸入信號為70 MHz時抖動最少為100 fs rms,對應(yīng)擺率為1V/ns。

圖7. RMS抖動 vs. 擺率

電子發(fā)燒友App

電子發(fā)燒友App

評論