異步復位信號亞穩態的原因:

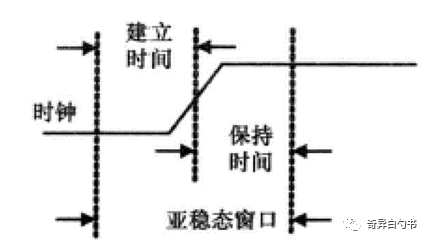

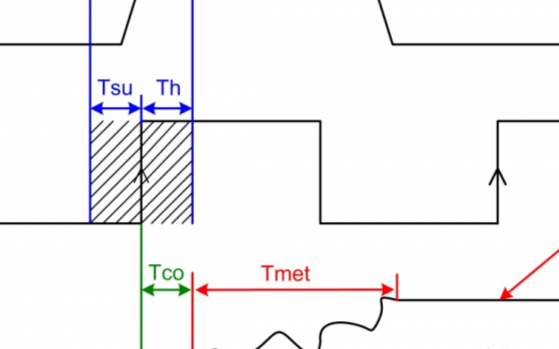

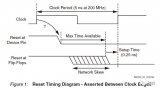

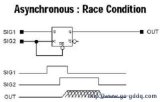

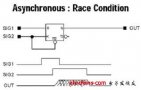

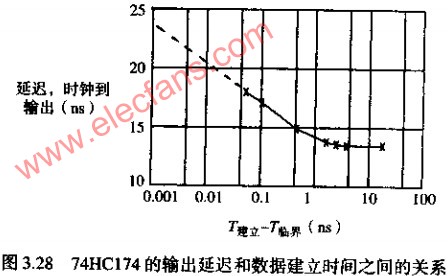

復位結束也就是釋放的時刻恰在時鐘上升沿的建立時間和保持時間之間時無法決定現在的復位狀態是1還是0,造成亞穩態。

下面是具體解釋:

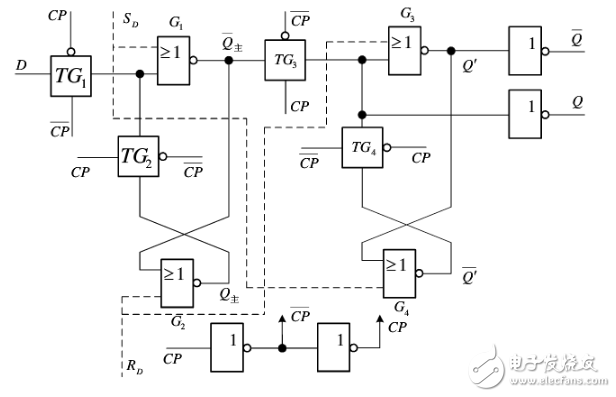

在帶有復位端的D觸發器中,當reset信號“復位”有效時,它可以直接驅動最后一級的與非門,令Q端“異步”置位為“1”or“0”。這就是異步復位。當這個復位信號release時,Q的輸出由前一級的內部輸出決定。

然而,由于復位信號不僅直接作用于最后一級門,而且也會做為前級電路的一個輸入信號,因此這個前一級的內部輸出也受到復位信號的影響。前一級的內部電路實際上是實現了一個“保持”的功能,即在時鐘沿跳變附近鎖住當時的輸入值,使得在時鐘變為高電平時不再受輸入信號的影響。

對于這一個“維持”電路,在時鐘沿變化附近,如果“reset”信號有效,那么,就會鎖存住“reset”的值;如果reset信號釋放,那么這個“維持”電路會去鎖當時的D輸入端的數據。因此,如果reset信號的“釋放”發生在靠時鐘沿很近的時間點,那么這個“維持”電路就可能既沒有足夠時間“維持”住reset值,也沒有足夠時間“維持”住D輸入端的值,因此造成亞穩態,并通過最后一級與非門傳到Q端輸出。如果reset信號的“釋放”時間能夠晚一點點,也就是說,讓“維持”電路有足夠的時間去鎖住“reset”的值,那么,我們就可以肯定輸出為穩定的“reset”狀態了。這一小段鎖住“reset”值所需要的時間,就是寄存器的removal time要求。

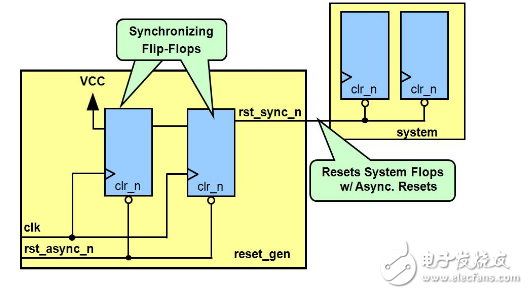

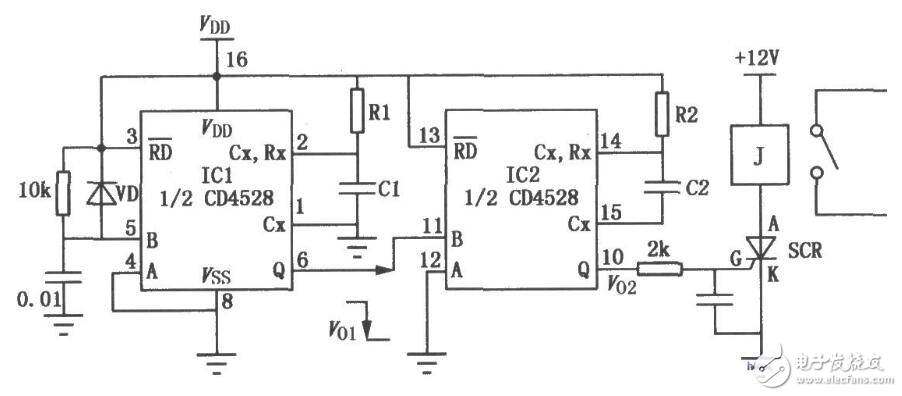

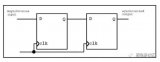

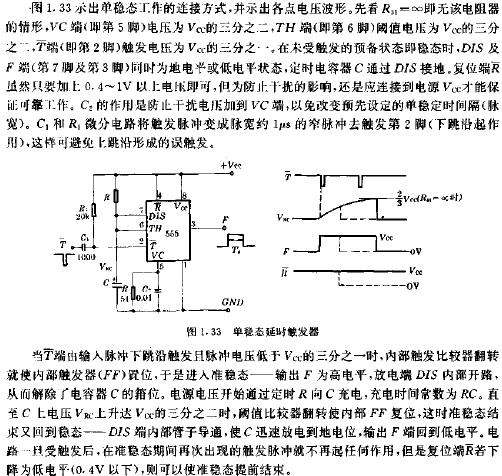

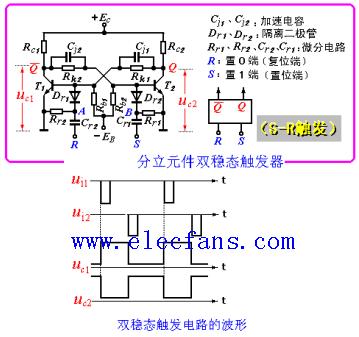

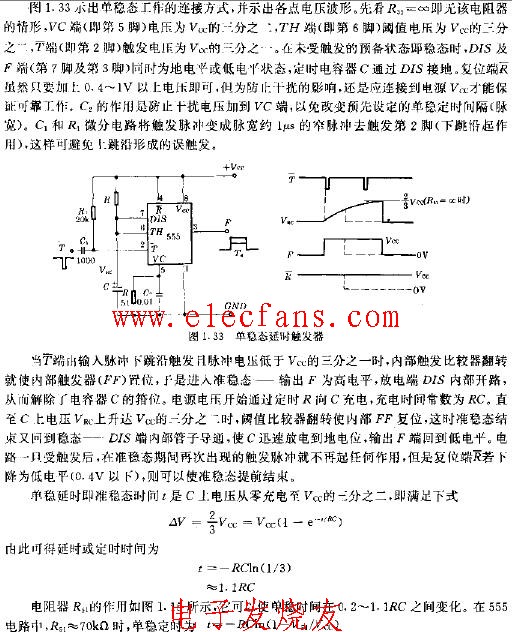

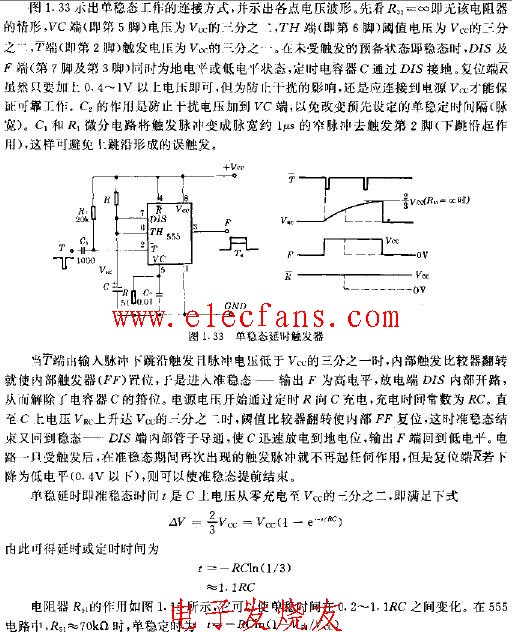

如圖第一個方框內是異步復位和同步釋放電路。有兩個D觸發器構成。第一級D觸發器的輸入時VCC,第二級觸發器輸出是可以異步復位,同步釋放后的復位信號。

利用前面兩級觸發器實現。特點:

第一級觸發器的數據端口是接電源,即高電平1’b1。

第一級觸發器的輸出,不能使用,因為仍存在亞穩態的危險。兩級觸發器做同步,是非總線信號的最常見異步處理方法。總線信號的異步處理方法,最常見的是異步fifo實現。

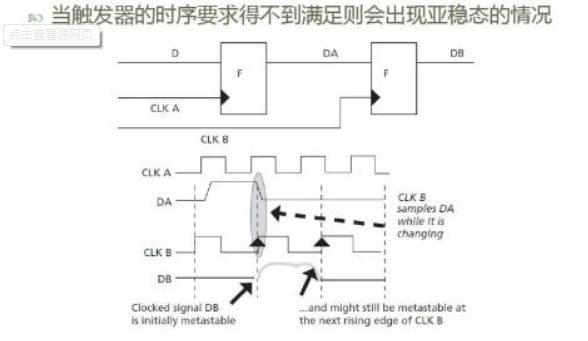

很多人只知道觸發器D端口來源是異步的話,會因為建立保持時間的時序違反而在觸發器Q端口產生亞穩態。

但是不清楚,異步復位信號為什么會導致亞穩態的產生。

首先,回顧理論教材里介紹的建立保持時間違反分析,教材一般都是拿沒有復位端口的D觸發器舉例。

然后,畫出帶有異步復位端口的D觸發器,下圖帶異步復位Rd,并帶有異步置位端口Sd。

由此得知,異步復位信號或者異步置位信號,跟數據端口D信號,沒有什么區別,都會存在建立保持時間的違反,從而時序沖突,引發輸出亞穩態。

亞穩態,出現的問題或者麻煩,是在信號變化的時候,不能保證第一拍采樣的值是固定的。

如果信號穩定,不會出現亞穩態的。就是采樣后的跳變,時刻不確定,也許早,也許晚。

系統不希望這樣的未知狀態發生,系統希望知道在某一個時刻,后續邏輯需要的輸入信號,是穩定值。

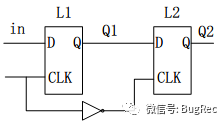

二級觸發器同步后,第二季觸發器的輸出基本上是穩定值。后續邏輯根據穩定值,會有穩定的行為。這就是追求的系統穩定性。

最好是系統一起復位釋放,但是時鐘域不同,不可能保證系統一起復位釋放。一般來說,系統復位釋放的順序,是需要保證的。否則系統就是不安全的。

舉個例子,系統啟動時,內核讀取啟動指令,要powerdown某外設;但是powerdown的邏輯要求外設和內核沒有通信請求正在發生。此時,外設比內核先釋放復位的情況(復位釋放的時刻,外設有可能已經開始與內核發生請求),與內核比外設先釋放復位的情況(復位釋放的時刻,外設肯定與內核沒有發生請求),是不一樣的,powerdown也許不能處理成功。

這也是異步復位信號需要同步釋放的原因,目的都是為了避免亞穩態的產生。

第一級觸發器的輸出,永遠存在亞穩態的可能。亞穩態,導致系統不會復位初始化到已知狀態。

當第一級觸發器采樣異步輸入之后,允許輸出出現的亞穩態可以長達一個周期,在這個周期內,亞穩態特性減弱。在第二個時鐘沿到來時,第二級同步器采樣,之后才把該信號傳遞到內部邏輯中去。第二級輸出是穩定且已被同步了的。如果在第二級采樣時保持時間不夠,第一級的輸出仍然處于很強的亞穩態,將會導致第二級同步器也進入亞穩態,但這種故障出現的概率比較小。

一般情況下,兩級同步器總體的故障概率是一級同步器故障概率的平方。在大部分的同步化設計中,兩級同步器足以消除所有可能的亞穩態了。

基本D觸發器、同步D觸發器和異步D觸發器的Verilog描述

//基本D觸發器

module D_EF(Q,D,CLK)

input D,CLK;

output Q;

reg Q; //在always語句中被賦值的信號要聲明為reg類型 寄存器定義

always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要記憶

begin Q 《= D; end

endmodule

//帶異步清0、異步置1的D觸發器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;//寄存器定義

always @ (posedge clk or negedge set or negedge reset)

begin

if(!reset) begin q《=0;qn《=1;end//異步清0,低有效

else if(!set) begin q《=1;qn《=1;end //異步置1,低有效

else begin q《=~d;qn《=~d;end

end

endmodule

//帶同步清0、同步置1的D觸發器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;

always @ (posedge clk)

begin

if(reset) begin q《=0;qn《=1;end//同步清0,高有效

else if(set) begin q《=1;qn《=1;end //同步置1,高有效

else begin q《=~d;qn《=~d;end

end

endmodule

電子發燒友App

電子發燒友App

評論