ADC/模數(shù)轉(zhuǎn)換器簡介

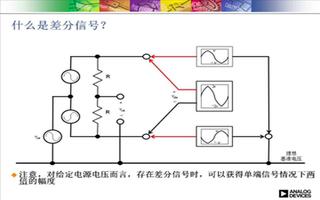

模數(shù)轉(zhuǎn)換器即A/D轉(zhuǎn)換器,或簡稱ADC,通常是指一個(gè)將模擬信號(hào)轉(zhuǎn)變?yōu)?a target="_blank">數(shù)字信號(hào)的電子元件。通常的模數(shù)轉(zhuǎn)換器是將一個(gè)輸入電壓信號(hào)轉(zhuǎn)換為一個(gè)輸出的數(shù)字信號(hào)。由于數(shù)字信號(hào)本身不具有實(shí)際意義,僅僅表示一個(gè)相對(duì)大小。故任何一個(gè)模數(shù)轉(zhuǎn)換器都需要一個(gè)參考模擬量作為轉(zhuǎn)換的標(biāo)準(zhǔn),比較常見的參考標(biāo)準(zhǔn)為最大的可轉(zhuǎn)換信號(hào)大小。而輸出的數(shù)字量則表示輸入信號(hào)相對(duì)于參考信號(hào)的大小。

分類及特點(diǎn)

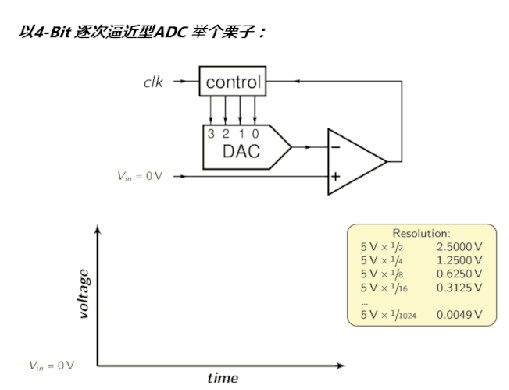

模數(shù)轉(zhuǎn)換器的種類很多,按工作原理的不同,可分成間接ADC和直接ADC。間接ADC是先將輸入模擬電壓轉(zhuǎn)換成時(shí)間或頻率,然后再把這些中間量轉(zhuǎn)換成數(shù)字量,常用的有雙積分型ADC。直接ADC則直接轉(zhuǎn)換成數(shù)字量,常用的有并聯(lián)比較型ADC和逐次逼近型ADC。

并聯(lián)比較型ADC:采用各量級(jí)同時(shí)并行比較,各位輸出碼也是同時(shí)并行產(chǎn)生,所以轉(zhuǎn)換速度快。并聯(lián)比較型ADC的缺點(diǎn)是成本高、功耗大。

逐次逼近型ADC:它產(chǎn)生一系列比較電壓VR,但它是逐個(gè)產(chǎn)生比較電壓,逐次與輸入電壓分別比較,以逐漸逼近的方式進(jìn)行模數(shù)轉(zhuǎn)換的。它比并聯(lián)比較型ADC的轉(zhuǎn)換速度慢,比雙分積型ADC要快得多,屬于中速ADC器件。

雙積分型ADC:它先對(duì)輸入采樣電壓和基準(zhǔn)電壓進(jìn)行兩次積分,獲得與采樣電壓平均值成正比的時(shí)間間隔,同時(shí)用計(jì)數(shù)器對(duì)標(biāo)準(zhǔn)時(shí)鐘脈沖計(jì)數(shù)。它的優(yōu)點(diǎn)是抗干擾能力強(qiáng),穩(wěn)定性好;主要缺點(diǎn)是轉(zhuǎn)換速度低。

ADC工作原理

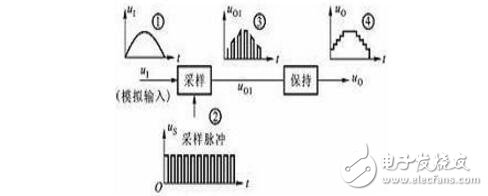

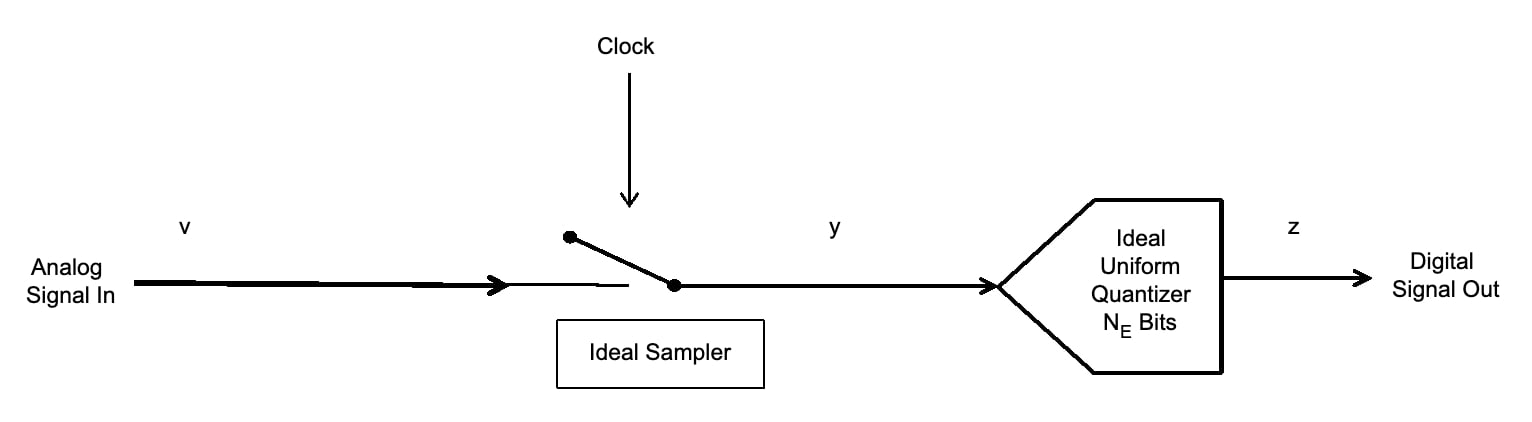

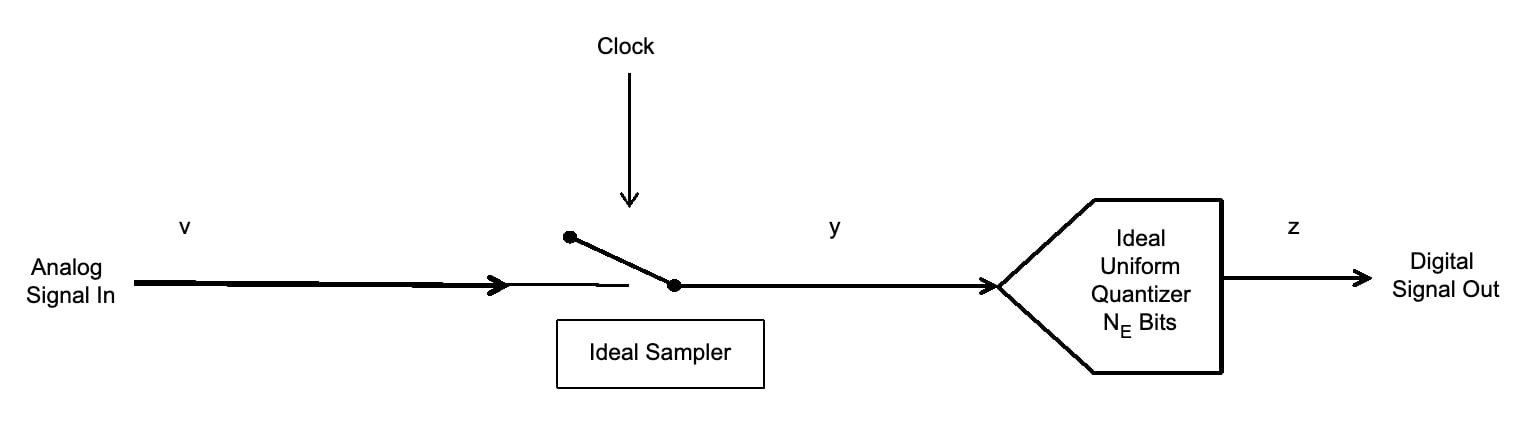

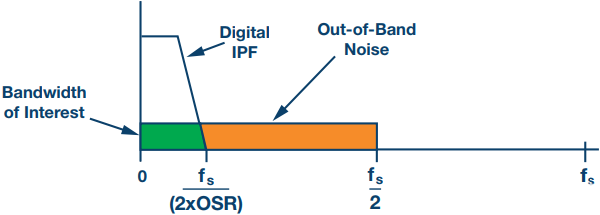

輸入端輸入的模擬電壓,經(jīng)采樣、保持、量化和編碼四個(gè)過程的處理,轉(zhuǎn)換成對(duì)應(yīng)的二進(jìn)制數(shù)碼輸出。采樣就是利用模擬開關(guān)將連續(xù)變化的模擬量變成離散的數(shù)字量,如上圖中波形③所示。由于經(jīng)采樣后形成的數(shù)字量寬度較窄,經(jīng)過保持電路可將窄脈沖展寬,形成梯形波,如波形④所示。量化就是將階梯形模擬信號(hào)中各個(gè)電壓值轉(zhuǎn)化為某個(gè)最小單位的整數(shù)倍,便于用數(shù)字量來表示。編碼就是將量化的結(jié)果(即整數(shù)倍值)用二進(jìn)制數(shù)碼來表示。。這個(gè)過程就實(shí)現(xiàn)了模/數(shù)轉(zhuǎn)換。目前集成模/數(shù)轉(zhuǎn)換器種類較多,有8位、10位模/數(shù)轉(zhuǎn)換器。

ADC位數(shù)的確定

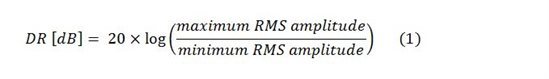

ADC位數(shù)是根據(jù)傳輸方式和噪聲來計(jì)算的。如,64QAM/7/8碼率在視頻解碼正常的最低信噪比為28dB(某種衰落信道下);OFDM在輕微削波時(shí)的峰均比假設(shè)為11dB,所以ADC的最大信噪比至少要40dB,考慮信號(hào)波動(dòng)給AGC留出3dB的余量,那么ADC至少要42/6=7位。剩下的就應(yīng)該是考慮到噪聲等因素留的余量了。

ADC每增加一位,信噪比提高6dB,前提是輸入ADC的波形沒有噪聲。模擬信號(hào)的信噪比是一定的,ADC之后的信號(hào)的最高信噪比也就定了。

我覺得得分情況。有兩點(diǎn):首先RF指標(biāo)不可能無限高的;其次,RF指標(biāo)越高成本越高。對(duì)低成本系統(tǒng),是鏈路預(yù)算決定射頻指標(biāo),如wlan;對(duì)高成本系統(tǒng),可能是RF指標(biāo)決定鏈路預(yù)算,如星際通信。

選AD,看接收信號(hào)的動(dòng)態(tài)范圍要求和解調(diào)性能的要求。 非線性指標(biāo),取決于接收信號(hào)的特性以及干擾的特性。

ADC有效位數(shù)的理解

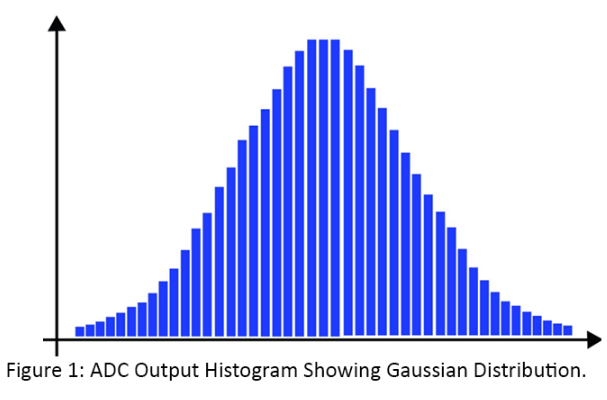

假設(shè)一個(gè)12位非理想的ADC,其ENOB為10bit,這并不表示把ADC的后兩位刪掉就可以當(dāng)做一個(gè)理想的10bitADC來使用,如果去掉后兩位把該ADC作為一個(gè)10bit的ADC來測試,你會(huì)發(fā)現(xiàn)它的ENOB不到10bit。

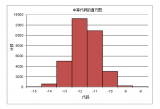

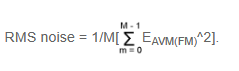

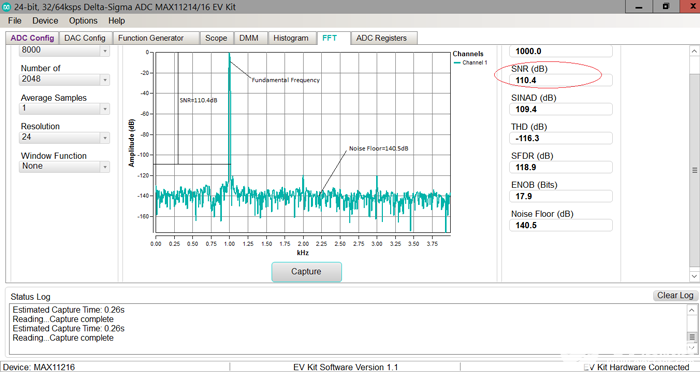

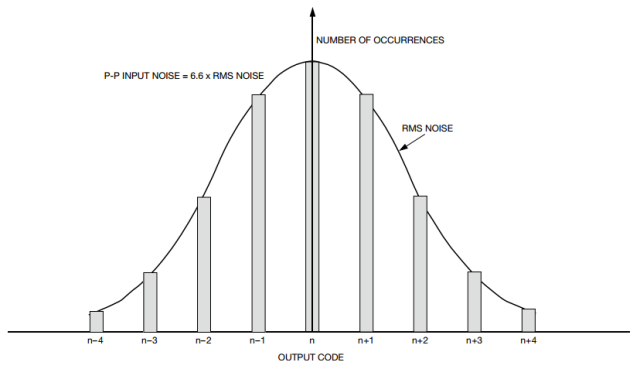

ENOB的計(jì)算方法是使用ADC測量出的SNDR根據(jù)公式SNDR=6.02*ENOB+1.76換算而來的,從這個(gè)公式我們可以明白這里ENOB的意思是12bit非理想ADC的SNDR與理想的10bitADC的SNR相等。

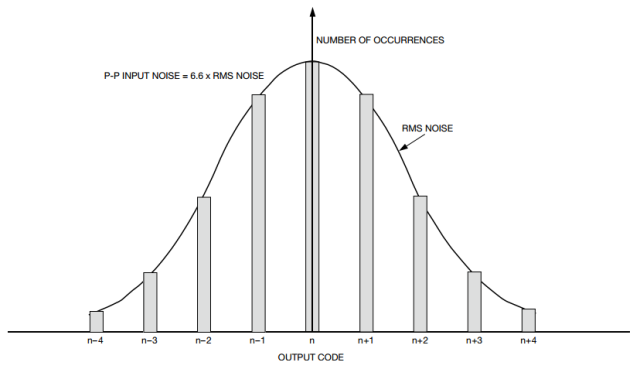

對(duì)于一個(gè)非理想的ADC,其輸出不僅有量化噪聲,還有失真引起的高次諧波,所以會(huì)在SNDR的計(jì)算中抵消一部分精度。

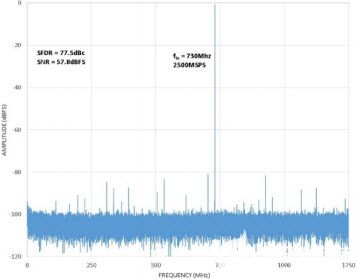

信噪失真比 SNDR

SNDR是指頻帶內(nèi)信號(hào)總功率和噪聲以及諧波功率之和的比值。它的定義和SNR的定義類似,只是為了強(qiáng)調(diào)ADC中的諧波失真。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論