3)、在RCC的中斷處理程序中,再對HSE和PLL進行相應的處理。

注意:一旦CSS被激活,當HSE時鐘出現故障時將產生CSS中斷,同時自動產生 NMI。NMI將被不斷執行,直到CSS中斷掛起位被清除。因此,在NMI的處理程序中 必須通過設置時鐘中斷寄存器(RCC_CIR)里的CSSC位來清除CSS中斷。

2、SysTick工作原理

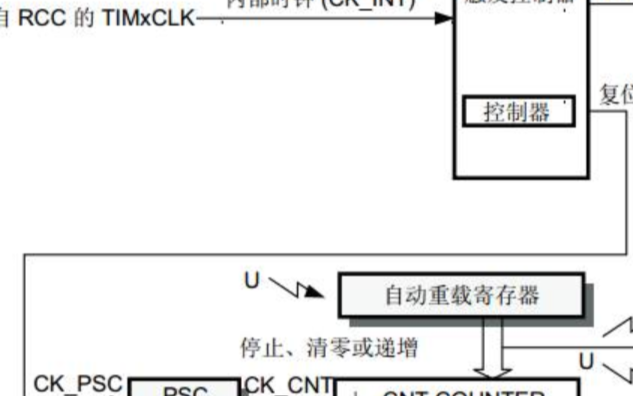

Cortex-M3的內核中包含一個SysTick時鐘。SysTick 為一個24位遞減計數器,SysTick設定初值并使能后, 每經過1個系統時鐘周期,計數值就減1。計數到0時, SysTick計數器自動重裝初值并繼續計數,同時內部的 COUNTFLAG標志會置位,觸發中斷(如果中斷使能)。

3、內部時鐘輸出PA.8(MCO)

STM32的PA.8引腳具有復用功能——時鐘輸出(MCO), 該功能能將STM32內部的時鐘通過PA.8輸出。

操作流程:

1)、設置PA.8為復用Push-Pull模式。

GPIO_InitStructure.GPIO_Pin GPIO_Pin_8;

GPIO_InitStructure.GPIO_Speed GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode GPIO_Mode_AF_PP;

GPIO_Init(GPIOA, &GPIO_InitStructure);

2)、選擇輸出時鐘源。

時鐘的選擇由時鐘配置寄存器(RCC_CFGR)中的MCO[2:0]位控制。

RCC_MCOConfig(RCC_MCO);

參數RCC_MCO為要輸出的內部時鐘:

RCC_MCO_NoClock --- 無時鐘輸出

RCC_MCO_SYSCLK --- 輸出系統時鐘(SysCLK)

RCC_MCO_HSI --- 輸出內部高速8MHz的RC振蕩器的時鐘(HSI)

RCC_MCO_HSE --- 輸出高速外部時鐘信號(HSE)

RCC_MCO_PLLCLK_Div2 --- 輸出PLL倍頻后的二分頻時鐘(PLLCLK/2)

注:由于STM32 GPIO輸出管腳的最大響應頻率為50MHz,如果輸出頻率超過50MHz,則輸出的波形會失真。

4、可編程電壓監測器(PVD)

STM32內部自帶PVD功能,用于對MCU供電電壓VDD進行監控。通過電源控制寄存器中的PLS[2:0]位可以用來設定監控電壓的閥值,通過對外部電壓進行比較來監控電源。當條件觸發,需要系統進入特別保護狀態,執行緊急關閉任務:對系統的一些數據保存起來,同時對外設進行相應的保護操作。

操作流程:

1)、系統啟動后啟動PVD,并開啟相應的中斷。

PWR_PVDLevelConfig(PWR_PVDLevel_2V8); // 設定監控閥值

PWR_PVDCmd(ENABLE); // 使能PVD

EXTI_StructInit(&EXTI_InitStructure);

EXTI_InitStructure.EXTI_Line EXTI_Line16; // PVD連接到中斷線16上

EXTI_InitStructure.EXTI_Mode EXTI_Mode_Interrupt; //使用中斷模式

EXTI_InitStructure.EXTI_Trigger EXTI_Trigger_Raising;//電壓低于閥值時產生中斷

EXTI_InitStructure.EXTI_LineCmd ENABLE; // 使能中斷線

EXTI_Init(&EXTI_InitStructure); // 初始

EXTI_InitStructure.EXTI_Trigger的賦值可選項:

EXTI_Trigger_Rising---表示電壓從高下降到低于設定閥值時產生中斷;

EXTI_Trigger_Falling---表示電壓從低上升到高于設定閥值時產生中斷;

EXTI_Trigger_Rising_Falling---表示電壓上升或下降越過設定閥值時都產生中斷。

2)、當工作電壓低于設定閥值時,將產生PVD中斷,在中斷程序中進行相應的處理:

void PVD_IRQHandler(void)

{

EXTI_ClearITPendingBit(EXTI_Line16);

…… // 用戶添加緊急處理代碼處

}

5、STM32上不使用外部晶振,OSC_IN和OSC_OUT的接法

1)、對于100腳或144腳的產品,OSC_IN應接地,OSC_OUT應懸空。

2)、對于少于100腳的產品,有2種接法:

2.1)、OSC_IN和OSC_OUT分別通過10K電阻接地。

此方法可提高EMC性能。

2.2)、分別重映射OSC_IN和OSC_OUT至PD0和PD1,再配置PD0和PD1為推挽輸出并輸出‘0’。

此方法可以減小功耗并(相對上面2.1),并節省2個外部電阻。

Interrupt/Evens

1、NVIC的優先級概念占先式優先級 (pre-emption priority):

高占先式優先級的中斷事件會打斷當前的主程序/中斷程序運行— —搶斷式優先響應,俗稱中斷嵌套。

副優先級(subpriority):

在占先式優先級相同的情況下,高副優先級的中斷優先被響應;

在占先式優先級相同的情況下,如果有低副優先級中斷正在執行, 高副優先級的中斷要等待已被響應的低副優先級中斷執行結束后才 能得到響應——非搶斷式響應(不能嵌套)。

2、判斷中斷是否會被響應的依據

首先是占先式優先級,其次是副優先級;

占先式優先級決定是否會有中斷嵌套;

Reset、NMI、Hard Fault 優先級為負(高于普通中斷優先級)且不可調整。

3、STM32中用到的Cortex-M3寄存器說明

在STM32中用到了Cortex-M3定義的三組寄存器,有關這三組寄存器的說明不在STM32的技術手冊中,需要參考ARM公司發布的Cortex-M3 Technical Reference Manual (r2p0)。

在STM32的固件庫中定義了三個結構體與這三個寄存器組相對應,這三個結構體與ARM手冊中寄存器的對應關系如下:

1)、NVIC寄存器組

STM32的固件庫中有如下定義:

typedef struct

{

vu32 ISER[2];

u32 RESERVED0[30];

vu32 ICER[2];

u32 RSERVED1[30];

vu32 ISPR[2];

u32 RESERVED2[30];

vu32 ICPR[2];

u32 RESERVED3[30];

vu32 IABR[2];

u32 RESERVED4[62];

vu32 IPR[11];

} NVIC_TypeDef;

電子發燒友App

電子發燒友App

評論