晶體振蕩器是指從一塊石英晶體上按一定方位角切下薄片(簡稱為晶片),石英晶體諧振器,簡稱為石英晶體或晶體、晶振;而在封裝內(nèi)部添加IC組成振蕩電路的晶體元件稱為晶體振蕩器。其產(chǎn)品一般用金屬外殼封裝,也有用玻璃殼、陶瓷或塑料封裝的。

晶振的使用

晶振,在電氣上它可以等效成一個電容和一個電阻并聯(lián)再串聯(lián)一個電容的二端網(wǎng)絡(luò),電工學上這個網(wǎng)絡(luò)有兩個諧振點,以頻率的高低分其中較低 的頻率是串聯(lián)諧振,較高的頻率是并聯(lián)諧振。由于晶體自身的特性致使這兩個頻率的距離相當?shù)慕咏谶@個極窄的頻率范圍內(nèi),晶振等效為一個電感,所以只要晶 振的兩端并聯(lián)上合適的電容它就會組成并聯(lián)諧振電路。這個并聯(lián)諧振電路加到一個負反饋電路中就可以構(gòu)成正弦波振蕩電路,由于晶振等效為電感的頻率范圍很窄, 所以即使其他元件的參數(shù)變化很大,這個振蕩器的頻率也不會有很大的變化。

晶振有一個重要的參數(shù),那就是負載電容值,選擇與負載電容值相等的并聯(lián)電容,就可以得到晶振標稱的諧振頻率。

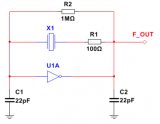

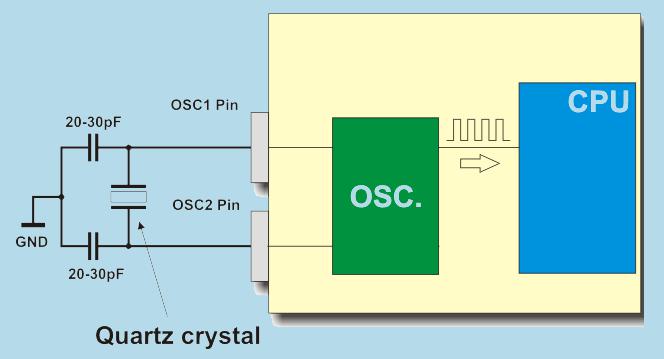

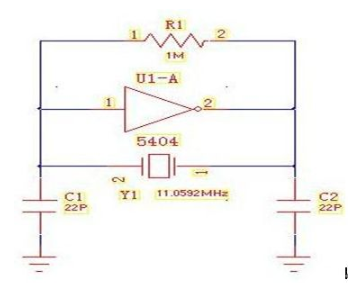

一般的晶振振蕩電路都是在一個反相放大器(注意是放大器不是反相器)的兩端接入晶振,再有兩個電容分別接到晶振的兩端,每個電容的另一端再接到地,這兩個電容串聯(lián)的容量值就應(yīng)該等于負載電容,請注意一般IC的引腳都有等效輸入電容,這個不能忽略。

一般的晶振的負載電容為15p或12.5p ,如果再考慮元件引腳的等效輸入電容,則兩個22p的電容構(gòu)成晶振的振蕩電路就是比較好的選擇。

晶振是為電路提供頻率基準的元器件,通常分成有源晶振和無源晶振兩個大類,無源晶振需要芯片內(nèi)部有振蕩器,并且晶振的信號電壓根據(jù)起振電路而定,允許不同的電壓,但無源晶振通常信號質(zhì)量和精度較差,需要精確匹配外圍電路(電感、電容、電阻等),如需更換晶振時要同時更換外圍的電路。有源晶振不需要芯片的內(nèi)部振蕩器,可以提供高精度的頻率基準,信號質(zhì)量也較無源晶振要好。

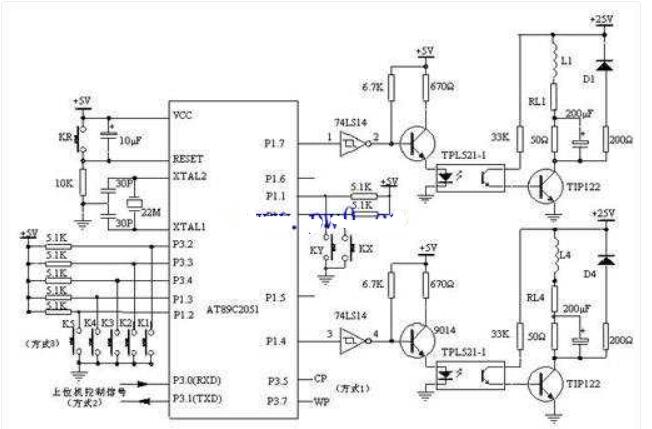

每種芯片的手冊上都會提供外部晶振輸入的標準電路,會表明芯片的最高可使用頻率等參數(shù),在設(shè)計電路時要掌握。與計算機用CPU不同,單片機現(xiàn)在所能接收的晶振頻率相對較低,但對于一般控制電路來說足夠了。

晶體振蕩器也分為無源晶振和有源晶振兩種類型。無源晶振與有源晶振(諧振)的英文名稱不同,無源晶振為crystal(晶體),而有源晶振則叫做oscillator(振蕩器)。無源晶振需要借助于時鐘電路才能產(chǎn)生振蕩信號,自身無法振蕩起來,所以“無源晶振”這個說法并不準確;有源晶振是一個完整的諧振振蕩器。

諧振振蕩器包括石英(或其晶體材料)晶體諧振器,陶瓷諧振器,LC諧振器等。

晶振與諧振振蕩器有其共同的交集有源晶體諧振振蕩器。

石英晶片所以能做振蕩電路(諧振)是基于它的壓電效應(yīng),從物理學中知道,若在晶片的兩個極板間加一電場,會使晶體產(chǎn)生機械變形;反之,若在極板間施加機械力,又會在相應(yīng)的方向上產(chǎn)生電場,這種現(xiàn)象稱為壓電效應(yīng)。如在極板間所加的是交變電壓,就會產(chǎn)生機械變形振動,同時機械變形振動又會產(chǎn)生交變電場。一般來說,這種機械振動的振幅是比較小的,其振動頻率則是很穩(wěn)定的。但當外加交變電壓的頻率與晶片的固有頻率(決定于晶片的尺寸)相等時,機械振動的幅度將急劇增加,這種現(xiàn)象稱為壓電諧振,因此石英晶體又稱為石英晶體諧振器。 其特點是頻率穩(wěn)定度很高。

石英晶體振蕩器與石英晶體諧振器都是提供穩(wěn)定電路頻率的一種電子器件。石英晶體振蕩器是利用石英晶體的壓電效應(yīng)來起振,而石英晶體諧振器是利用石英晶體和內(nèi)置IC來共同作用來工作的。振蕩器直接應(yīng)用于電路中,諧振器工作時一般需要提供3.3V電壓來維持工作。振蕩器比諧振器多了一個重要技術(shù)參數(shù)為:諧振電阻(RR),諧振器沒有電阻要求。RR的大小直接影響電路的性能,也是各商家競爭的一個重要參數(shù)。

關(guān)于外部時鐘晶振頻率選擇

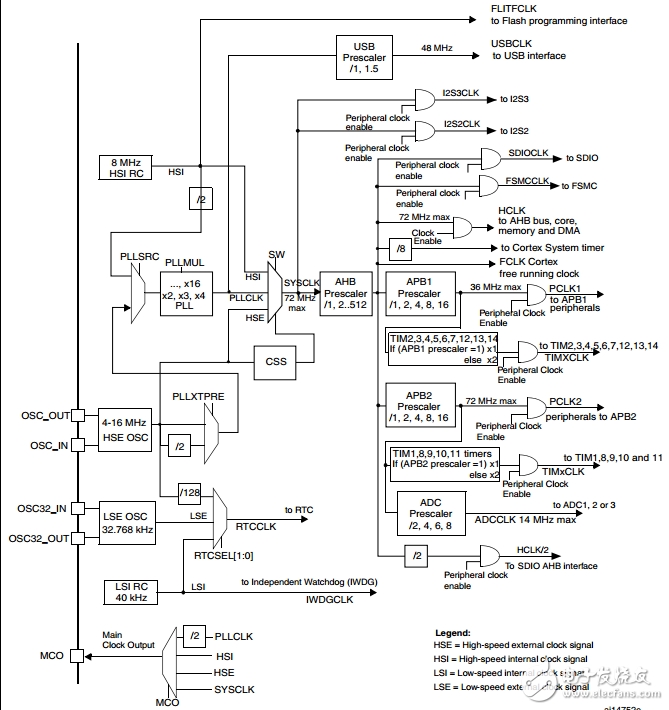

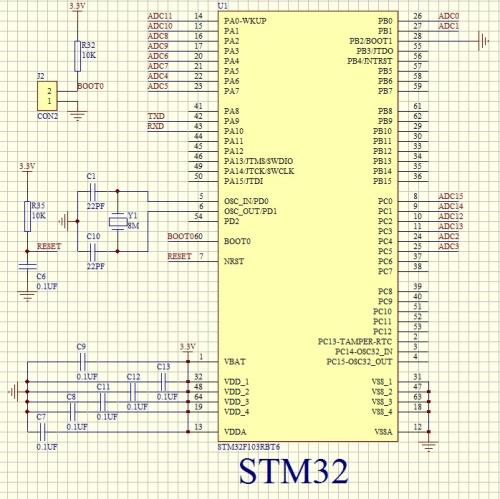

下圖是時鐘樹(Figure 8. Clock tree),它完全地列出來STM32這個芯片內(nèi)部各個模塊的時鐘來源以及相關(guān)的從屬關(guān)系。

在這個圖的正中央,有一個核心時鐘:SYSCLK,它最大頻率是72MHz,它的時鐘信號通過選擇器SW可以由PLLCLK提供(也可由HIS、HSE提供)。

PLL,毫無疑問,它是用來倍頻的,可以*2,*3,*4……*16,它的時鐘信號通過選擇器PLLSRC可以由8MHz的高速內(nèi)部RC振蕩器經(jīng)過二分頻提供,也可由PLLXTPRE的選擇器輸出提供,

而PLLXTPRE的選擇器就接的是我們的8MHz的高速外部時鐘(直接接入或二分頻接入)。

總的來說,對于我們這個板子,若使用高速外部時鐘給STM32內(nèi)核提供時鐘源,一般以下兩條路:

① [高速外部時鐘:8MHz]》》》[不分頻:8MHz]》》》》[PLL倍頻,2到16倍]》》》[SYSCLK,16MHz-128MHz]

②[高速外部時鐘:8MHz]》》》[二分頻:4MHz]》》》》[PLL倍頻,2到16倍]》》》[SYSCLK,8MHz-64MHz]

我們注意到,在8MHz外部時鐘給PLL之前若分頻的話,那么最大(×16)才64MHz,因此,我們都會給PLL以8MHz的時鐘源讓其倍頻,這樣能使它發(fā)揮到72MHz的高頻率

正因如此,系統(tǒng)時鐘總是8的倍數(shù)。

我們看這個芯片的數(shù)據(jù)手冊,立刻就能明白,不是必須得接8MHz的晶振的

① 高速外部時鐘源頻率范圍(P55-P58):1MHz~25MHz(有源);4MHz~16MHz(無源)

② PLL輸入時鐘源頻率范圍(P62):1MHz-25MHz

③ PLL輸出時鐘源頻率范圍(P62):16MHz~72MHz

我們自己設(shè)計板子的時候只要滿足它的范圍就可以了。

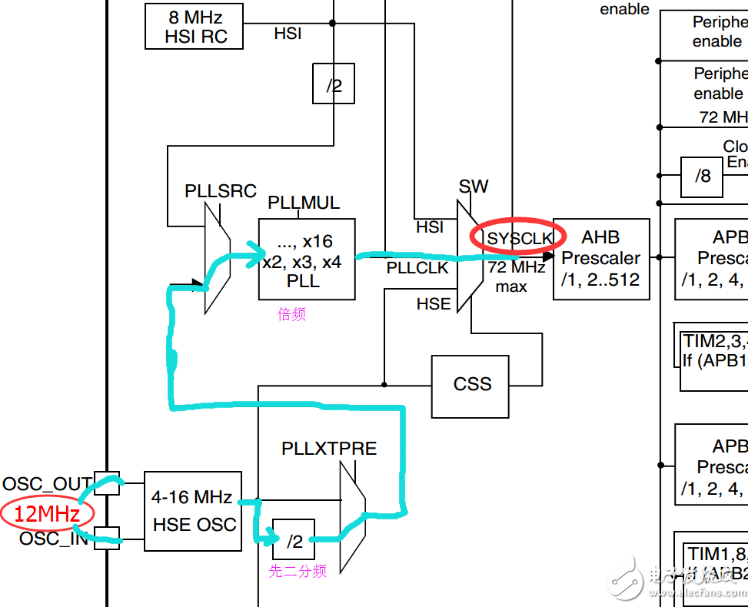

例如:我們可以選擇一個12MHz的無源晶體接到STM32芯片上。

在給STM32進行時鐘配置的時候,

① 選擇PLLXTMRE的輸入源為12MHz/2 = 6MHz

② 選擇PLLSRC的輸入源為PLLXTMRE的輸出6MHz,

③ 在PLL內(nèi)進行3到12倍的倍頻(最小16MHz,最大72MHz),

最終我們可選擇的頻率就有:18MHz、24MHz、30MHz、36MHz、42MHz、48MHz、54MHz、60MHz、66MHz、72MHz

圖示:

電子發(fā)燒友App

電子發(fā)燒友App

評論