大家都知道74hc138是一個譯碼器,那么什么是譯碼器,74hc138又有怎樣的功能呢?本文將主要介紹的是關于74hc138的的原理功能解析,幫助你更深的了解74hc138元器件。

譯碼器

譯碼器簡介

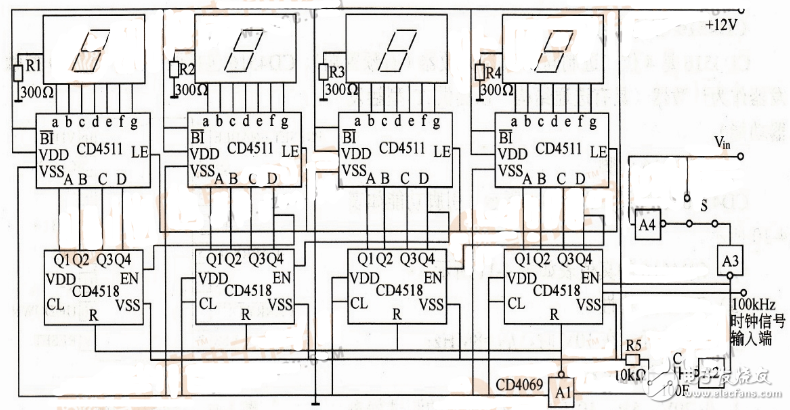

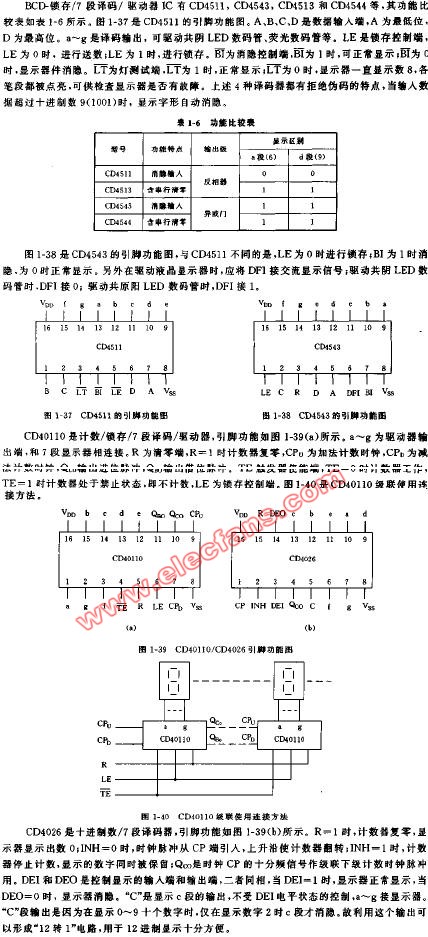

碼器(decoder)是一類多輸入多輸出組合邏輯電路器件,其可以分為:變量譯碼和顯示譯碼兩類。變量譯碼器一般是一種較少輸入變為較多輸出的器件,常見的有n線-2^n線譯碼和8421BCD碼譯碼兩類;顯示譯碼器用來將二進制數轉換成對應的七段碼,一般其可分為驅動LED和驅動LCD兩類。

譯碼器分類

譯碼器的種類很多,但它們的工作原理和分析設計方法大同小異,其中二進制譯碼器、二-十進制譯碼器和顯示譯碼器是三種最典型,使用十分廣泛的譯碼電路。

二進制碼譯碼器,也稱最小項譯碼器,N中取一譯碼器,最小項譯碼器一般是將二進制碼譯為十進制碼;

代碼轉換譯碼器,是從一種編碼轉換為另一種編碼;

顯示譯碼器,一般是將一種編碼譯成十進制碼或特定的編碼,并通過顯示器件將譯碼器的狀態顯示出來。

74hc138

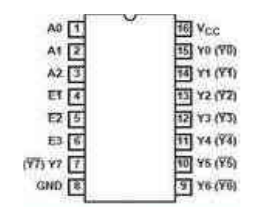

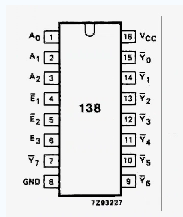

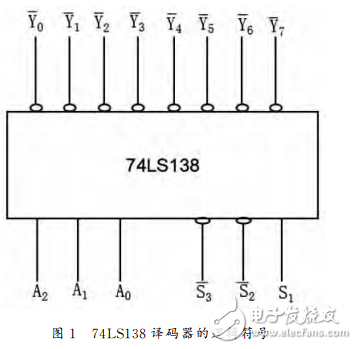

74HC138是一款高速CMOS器件,74HC138引腳兼容低功耗肖特基TTL(LSTTL)系列。74HC138譯碼器可接受3位二進制加權地址輸入(A0, A1和A2),并當使能時,提供8個互斥的低有效輸出(Y0至Y7)。

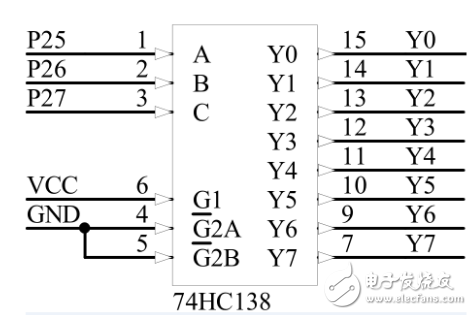

?

74HC138特有3個使能輸入端:兩個低有效(E1和E2)和一個高有效(E3)。除非E1和E2置低且E3置高,否則74HC138將保持所有輸出為高。

74HC138是高速硅柵CMOS解碼器,適合內存地址解碼或數據路由應用。74HC138 作用原理于高性能的存貯譯碼或要求傳輸延遲時間短的數據傳輸系統,在 高性能存貯器系統中,用這種譯碼器可以提高譯碼系統的效率。將快速賦能電路用于高速存貯器時,譯碼器的延遲時間和存貯器的賦能時間通常小于存貯器的典型存取時間,這就是說由肖特基鉗位的系統譯碼器所引起的有效系統延遲可以忽略不計。HC138 按照三位二進制輸入碼和賦能輸入條件,從8 個輸出端中譯出一個 低電平輸出。兩個低電平有效的賦能輸入端和一個高電平有效的賦能輸入端減少了擴展所需要的外接門或倒相器,擴展成24 線譯碼器不需外接門;擴展成32 線譯碼器,只需要接一個外接倒相器。在解調器應用中,賦能輸入端可用作數據輸入端。

74hc138的功能

74HC138譯碼器可接受3位二進制加權地址輸入(A0, A1和A2),并當使能時,提供8個互斥的低有效輸出(Y0至Y7)。74HC138特有3個使能輸入端:兩個低有效(E1和E2)和一個高有效(E3)。除非E1和E2置低且E3置高,否則74HC138將保持所有輸出為高。利用這種復合使能特性,僅需4片74HC138芯片和1個反相器,即可輕松實現并行擴展,組合成為一個1-32(5線到32線)譯碼器。任選一個低有效使能輸入端作為數據輸入,而把其余的使能輸入端作為選通端,則74HC138亦可充當一個8輸出多路分配器,未使用的使能輸入端必須保持綁定在各自合適的高有效或低有效狀態。

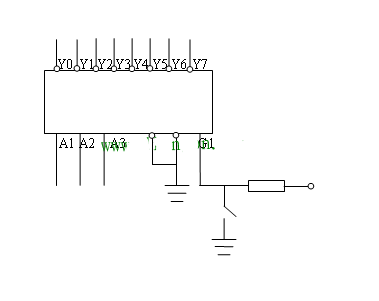

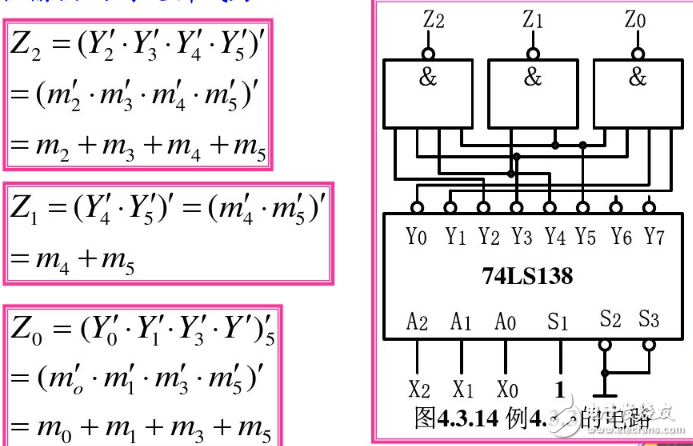

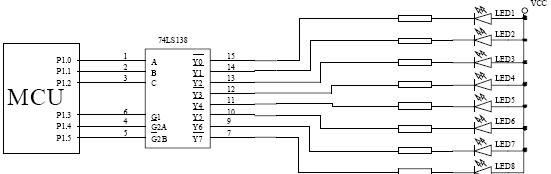

74HC138原理圖

以上便是138譯碼器的原理圖。其中,在芯片第4、5引腳處,標識符G2A和G2B上面有一橫杠,這個意思是代表此端口輸出低電平有效(可見,4、5引腳連接的是GND),而第6引腳連接的VCC。?

74HC138譯碼器可接受3位二進制加權地址輸入(A,B和C),并當使能時,提供8個互斥的低有效輸出(Y0~Y7)。74HC138特有3個使能輸入端:兩個低電平有效(G2A、G2B)和一個高有效(G1)。除非G2A和G2B置低且G1置高,否則74HC138將保持所有輸出為高。

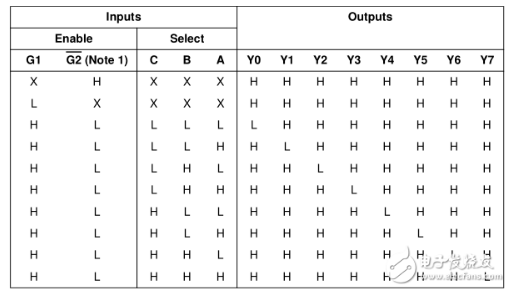

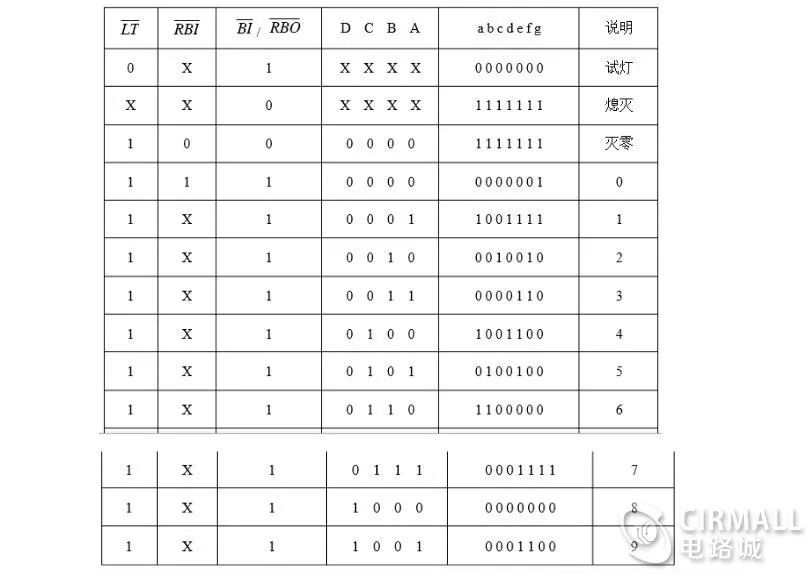

其真值表如下所示(可通過芯片手冊進行查閱):

74HC138真值表

如圖表下的注解所示:H—高電平,L—低電平,X—任意電平,G2(—)是代表G1A和G2B之和(其實看原理圖便知,G2A和G2B是一起控制的)。?

通過真值表,我們知道正確的控制方式為,G1給高電平,G2給低電平。于是,通過控制ABC三者輸入的值(二進制),控制Y0-Y7的輸出值(二進制)。?

例如,ABC = 000,Y0-Y7 = 0111 1111 ; ABC = 101,Y0~Y7 = 1111 1011。?

有一點請注意:?

前面說到,138譯碼器是提供8個互斥(Y0-Y7,8個腳互不影響)的低電平輸出,但是輸出來除了被ABC地址選中的那一個,其他的都是1,這是因為芯片內部的每個輸出端口前,都接有一個與非門,于是輸出端電平反相了。

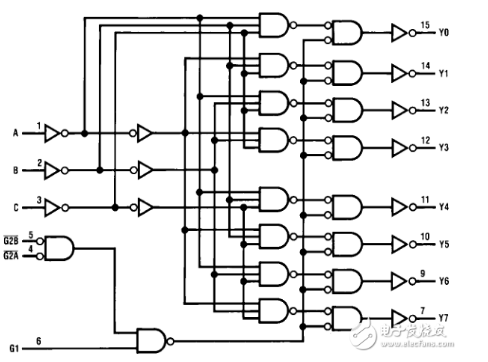

下面附上74HC138譯碼器的邏輯圖:?

在每一個輸出端口前面,可以看到都存在一個與非門電路(簡單的數電知識),我們可以在邏輯圖中對ABC賦值,再去查看Y0~Y7的輸出,再與真值表核對一下。

到此為止,可能已經能看出來,138譯碼器的功能之一了:如原理圖所示,使得P2.5P2.6P2.7三個引腳,控制了8個輸出!但是大家會問到,每次輸出都會是7個高電平,1個低電平。

74HC138的應用

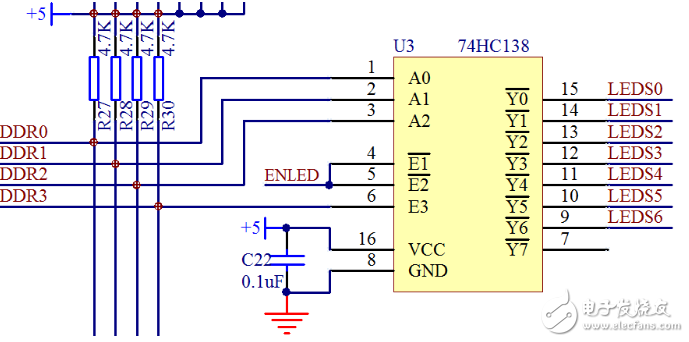

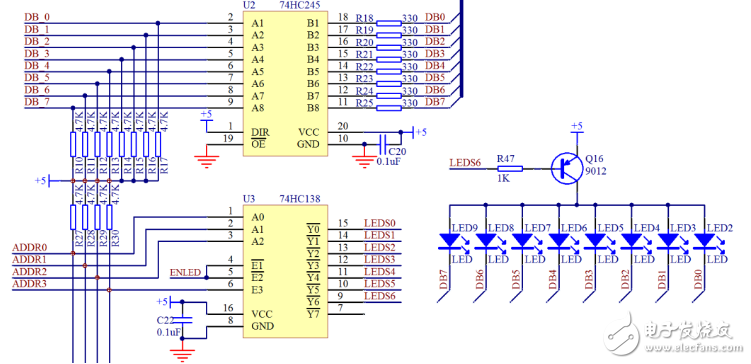

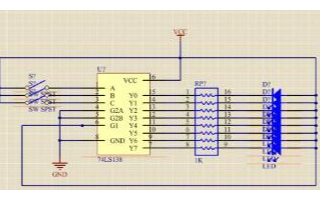

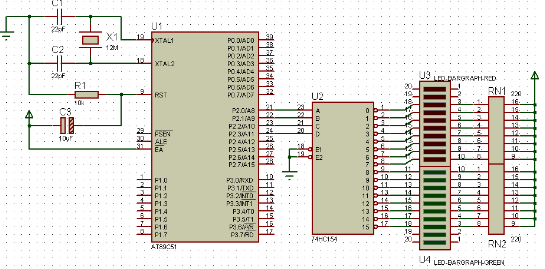

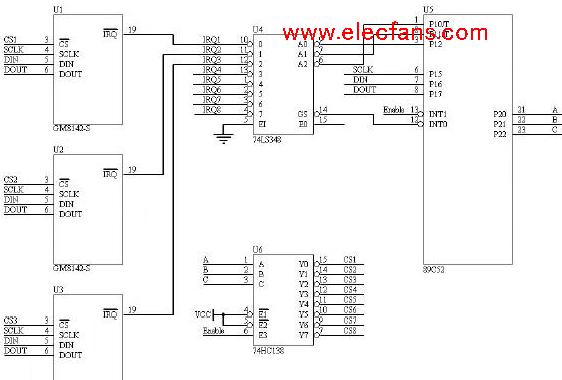

一般在單片機電路中,為了掌握更多的器件,就要運用一些核心的數字芯片,這種數字芯片由復雜的輸出邏輯來掌握輸入邏輯,比方 74HC138這個三八譯碼器,圖 3-15 是 74HC138 在我們道理圖上的一個使用。

74HC138應用原理圖

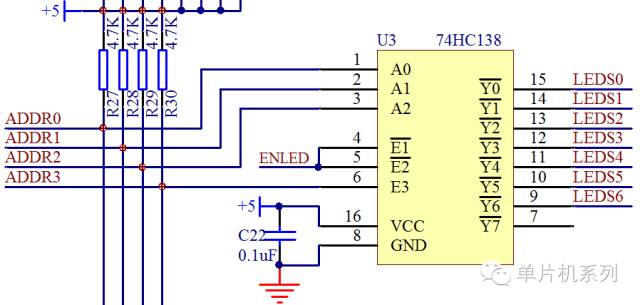

從這個名字來剖析,三八譯碼器,就是把 3 種輸出形態翻譯成 8 種輸入形態。從圖 3-15所能看出來的,74HC138 有 1~6 一共是 6 個輸出引腳,然則個中 4、5、6 這三個引腳是使能引腳。使能引腳和我們前邊講 74HC245 的 OE 引腳是一樣的,這三個引腳假如不契合規則的輸出請求,Y0 到 Y7 不論你輸出的 1、2、3 引腳是什么電平形態,老是高電平。所以我們要想讓這個 74HC138 正常任務,ENLED 誰人輸出地位必需輸出低電平,ADDR3 地位必需輸出高電平,這兩個地位多是使能掌握端口。不曉得人人能否記得我們第二課的程序有這么兩句 ENLED = 0;ADDR3 = 1;就是掌握使這個 74HC138 使能的。

這類邏輯芯片,大多多是有使能引腳的,使能契合請求了,那下面就要研討掌握邏輯了。關于數字器件的引腳,假如一個引腳輸出的時分,有 0 和 1 兩種形態;關于兩個引腳輸出的時分,就會有 00、01、10、11 這四種形態了,那么關于 3 個輸出的時分,就會呈現 8 種形態了,人人可以看下邊的這個真值表——圖 3-16,個中輸出是 A2、A1、A0 的次序,輸入是從Y0、Y1.。..。.Y7 的次序。

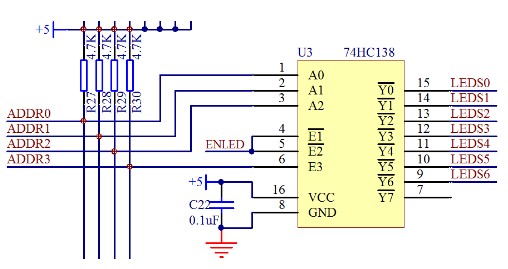

74HC138在任一輸出形態下,只要一個輸入引腳是低電平,其他的引腳多是高電平。在后面的電路中我們曾經看到,8 個 LED 小燈的總開關三極管 Q16 基極的掌握端是LEDS6,也就是 Y6 輸入一個低電平的時分,可以守舊三極管 Q16,從右側的愿望輸入的后果,我們可以推導出我們的 A2、A1、A0 的輸出形態應當是 110,如下圖:

那么我們再全體捋一遍點亮 LED 小燈的進程,起首看 74HC138,我們要讓 LEDS6 為低電平才干導通三極管 Q16,所以 ENLED = 0;ADDR3 = 1;包管 74HC138 使能。然后 ADDR2 =1; ADDR1 = 1; ADDR0 = 0;如許包管了三極管 Q16 這個開關守舊,5V 電源加到 LED 上。

而 74HC245 左側是經過 P0 口掌握,我們讓 P0.0 引腳等于 0,就是 DB_0 等于 0,而右側 DB0 等于 DB_0 的形態,也是 0,那么如許在這一排共 8 個 LED 小燈傍邊,只要最右側的小燈和 5V 之間有壓差,有壓差就會有電流暢過,有電流暢過我們的 LED2 就會發光了。

結語

關于74HC138的介紹就到這了,在本文中我們共同探討的譯碼器以及74HC138的介紹、原理功能分析,希望通過本文能讓你對74HC138有更好的認知,如有不足之處歡迎指正。

電子發燒友App

電子發燒友App

評論