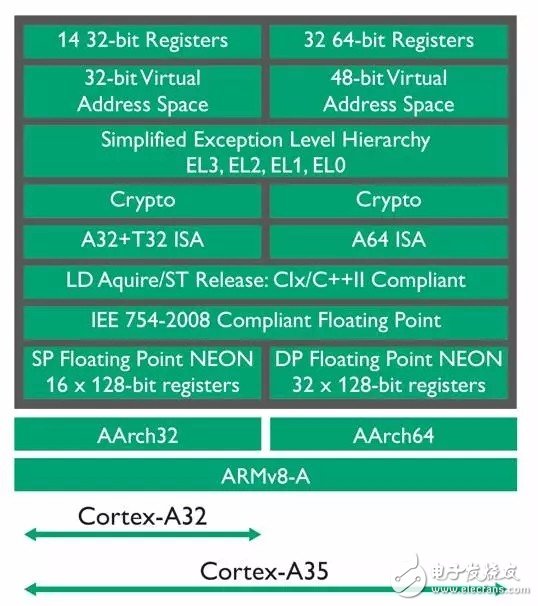

Cortex-A32是ARM架構中獨一無二的產品,擁有重要地位。Cortex-A32基于ARMv8-A架構,卻是針對32位設計的處理器。下圖介紹了Cortex-A32與ARMv8-A架構的匹配程度,并與Cortex-A35進行了對比。

圖一:Cortex-A32和ARMv8-A

基于上述,Cortex-A35可以實現兩種執行態,分別為32位AArch32及64位AArch64,從而充分發揮ARMv8-A架構的64位操作能力;相對比,Cortex-A32僅支持32位AArch32執行態,這一決定不僅進一步壓縮產品面積,對于不需要64位操作能力的用例,還可以帶來顯著的功耗優化。

無可否認,部分嵌入式應用可以從64位獲益,但許多其他應用都是32位的,將來很長一段時間市場也會依舊如此,Cortex-A32則專為這些應用程序量身打造。

AArch32執行態是早期Cortex-A處理器所用ARMv7-A架構的升級版。盡管不具備64位功能,但在其它某些功能卻得到顯著增強,使Cortex-A32與Cortex-A7和Cortex-A5相比更加高效;對基于更早ARM處理器的設計演變,或聚焦嵌入式市場的全新設計來說,都是理想的選擇。

對比ARMv7-A,AArch32在如下方面得到強化:

添加多項新指令,密碼函數性能提高;

全新的負載獲取及存儲釋放(Load Acquire and Store Release)指令,讓訪存排序更高效,與全新C++11訪存排序語義匹配;

額外的標量和單指令多數據結構(SIMD)浮點指令;

更豐富的系統控制指令。

對比早期的32位ARMv7-A處理器,Arrch32這些額外特性使其具備更佳的性能。

Cortex-A32總線接口上的高級一致性擴展(Advanced Coherency Extensions,ACE)使其可以利用Cortex-A32構建支持完全一致的多處理器系統,按需升級,以實現更高的性能。不過,如果產品面積與功耗是最主要的限制因素,Cortex-A32也提供專門針對單處理器應用優化的版本, 移除一致性邏輯,實現更高功效。

經過大物理地址擴展(Large Physical Address Extension,LPAE),Cortex-A32的可尋址內存空間得到擴展,超過Cortex-A5的32位(4GB),達到40位物理地址空間。

核心本身配置了額外的高級功能,進一步提高效率。其中包括更靈活的功耗管理、更優化的電源域和保留電源門控(retention power gating)的延伸使用。

ARMv7-M 主要特性

ARM Cortex-M處理器基于ARMv7-M架構(Cortex-M0和Cortex-M0+ 采用類似的ARMv6-M架構)。雖然與早期的ARM架構有眾多相似之處,但ARMv7-M經過專門打造,更適合深度嵌入、低成本的實時微處理器應用。因此,早期架構的很多功能被刪除,并添加了新的特性,以構建更符合“微控制器”環境的編程模式。

對比前代處理器(例如備受歡迎的ARM7TDMI),變化具體如下:

1.操作模式數量顯著減少,從7種甚至更多減至2種:僅保留處理器模式與線程模式。其中一種模式(處理器模式)可以默認為優先采用。

2.寄存器文件簡化。雖然編程器可用的寄存器數量實質上仍然是16個,但前代架構使用的分組寄存器機制明顯減少,因此兩種操作模式寄存的只有棧指針(r13)。是否使用寄存拷貝可自行設置。

3.異常模式的變化最為明顯。由于典型的微控制器應用可能會出現大量的芯片外設中斷,基于此,全新架構中的所有Cortex-M核心都配置了標準嵌套中斷向量控制器(Nested Vectored Interrupt Controller,NVIC)。類似的,根據記載處理器地址的向量表,異常處理模式也被標準化。上下文保存和恢復操作完全在硬件中實現,進一步簡化編寫中斷處理器的軟件任務。基于上述,實現過程中的干擾性延遲發生幾率被降到極低,且高度可預測。

4.與前代ARM處理器類似,ARMv7-M定義了可選內存保護架構。同時,因為裸金屬系統或在實時操作系統(RTOS)下運行的系統通常不需要虛擬內存,ARMv7-M并不為其提供支持。

5.為協助實時操作系統(RTOS)的實現和移植,一些標準的片上外圍設備也在架構中獲得定義,例如SysTick timer。

6.為進一步縮小處理器核心面積,ARMv7-M處理器僅采用Thumb指令集(包括Thumb-2指令集擴展)。

ARMv8-A AArch32 主要特性

Cortex-A處理器基于ARMv7-A或ARMv8-A架構。ARMv8-A處理器支持AArch32執行態,是32位ARMv7-A架構的兼容升級。這些架構的設計添加了專屬特性,比如虛擬內存環境,以支持包括Linux、Android、Windows等的平臺操作系統。

對比Cortex-M處理器核心,Cortex-A獨特之處包括:

1.擁有7種或更多操作模式:用戶、管理器、IRQ、FIQ、未定義、中止、系統。每種模式都可以處理一項具體事件,例如,IRQ模式被用于處理IRQ中斷。AArch32還支持另外兩種模式:Hyp 和監視器,這兩種模式分別用于虛擬化及ARM TrustZone。

2.雖然可以使用的寄存器數量同樣是16個,但AArch32有許多與上述操作模式相對應的“分組”(banked)寄存器。一旦進入特定操作模式,這些寄存器就會取代對應的用戶模式。這使異常處理的許多方面得到簡化,但也意味著需要提高機器管理能力,并在初始化上花更大的功夫。

3.異常模式有顯著差別,與最初的ARM架構設備一脈相承。具體來說,向量表是由一組可執行的指令組成,而不是地址,并且保存和恢復上下文的任務幾乎完全由編程器承擔。

4.還有一個重要差別是內存管理單元(Memory Management Unit ,MMU),內存管理單元會編譯核心提交的虛擬地址以及存儲系統需要的物理地址。針對Linux一樣的平臺操作系統所使用的完整需求分頁虛擬存儲器環境,Cortex-A也可以提供支持。

ARMv7-M 與 AArch32 的不同之處

從基于Cortex-M處理器的系統遷移到基于Cortex-A32處理器的系統時,許多新特性也有必要了解。盡管這兩種架構之間有許多相似之處(如寄存器組和指令集存在多種共性),但仍然需要清楚一點,ARMv8-A架構在AArch32執行態下的許多特性是基于早期架構的。本節將詳細介紹AArch32的特性,這些特性在ARMv7-M中不具備,或者實現方式極其不同。

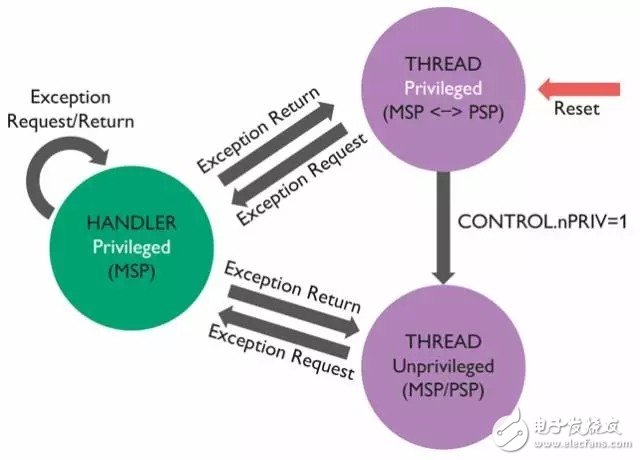

操作模式

如2圖所示,ARMv7-M僅定義兩種操作模式,線程模式與處理器模式。處理器模式可以設置為普通模式,也就是說,在不需要時,軟件可以不啟用該特性。處理器模式主要被用于處理異常情況,線性模式則用于用戶進程。模式間的轉化基本上是自動的,發生條件如圖所示。如異常情況發生,處理器模式自動啟用,異常處理完成后,處理器模式自動退出。SVCall指令是軟件進入處理器模式的主要方法(將啟動的IRQ設定為未決,可令處理器執行異常操作)。

圖2: ARMv7-M操作模式

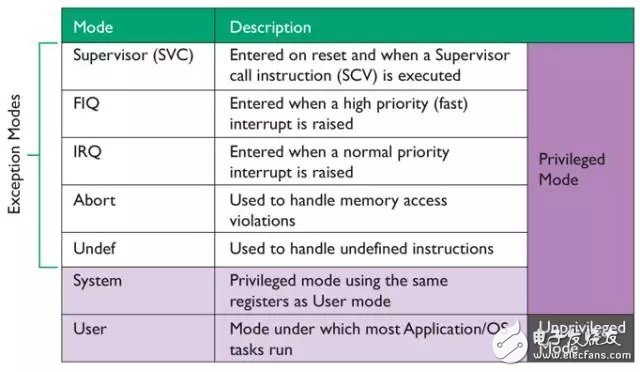

對比圖3,圖2顯示的是AArch32執行態下支持的操作模式。基本的操作模式有七種,其中五種用于處理特定異常。如發生快速中斷(Fast Interrupt,FIQ)異常,則會進入FIQ模式;如出現未定義指令,則進入Undef模式,諸如此類。

圖3: AArch32操作模式

模式間的轉換通常自動執行,但是如果在現程序狀態寄存器(Current Program Status Register,CPSR)中寫入模式字段,則可完全由軟件控制進行模式轉換,具體細節稍后再做說明。與SVCall指令類似,SVC指令可以支持軟件處理SVC異常,并進入SVC模式。

AArch32還支持其他兩種模式,但未在圖中顯示(僅為節省版面空間)。它們分別是Hyp模式(用于管理程序)和監控模式(用于TrustZone)。

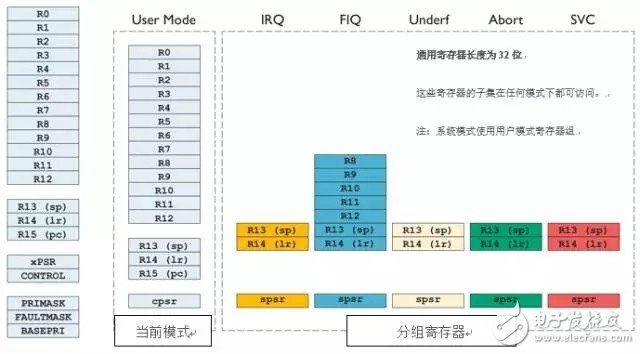

寄存器組

圖4及圖5分別介紹了ARMv7-M 和 AArch32寄存器組。從圖中可以看出,兩種寄存器有許多相似之處,這是因為兩者皆承襲了ARMv6及早期架構的共同特性。

多數指令可以訪問13個通用寄存器(r0至r12)。兩種架構下,r13預設為棧指針(SP),r14預設為連接寄存器(LR),r15預設為程序計數器(PC)。ARMv7-M架構下,訪問專用寄存器受到嚴格限制;AArch32下,可以用與其他通用寄存器相同的方式訪問這些寄存器;不過無需多言,擅自修改PC值可能會產生不良后果!

圖4:ARMv7-M寄存器組 圖5- AArch32寄存器組

ARMv7-M是一小組其他專用寄存器,包括PRIMASK、FAULTMASK、xPSR、CONTROL及BASEPRI,用于控制、配置處理器及處理異常情況。

指令集

如圖5所示,AArch32還有一些與特定操作模式相關的寄存器。如進入對應的模式下,這些寄存器會與相應的用戶模式切換。只有極少數特殊指令能夠訪問,并且還無法直接訪問。這些數值隨著模式變化被保存,以輔助異常處理。特別值得指出的是,每種異常模式都對應獨立的棧指針,從而能夠在單獨堆棧上解決每個異常狀況。這就讓異常處理程序更可靠、防御性更強。異常出現后,相關模式的連接寄存器會被設定為異常返回地址。

每種異常模式都對應一個附加寄存器,即程序保護狀態寄存器(SPSR)。程序保護狀態寄存器用于出現異常時及時記錄當前的程序狀態寄存器數值以及LR,從而自動保存相關數據。另外,AArch32的圖示中未顯示Mon與Hyp模式。與其他模式一樣,它們分別支持R13與R14分組寄存器。

Cortex-A架構下,有一個與ARM NEON SIMD指令集相關的獨立寄存器組,包含32個128位寬寄存器。每個寄存器都可作為單字、雙字或四倍字尋址,NEON指令集也支持依據字節或四倍字進行向量運算。

異常模型

上述兩個架構的異常模型具有顯著差異,但兩者都支持因系統事件或外圍中斷引起的內部及外部異常。

ARMv7-M支持與傳統微控制器上發現的異常更相近的模型,所有外部中斷都通過含有處理器地址的向量表單獨進行向量處理。

AArch32與早期ARM架構中的異常模型更相近,早期的ARM架構中僅有8種異常類型,向量也各不相同。向量表由可執行指令組成,通常是特定異常處理器的分支指令。僅支持兩種外部中斷源,即FIQ和IRQ。通常,一個高優先級中斷會連接FIQ,其他則連接IRQ。這意味著系統要么裝有軟件調度程序,要么就要和現代系統一樣裝有中斷向量控制器(Vectored Interrupt Controller,VIC),可以利用單一向量地址進行編程。

多數Cortex-A系統裝有基于ARM的通用中斷控制器(Generic Interrupt Controller,GIC)。GIC是許多物理中斷和ARM核心中斷輸入(FIQ和IRQ)的接口,處理優先次序、遮蔽、單一中斷啟用或禁止,及優先權。欲了解更多信息,請參考《GIC架構參考手冊》。

虛擬內存支持

支持完全虛擬內存環境是ARMv8-A的一個主要特性,使設備可以支持Linux和Android等平臺操作系統。同樣,虛擬內存能力通常也是客戶選擇核心的重要依據。

虛擬內存環境使操作系統能夠以更加靈活的方式管理內存,例如,允許單獨處理動態擴展棧區域,按照需求將單個代碼和數據區域調入和調出外部存儲頁面,并使每個用戶處理系統內存映射的相同視圖。

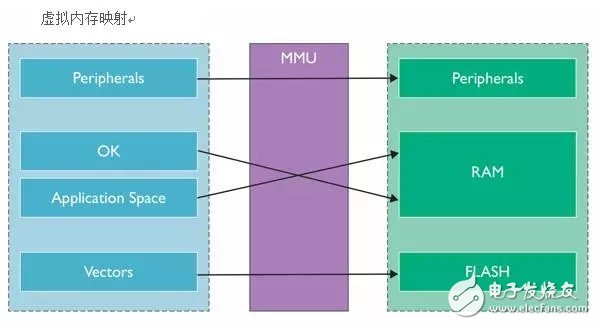

圖6:虛擬內存

為此,如圖6所示,虛擬內存在處理器提供的每個地址上進行“轉換”。軟件在“虛擬地址空間”和稱為內存管理單元(Memory Management Unit,MMU)的模塊中運行,并將其轉換為“物理地址空間”,為系統中的每個用戶任務以及操作系統本身創建新的虛擬內存映射,還使操作系統完全控制訪問權限等。每項任務都可以在自身的虛擬內存空間中執行,就像是系統中的唯一任務。只有操作系統知道外部物理內存中該任務的代碼和數據區域的真實物理位置。

任務切換時,操作系統的其中一項工作就是重新配置MMU,使代碼和數據能被輸入任務使用,同時讓輸出任務的存儲器可以暫時訪問。這進一步增強了任務之間的分離,構建安全可靠的系統。

這里我們不再深入研究所有細節。簡而言之,ARM處理器的MMU使用了“頁面表”(外部存儲器中)的數據,驅動并控制轉換。系統已經經過一系列優化(如轉換查找緩沖器(TLBs),緩存通過轉換降低讀取頁面表的功耗),讓轉換過程的功耗降到最低。

電子發燒友App

電子發燒友App

評論