利用FPGA實現雙口RAM的設計及應用

概述:為了在高速采集時不丟失數據,在數據采集系統和

2010-04-16 14:08:36 11323

11323

1. 初識XILINX 初識XILINX,是PYNQ-Z2。當時剛學完學校的數字電路課程,對FPGA并不了解,學校課程也僅僅是用VHDL驗證了一些基礎的FPGA實驗,例如生成一個n進位序列

2020-11-05 15:56:42 4204

4204 即是相應的 HDL 程序以及最新非常流行的基于高層次綜合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。 (1)選擇FPGA(SoC)的若干理由 a)FPGA

2020-12-17 12:58:21 4094

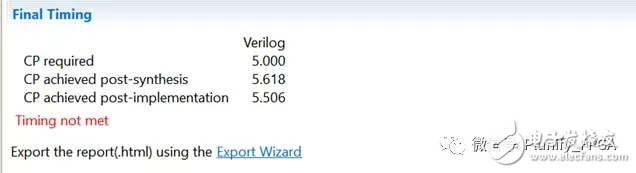

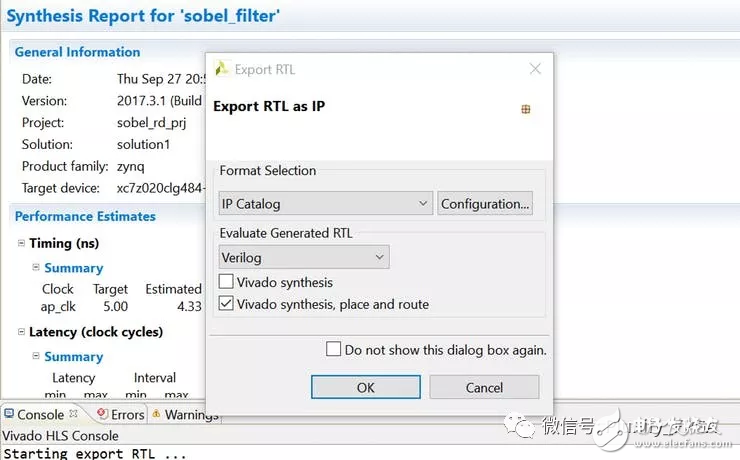

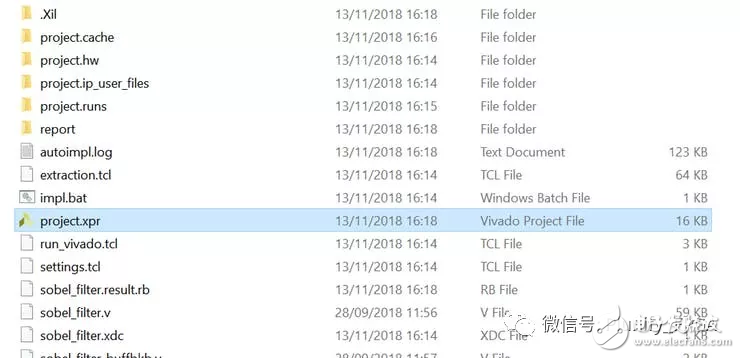

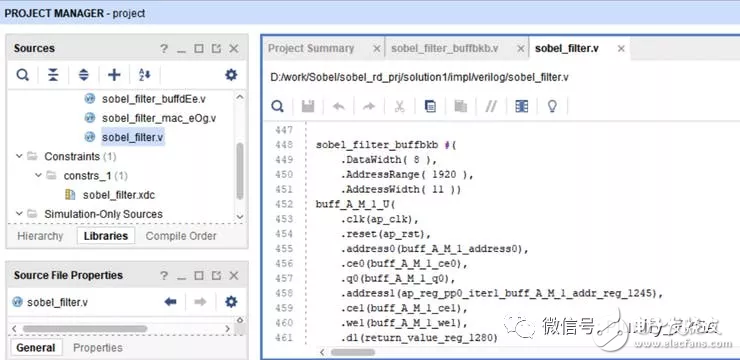

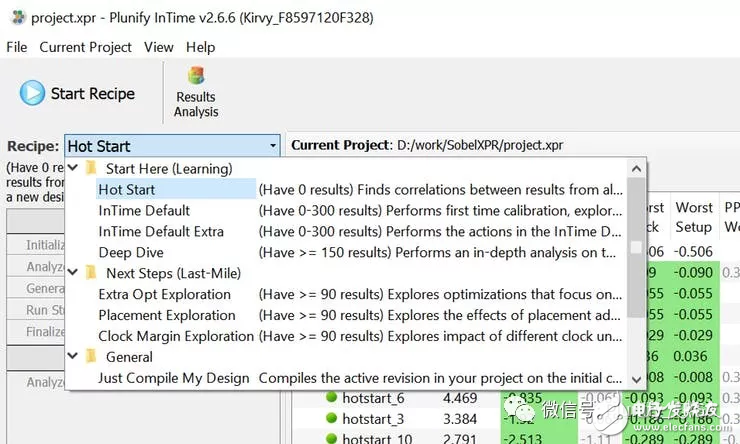

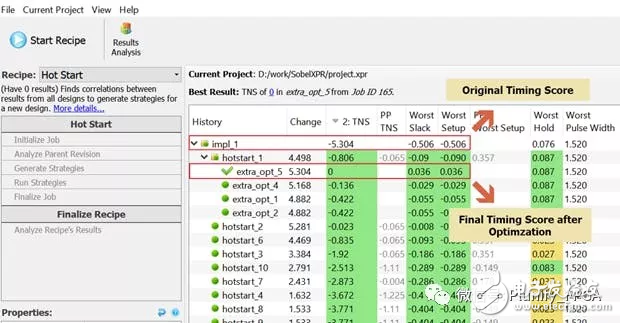

4094 InTime。 前言 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復雜的 FPGA 設計上實現高性能,往往需要手動優化 RTL 代碼,這也意味著從 C 轉化得到 RTL 基本不可能。其實,使用 FPGA 工具設置來優化設計可以最

2020-12-20 11:46:46 1416

1416

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

2023-10-30 11:41:01 349

349

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

2023-10-30 14:34:36 564

564

嗨,我是FPGA和FPGA的新手。 HDL(Verilog)也是這里的新論壇。剛從Pargue(捷克共和國)發布我的Hello我希望編譯位文件作為練習(由Wirth ETH Zurig大學教授

2020-05-20 15:35:37

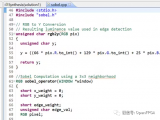

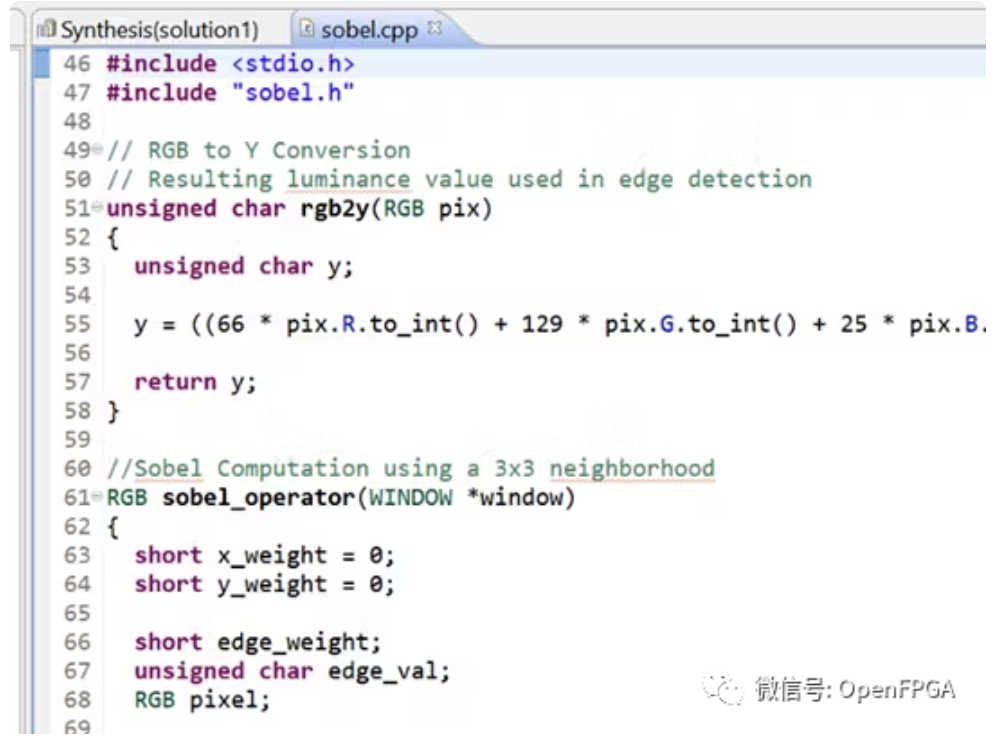

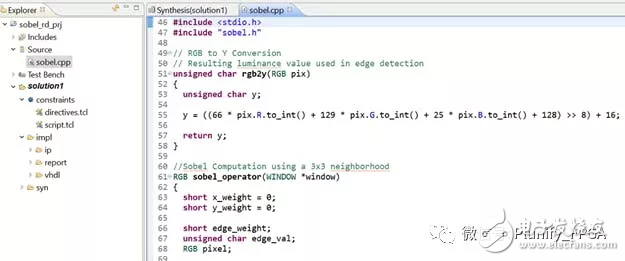

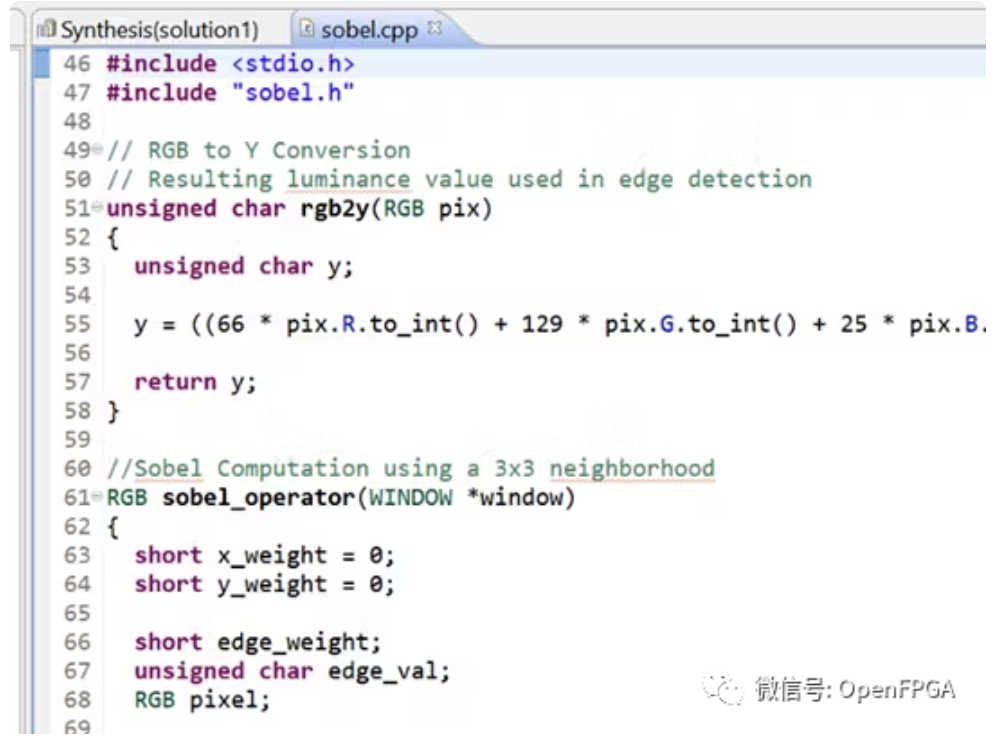

(HLS) 的幫助下,基于 C 語言的語言現在可用于 FPGA 設計。具體來說,AMD Vivado? HLS 編譯器提供的編程環境能夠與標準處理器及專用處理器共享關鍵技術,用于優化 C 語言程序

2023-06-28 18:18:57

。DSP 和 RAM 推論優化當今的高級 FPGA 器件除常規邏輯模塊外還包含 DSP 和 RAM嵌入式模塊。這樣一來,合成工具可了解各種 RTL 編碼樣式,將其映射到適當的 DSP或 RAM 模塊,從而

2018-09-20 11:11:16

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真

2021-07-23 09:12:07

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

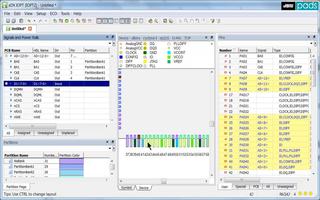

使用 HDL 語言進行 FPGA 開發需要專用的 FPGA 工具軟件,它們的功能包括 FPGA 程序的編寫、綜合、仿真以及下載等。就整體來說,目前的 FPGA 工具軟件大概可以分為兩類:? 一類是由

2018-09-27 09:17:44

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

第二章 FPGA 開發流程FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

工作原理及其使用;對比手工編寫代碼與利用IP快速進行設計的異同;第五階段 常系數復雜FIR濾波器的設計; 使用基于IP核的設計方法和流程,針對速度、面積、和功耗的優化; 使用EDA工具針對各個綜合階段

2012-09-13 20:07:24

FPGA 設計優化主要分為編碼風格、設計規劃和時序收斂三大部分,這 些因素直接決定了 FPGA 設計的成敗。 編碼風格直接影響 FPGA 設計的實現并最終影響設計的性能。盡管綜合 工具集成

2022-09-29 06:12:02

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優化策略基于VHDL的FPGA系統行為級設計

2021-04-15 06:33:58

`FPGA面積優化1.對于速度要求不是很高的情況下,我們可以把流水線設計成迭代的形式,從而重復利用FPGA功能相同的資源。2.對于控制邏輯小于共享邏輯時,控制邏輯資源可以用來復用,例如FIR濾波器

2014-12-04 13:52:40

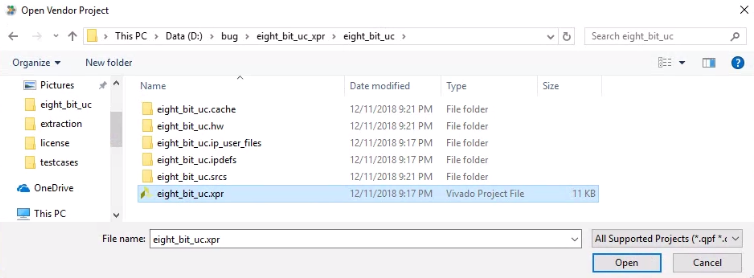

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

所有可能的數據通信方式-沒有功能概述,也沒有對用戶代碼進行優化轉換-支持代碼報告得太晚了-在某些情況下,工具的高效實施是不可能的,例如當必須將太多的加速器映射到硬件部分時。HLS工具無法預先檢測

2021-07-10 08:00:00

描述TIDA-01051 參考設計用于演示極高通道數數據采集 (DAQ) 系統(如用在自動測試設備 (ATE) 中的系統)經過優化的通道密度、集成、功耗、時鐘分配和信號鏈性能。利用串行器(如 TI

2018-10-29 09:47:41

BOARD EVAL FPGA BLACKFIN EXTENDR

2023-03-30 12:06:40

MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA TOOL W/MANUAL

2023-04-06 11:27:29

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

有關。 FPGA Compiler II是一個完善的FPGA邏輯分析、綜合和優化工具,它從HDL形式未

2010-01-30 11:22:22

所有可能的數據通信方式-沒有功能概述,也沒有對用戶代碼進行優化轉換-支持代碼報告得太晚了-在某些情況下,工具的高效實施是不可能的,例如當必須將太多的加速器映射到硬件部分時。HLS工具無法預先檢測

2021-07-06 08:00:00

主要可以從“設計的重用”和“抽象層級的提升”這兩個方面來考慮。Xilinx推出的Vivado HLS工具可以直接使用C、C++或System C來對Xilinx系列的FPGA進行編程,從而提高抽象的層級

2020-10-10 16:44:42

)對正點原子FPGA感興趣的同學可以加群討論:8767449005)關注正點原子公眾號,獲取最新資料第四章呼吸燈實驗在前面兩個實驗中我們學習了如何通過Vivado HLS工具來生成帶有一個

2020-10-10 17:01:29

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰。為什么要設計優化FPGA功耗?

2019-08-08 07:39:45

表),并根據約束條件優化生成的邏輯連接,輸出edf和edn等文件。4)實現實現可理解為利用實現工具把邏輯映射到目標器件結構的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能連接的布線通道進行連線,并

2021-05-27 09:28:40

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis

2022-09-09 16:45:27

`再談設計工具FPGA的優勢FPGA最大的優勢特點就是能夠縮短開發所需時間。 換句話說,通過使用FPGA,設計人員可以有效地利用每一分鐘進行開發。例如,在開發過程中使用FPGA與否,可以導致開發時間

2012-02-24 17:26:23

語言進行CPLD/FPGA設計開發,Altera和Lattice已經在開發軟件方面提供了基于本公司芯片的強大開發工具。但由于VHDL設計是行為級設計,所帶來的問題是設計者的設計思想與電路結構相脫節,而且

2019-06-18 07:45:03

FPGA的HLS案例開發|基于Kintex-7、Zynq-7045_7100開發板前 言本文主要介紹HLS案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

相比,能夠為通信和多媒體應用提供高達10倍速的更高的設計和驗證能力。Synphony HLS為ASIC 和 FPGA的應用、架構和快速原型生成最優化的RTL。Synphony HLS解決方案架構圖

2019-08-13 08:21:49

用于Xilinx FPGA的Keysight E5910A串行鏈路優化工具

2019-10-16 10:49:30

如何利用模擬工具優化電路設計?如何利用專用仿真器解決RF電路問題? 使用模擬工具有哪些好處?

2021-04-13 06:40:30

進行編譯的。本文僅驗證了采用高級語言開發FPGA的可行性,還有很多優化工作待完善,僅以此文為大家提供一個新的視角,為軟件開發人員利用FPGA進行算法加速做前期調研,歡迎感興趣的同事共同交流。

2017-09-25 10:06:29

FPGA怎么選擇?針對功耗和I/O而優化的FPGA介紹

2021-05-06 09:20:34

Altera公司用FPGA做DSP算法的工具

2006-03-25 13:46:45 39

39 概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎的函數庫以及常用的控制函數模塊,配合

2022-05-19 09:16:05

。EasyGo FPGA Solver 的優點在于,能夠將Simulink的圖形化模型利用解算器軟件轉化成FPGA執行的代碼,而不需要進行FPGA的編譯

2022-05-19 09:21:43

FPGA調試工具chipscope,學習與使用FPGA必用的工具。。

2009-03-23 09:45:00 86

86 基于多種EDA工具的FPGA設計

介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實

2009-05-14 18:38:38 854

854

摘 要:在FPGA開發的各個階段,市場為我們提供了很多優秀的EDA工具。面對眼花繚亂的EDA工具,如何充分利用各種工具的特點,并規劃好各種工具的協同使用,對FPGA

2009-06-20 10:51:14 692

692 摘要:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實際操作介紹了

2009-06-20 11:42:45 522

522

FPGA設計工具淺談

作為一個負責FPGA企業市場營銷團隊工作的人,我不得不說,由于在工藝技術方面的顯著成就以及硅芯片設計領

2009-10-10 07:46:04 429

429 多種EDA工具的FPGA設計方案

概述:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配

2010-05-25 17:56:59 670

670

Mentor Graphics的FPGA Advantage是享譽業界,具有FPGA設計黃金組合的全流程設計工具。本次課程將使用戶體驗FPGA Advantage如何最大化地加速設計的實現以及復用。同時掌握如何利用FPGA Advantage快速實現設計從創建、理解、仿真驗證、綜合以及布局布線的全過

2011-03-15 13:39:56 97

97 自從Xilinx推出FPGA二十多年來,研發工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實現數字電路的優選平臺。今天,功耗日益成為FPGA供應商及其客戶關注的問題。降低FPGA功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移

2011-03-15 14:58:34 31

31 基于FPGA的SM3算法優化設計與實現的論文

2015-10-29 17:16:51 4

4 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 高級FPGA設計 結構、實現和優化,適合于FPGA的進階學習。

2016-05-11 16:40:55 15

15 高級FPGA設計 結構、實現和優化,適合于學習FPGA的進階學習。

2016-05-11 16:40:55 14

14 FPGA學習資料教程之Xilinx-FPGA高級開發工具,感興趣的可以看看。

2016-09-01 15:27:27 0

0 利用FPGA實現信號處理算法是一個難度頗高的應用,不僅涉及到對信號處理算法、FPGA芯片和開發工具的學習,還意味著要改變傳統利用軟件在DSP上實現算法的習慣,從面向硬件實現的算法設計、硬件實現、結構優化和算法驗證等多個方面進行深入學習。

2016-12-26 17:26:41 12

12 基于FPGA的可堆疊存儲陣列設計與優化

2017-01-07 21:28:58 0

0 基于FPGA的高速固態存儲器優化設計_楊玉華

2017-01-13 21:40:36 1

1 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2017-02-09 01:59:11 264

264 參加 ?FPGA? 功率優化班,將幫助您創建更高電源效率的 ?FPGA? 設計。通過本課程的學習,將有助于您的設計滿足更小型化的 ?FPGA? 器件,降低 ?FPGA? 功耗,或在更低的溫度下運行

2017-02-09 06:24:11 167

167 Luke Miller并非一開始就是HLS(高層次綜合)的倡導者。在使用早期的工具版本的時候,他似乎有過一些糟糕的經歷。

2017-02-10 18:48:59 3333

3333

資源、速度和功耗是FPGA設計中的三大關鍵因素。隨著工藝水平的發展和系統性能的提升,低功耗成為一些產品的目標之一。功耗也隨之受到越來越多的系統工程師和FPGA工程師的關注。Xilinx新一代開發工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優化。

2017-11-18 03:11:50 4873

4873 現有的工具和技術可幫助您有效地實現時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現工具為滿足時序要求而優化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2951

2951 通常基于傳統處理器的C是串行執行,本文介紹Xilinx Vivado-HLS基于FPGA與傳統處理器對C編譯比較,差別。對傳統軟件工程師看來C是串行執行,本文將有助于軟件工程師理解

2017-11-18 12:23:09 2377

2377

1. FPGA 開發流程: 電路設計與設計輸入 ;仿真驗證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 9999

9999 HLS,高層綜合)。這個工具直接使用C、C++或SystemC 開發的高層描述來綜合數字硬件,這樣就不再需要人工做出用于硬件的設計,像是VHDL 或Verilog 這樣的文件,而是由HLS 工具來做這個事情。

2018-06-04 01:43:00 7171

7171

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS為FPGA流程提供集成化設計與開發環境,率先支持5G無線應用。

2018-08-30 10:09:32 7366

7366 作為集成電路設計領域現場可編程門陣列 (FPGA) 技術的創造者之一,賽靈思一直積極推廣高層次綜合 (HLS) 技術,通過這種能夠解讀所需行為的自動化設計流程打造出可實現此類行為的硬件。賽靈思剛剛推出了一本專著,清晰介紹了如何使用 HLS 技術來創建優化的硬件設計。

2018-11-10 11:01:05 2750

2750 了解如何利用Xilinx成本優化的FPGA和SoC產品組合的最新增強功能。

2018-11-28 06:20:00 2086

2086 用軟件從 C 轉化來的 RTL 代碼其實并不好理解。今天我們就來談談,如何在不改變 RTL 代碼的情況下,提升設計性能。 本項目所需應用與工具:賽靈思HLS、Plunify Cloud 以及 InTime。 前言 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。

2019-09-15 11:56:00 265

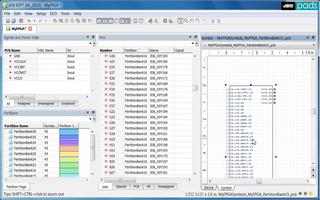

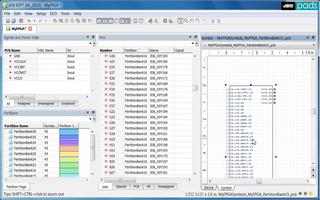

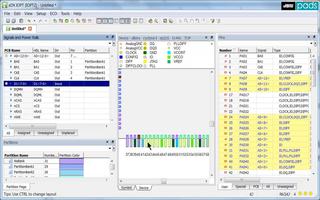

265 FPGA I/O 優化功能提供了自動化 FPGA 符號生成流程,該流程與原理圖設計和 PCB 設計相集成,可節省大量創建 PCB 設計的時間,同時提高原理圖符號的總體質量和準確性。

2019-05-20 06:16:00 2844

2844

與 FPGA 軟件工具進行自動雙向信息交換可提供由供應商規則驅動的“設計即正確”的 I/O 分配,從而實現快速、無誤的優化流程。其包括了最新的器件支持,并且可提前訪問尚未發布的 FPGA 供應商器件。

2019-05-16 06:13:00 3380

3380

介紹了如何利用Vivado HLS生成FIR濾波算法的HDL代碼,并將代碼添加到ISE工程中,經過綜合實現布局布線等操作后生成FPGA配置文件,下載到FPGA開發板中,Darren采用的目標板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 接著開始正文。據觀察,HLS的發展呈現愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 6232

6232

自動化和雙向信息交換與FPGA軟件工具提供了一個correct-by-construction供應商)I / O分配導致快速和錯誤免費優化過程。包括最新的設備支持和早期的拉菲FPGA供應商設備的訪問。

2019-10-16 07:00:00 2387

2387 討論了利用FPGA工具實現MBUS總線的原理、方法,以實際操作介紹了FPGA設計流程,并給出FPGA常用設計技巧。

2019-12-24 14:54:08 9

9 教程介紹 本教程旨在指導用戶通過 Plunify Cloud 的云服務器,來使用 InTime 軟件優化 FPGA 設計。如果您首次使用 InTime,請免費 申請該軟件的本地試用 。 本教程涵蓋

2020-12-21 17:57:01 1227

1227

本文檔的主要內容詳細介紹的是FPGA JTAG工具設計的教程說明。

2020-12-31 17:30:55 18

18 1.項目需求 FPGA :V7-690T兩片 Resource:兩片FPGA通過X12 gth互聯;每片FPGA使用48路serdes走光口與板外連接;每片FPGA使用SIROx4通過VPX與外界

2021-01-07 10:15:31 4645

4645

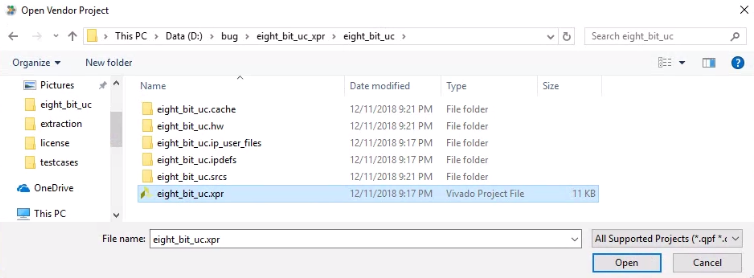

HLS的FPGA開發方法是只抽象出可以在C/C++環境中輕松表達的應用部分。通過使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

電子發燒友網站提供《ThunderGP:基于HLS的FPGA圖形處理框架.zip》資料免費下載

2022-10-27 16:49:59 0

0 中來實現,無縫的將硬件仿真環境集合在一起,使用軟件為中心的工具、報告以及優化設計,很容易的在 FPGA 傳統的設計工具中生成 IP。 傳統的 FPGA 開發,首先寫 HDL 代碼,然后做行為仿真,最后做綜合

2022-12-02 12:30:02 2570

2570 對于FPGA來說,設計人員可以充分利用其可編程能力以及相關的工具來準確估算功耗,然后再通過優化技術來使FPGA和相應的硬件設計滿足其功耗方面的要求。

2022-12-29 14:46:14 928

928 HLS ?(high-level synthesis)稱為高級綜合, 它的主要功能是用 C/C++為 FPGA開發 算法。這將提升FPGA 算法開發的生產力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件描述語言)是兩種最常用的數字

2023-03-21 10:26:50 2622

2622 AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕松創建復雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統一軟件平臺(用于所有異構系統設計和應用)高度集成。

2023-04-23 10:41:01 652

652

電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 1

1 本篇博客介紹 VVAS 框架所支持調用的 H/W(HLS) 內核。 H/W 內核指的是使用 HLS 工具生成的在 FPGA 部分執行的硬件功能模塊。

2023-08-04 11:00:43 335

335

電子發燒友網站提供《基于FPGA的神經振蕩器設計及優化.pdf》資料免費下載

2023-11-10 09:39:29 0

0 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0

電子發燒友App

電子發燒友App

評論