浪潮聯(lián)合賽靈思宣布推出全球首款集成HBM2高速緩存的FPGA AI加速卡F37X,可在不到75W典型應(yīng)用功耗提供28.1TOPS的INT8計(jì)算性能和460GB/s的超高數(shù)據(jù)帶寬。

2018-10-16 18:50:24 1915

1915 為了幫助大家解決FPGA開(kāi)發(fā)中碰到的相關(guān)問(wèn)題,電子發(fā)燒友網(wǎng)和FPGA資深工程師吳厚航(網(wǎng)名“特權(quán)同學(xué)”)進(jìn)行了深入的交談,希望能為工程師群體在電子設(shè)計(jì)道路上提供參考。

2013-08-20 14:31:45 5641

5641 2018年10月16日, 中國(guó)北京 (賽靈思開(kāi)發(fā)者論壇) –今日, 華為在賽靈思開(kāi)發(fā)者論壇( XDF)上與賽靈思聯(lián)合發(fā)布了FX系列FPGA加速卡,為基因測(cè)序、視頻編碼、圖片處理、數(shù)據(jù)壓縮等業(yè)務(wù)提供

2018-10-17 13:42:02 3892

3892 跪求兩位數(shù)累加顯示函數(shù)代碼謝謝

2017-01-12 16:29:46

FPGA 中的Block Diagram能直接聯(lián)合Modelsim仿真嗎?如果不使用Block Diagram,是能夠正常聯(lián)合Modelsim仿真的,但是使用了Block Diagram模式后,配置一樣,但是總是報(bào)錯(cuò)

2016-10-08 17:12:26

CPU降低20倍,FPGA處理性能是CPU機(jī)器的6倍,驗(yàn)證了FPGA能進(jìn)行計(jì)算加速的能力,同時(shí)也增強(qiáng)了FPGA聯(lián)合團(tuán)隊(duì)的自信心。(圖1)圖片轉(zhuǎn)碼中FPGA和CPU延時(shí)對(duì)比(圖2)圖片轉(zhuǎn)碼中FPGA和CPU

2017-04-15 16:17:41

`急急急!兩位一體共陽(yáng)極數(shù)碼管顯示驅(qū)動(dòng)代碼表是什么?`

2013-01-12 23:50:06

小弟現(xiàn)在想做一個(gè)利用51單片機(jī)(at89s52)做一個(gè)倒計(jì)時(shí)定時(shí)器,為節(jié)約io口,我想采用兩位一體數(shù)碼管(十腳),還希望通過(guò)按鍵設(shè)定初始值,不知道電路如何設(shè)計(jì),程序這么寫(xiě),望各位大俠伸出援助之手,小弟不勝感激。。。

2011-08-05 16:25:47

我現(xiàn)在是讓他先亮2,然后把2滅掉。再亮1,1滅掉。再亮2,如此循環(huán)。。。雖然看上去數(shù)碼管一直都是顯示21。但是總感覺(jué)有點(diǎn)怪怪的。所以就來(lái)問(wèn)一下論壇的大神。兩位數(shù)碼管顯示兩個(gè)相同的數(shù)字還是理解的,但是

2020-05-26 16:03:00

哪位朋友有兩位共陰數(shù)碼管封裝圖,我下載了很多封裝圖庫(kù)但都是一位或四位的,求資源,謝謝

2017-01-09 11:27:20

程序想實(shí)現(xiàn)兩位共陰數(shù)碼管顯示兩位數(shù)值,數(shù)值設(shè)定大于50時(shí)候,蜂鳴器響的頻率比較快,數(shù)值設(shè)定不大于50時(shí)候,蜂鳴器響的頻率比較慢。蜂鳴器和數(shù)碼管單獨(dú)程序的時(shí)候都是正常,但是兩個(gè)程序工作的時(shí)候,蜂鳴器

2016-07-05 22:59:11

各位大神有兩位半數(shù)碼管的顯示程序嗎?套用函數(shù)那種,我寫(xiě)的就是一個(gè)個(gè)列出來(lái)的那種,太長(zhǎng)了。。。所以想優(yōu)化一下,拜托,嘿嘿嘿(抱拳)

2017-07-17 15:28:44

你好,xilinx工程師2位文件可以一起下載到FPGA嗎?這樣做的目的是使用FMC板上的GTX。我希望將KC705的晶振時(shí)鐘映射為FMC子板的refclk。所以我有2位文件:一個(gè)是IBERT,另一個(gè)

2019-04-10 10:44:04

ARM微處理器中支持字節(jié)、半字、字三種數(shù)據(jù)類(lèi)型,其中,字需要4字節(jié)對(duì)齊(地址的低兩位為0)、半字需要2字節(jié)對(duì)齊(地址的最低位為0)。我想問(wèn)的是括號(hào)中的內(nèi)容是什么意思呢?請(qǐng)牛人幫忙解釋一下!謝謝

2022-11-03 15:23:57

BURKERT伺服輔助兩位兩通隔膜閥00138962現(xiàn)貨促銷(xiāo)德國(guó)寶德BURKERT伺服輔助2/2路隔膜閥媒體分開(kāi)降低功耗不銹鋼外殼,適用于腐蝕性介質(zhì)電路功能NC或NO輸入2516上海就瑞機(jī)械設(shè)備

2018-07-24 18:44:09

協(xié)議要求pid包有4位進(jìn)行區(qū)分,但是ch 554作為從設(shè)備只能有兩位pid識(shí)別碼,如何區(qū)分?是數(shù)據(jù),還是令牌?CH554 作為設(shè)備時(shí),pid只有兩位,bUIS_TOKEN1 和 bUIS_TOKEN0,如何區(qū)分令牌包是數(shù)據(jù)還是其他?

2022-06-13 07:16:26

Debussy 能和64位的modelsim聯(lián)合嗎?

2017-09-19 20:31:35

USB 芯片和軟件廠商飛特蒂亞(FTDI)公司發(fā)布一款靈活而強(qiáng)大的開(kāi)發(fā)平臺(tái) Morph-IC-II,可加速基于FPGA的應(yīng)用與制作,并簡(jiǎn)化先進(jìn)邏輯電路設(shè)計(jì)中整合高速480Mbit/s USB通訊作業(yè)

2019-07-03 08:29:05

錯(cuò)誤、兩位錯(cuò)誤和其他錯(cuò)誤。請(qǐng)參閱下面的屏幕截圖。 然而,當(dāng)我在自定義 PCB 中將相同的參數(shù)值更改為更高的值時(shí),我沒(méi)有得到任何一位和兩位錯(cuò)誤。請(qǐng)參閱下面的屏幕截圖; 如果我將此參數(shù)設(shè)置為必須的值,那么

2023-04-18 07:07:16

Numatic兩位五通電磁閥維修與保養(yǎng)NUMATICS電磁閥閥門(mén)使用維修與保養(yǎng): 1.每周檢查一次閥門(mén)關(guān)閉時(shí)的密封性能,即用手摸、耳聽(tīng)感覺(jué)判定閥門(mén)密封效果,發(fā)現(xiàn)問(wèn)題及時(shí)報(bào)告處理;上海就瑞機(jī)械設(shè)備

2018-07-01 17:02:54

各位大神求指導(dǎo), S3C2410AGPB端口低兩位與次低兩位兩個(gè)反邏輯LED指示燈的交替閃爍,這個(gè)當(dāng)初沒(méi)好好學(xué),求指導(dǎo)

2023-11-14 20:22:42

iMPACT下載界面,將本實(shí)例工程下的sp6.bit文件燒錄到FPGA中在線運(yùn)行。確保P10的PIN2和PIN3用跳線帽短接。此時(shí)當(dāng)我們使用導(dǎo)航按鍵進(jìn)行DA輸出數(shù)據(jù)設(shè)定,則相應(yīng)的高兩位和低兩位數(shù)碼管都會(huì)發(fā)生變化,而且基本是一致的。這說(shuō)明AD和DA芯片都能正常的工作。 `

2016-05-30 08:23:06

`作者從2009年1月起,在《電子世界》雜志上連載了《手把手教你學(xué)CPLD/FPGA設(shè)計(jì)》講座。《手把手教你學(xué)CPLD/FPGA與單片機(jī)聯(lián)合設(shè)計(jì)》以此為藍(lán)本,另外增加了大量的篇幅與實(shí)驗(yàn)例子進(jìn)行充實(shí)

2015-01-06 17:21:59

作者從2009年1月起,在《電子世界》雜志上連載了《手把手教你學(xué)CPLD/FPGA設(shè)計(jì)》講座。《手把手教你學(xué)CPLD/FPGA與單片機(jī)聯(lián)合設(shè)計(jì)》以此為藍(lán)本,另外增加了大量的篇幅與實(shí)驗(yàn)例子進(jìn)行充實(shí)

2014-12-29 17:10:05

去形容了。本文Andrew不僅僅對(duì)FPGA入門(mén)學(xué)習(xí)流程做了詳細(xì)的分享,更是對(duì)FPGA開(kāi)發(fā)工作的要求分成大公司和小公司兩個(gè)層面來(lái)分析。你能想象曾經(jīng)從一個(gè)疏忽學(xué)業(yè)的人成為一名資深FAE的嘛? &

2014-08-18 15:38:50

/*本例程是C語(yǔ)言的位域操作示例這里為什么位域結(jié)構(gòu)體與聯(lián)合體一起使用?-->因?yàn)檫@樣定義后,即可以單獨(dú)使用標(biāo)志位 也可同時(shí)使用整個(gè)字節(jié)數(shù)據(jù)主要應(yīng)用:?jiǎn)纹瑱C(jī)C語(yǔ)言好處:用標(biāo)志位可以節(jié)省RAM空間

2021-07-14 06:23:12

求助,不怎么懂這題該怎么做。求教。用兩片四位全加器74283和必要的邏輯門(mén)設(shè)計(jì)一個(gè)數(shù)制轉(zhuǎn)換電路,實(shí)現(xiàn)將輸入的兩位十進(jìn)制數(shù)轉(zhuǎn)換成二進(jìn)制數(shù),十進(jìn)制數(shù)的輸入采用8421BCD碼來(lái)表示。用multisim仿真畫(huà)圖。

2016-07-01 20:13:27

32.768kHz振蕩器為OSCSCLK,此控制位無(wú)效。是不是可以這樣理解,假設(shè)外接晶振 12MHz 作為系統(tǒng)時(shí)鐘,那么(CLKS1CLKS0)兩位配置情況的機(jī)器周期對(duì)應(yīng)如下:00:一個(gè)機(jī)器周期 = 1/12MHz

2013-12-06 13:47:38

,其值顯示在數(shù)碼管的低兩位。圖10.80 AD和DA聯(lián)合實(shí)例功能框圖本實(shí)例模塊劃分如圖10.81所示。圖10.81 AD和DA聯(lián)合實(shí)例模塊層次板級(jí)調(diào)試連接好下載線,給CY4開(kāi)發(fā)板供電。打開(kāi)Quartus

2019-01-26 16:52:56

單片機(jī)串口顯示正常,為什么數(shù)據(jù)統(tǒng)計(jì)的數(shù)量少兩位呢

2023-10-25 06:34:02

`嚇到兩位大叔了。。。`

2012-10-24 16:23:08

在FPGA上加速過(guò)winograd嗎,有沒(méi)有和arm端做過(guò)加速結(jié)果比較

2022-09-21 11:28:56

FPGA加速卡是如何產(chǎn)生的?主要的FPGA加速卡產(chǎn)品有哪些?基于加速卡的FPGA生態(tài)系統(tǒng)布局是怎樣的?

2021-06-17 06:07:15

keil proteus仿真軟件 三、實(shí)驗(yàn)內(nèi)容在proteus軟件上實(shí)現(xiàn)8個(gè)發(fā)光LED,并通過(guò)編寫(xiě)程序控制LED發(fā)光現(xiàn)象并顯示自己的學(xué)號(hào)末兩位。 四、實(shí)驗(yàn)要求: 在LED中顯示自己的學(xué)號(hào)后兩位

2018-07-19 07:00:04

堆棧指針的最低兩位永遠(yuǎn)是0的原因是什么?

2022-01-26 06:09:38

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

我在用c語(yǔ)言編寫(xiě)lcd顯示的簡(jiǎn)易計(jì)算器,現(xiàn)在遇到一個(gè)問(wèn)題,除法運(yùn)算時(shí)怎樣編寫(xiě)可以實(shí)現(xiàn)結(jié)果保留兩位小數(shù)呢?大神們給個(gè)大概思路就好

2019-09-26 22:52:56

前言:做STM32的時(shí)候,定時(shí)器有兩個(gè)倍頻系數(shù),有時(shí)候頻率需要精確到小數(shù)后面,本例說(shuō)明如何在小數(shù)點(diǎn)后面兩位精確:STM31F103的最大頻率為7.2000e+07,那么如果要精確到小數(shù)點(diǎn)后面兩位

2021-08-17 07:02:19

設(shè)計(jì)一個(gè)兩位倒計(jì)時(shí)秒表,可通過(guò)按鍵啟動(dòng)和暫停,計(jì)時(shí)顯示于數(shù)碼管。

2019-10-20 10:31:01

寶德0330型兩位兩通電磁閥,寶德中國(guó)區(qū)域總代理原裝德國(guó)寶德BURKERT 0330 兩位兩通產(chǎn)品特性兩位兩通電磁閥的技術(shù)參數(shù),帶伺服膜片和與介質(zhì)隔離的三通先導(dǎo)控制。標(biāo)準(zhǔn)供貨為常閉和常開(kāi)回路功能

2018-07-18 08:58:27

新手求助5腳兩位半數(shù)碼管是怎樣進(jìn)行工作的?使用5腳兩位半數(shù)碼管有何注意事項(xiàng)?

2022-03-01 06:45:13

本人想用dsp和fpga聯(lián)合弄步進(jìn)電機(jī)控制,請(qǐng)問(wèn)一個(gè)大概的實(shí)現(xiàn)方向是什么樣的

2015-04-16 16:24:17

以前沒(méi)有做的兩位停止位的485通信,最近剛碰到

2023-06-19 10:29:31

想用ARM和FPGA聯(lián)合調(diào)用控制電機(jī)等,不知道現(xiàn)在主要用哪些芯片呢

2017-02-04 10:32:17

求助,如何利用ne555,lm393,74ls47芯片實(shí)現(xiàn)兩位共陽(yáng)數(shù)碼管的動(dòng)態(tài)顯示。

2021-12-23 19:37:01

!大家一起來(lái)看看特權(quán)同學(xué)告訴你哪些不為人知的秘訣:設(shè)計(jì)教訓(xùn)如何成就稱(chēng)職的FPGA資深工程師?作為ASIC領(lǐng)域中一種半定制電路,FPGA的發(fā)展不但解決了定制電路不足,并且能夠克服可編程器件門(mén)電路數(shù)有限

2013-08-20 16:50:48

4*4矩陣鍵盤(pán)輸入一個(gè)兩位數(shù),顯示在一個(gè)兩位數(shù)碼管上。程序如下:現(xiàn)在的問(wèn)題是我接一位的數(shù)碼管能正常顯示數(shù),接兩位的就像圖片中亂碼了?這是為什么呢?#includeunsigned char code

2017-02-24 21:26:00

第2

位和第3

位,跟下面的第0

位和第1

位什么區(qū)別?看他的字面意思好像是一個(gè)硬件狀態(tài)指示,就是說(shuō)第0,1

位配置為什么,這

兩位就相應(yīng)的變?yōu)槭裁磫幔?/div>

2019-01-16 01:56:22

我在用c語(yǔ)言編寫(xiě)lcd顯示的簡(jiǎn)易計(jì)算器,現(xiàn)在遇到一個(gè)問(wèn)題,除法運(yùn)算時(shí)怎樣編寫(xiě)可以實(shí)現(xiàn)結(jié)果保留兩位小數(shù)呢?給個(gè)大概思路就好

2019-04-17 03:16:29

所以先求出原碼再計(jì)算的,符號(hào)位存在別的變量中,每個(gè)軸的分量計(jì)算 :*39/100 擴(kuò)大了100位實(shí)際是保留兩位小數(shù)起初校驗(yàn)值 是0x10,-0x03,-0x03,但是X軸的輸出范圍有些大,便改為0x00

2019-04-16 03:06:21

全球領(lǐng)先的中文互聯(lián)網(wǎng)搜索引擎提供商百度正在采用賽靈思FPGA加速其中國(guó)數(shù)據(jù)中心的機(jī)器學(xué)習(xí)應(yīng)用。兩家公司正合作進(jìn)一步擴(kuò)大FPGA加速平臺(tái)的部署規(guī)模。新興應(yīng)用的快速發(fā)展正日漸加重計(jì)算工作的負(fù)載,數(shù)據(jù)中心

2016-12-15 17:15:52

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-03-04 11:13:54

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-03-11 11:07:39

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-03-18 11:16:02

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-03-25 11:34:03

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-04-01 10:53:42

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-04-11 14:45:24

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-04-18 14:12:57

產(chǎn)品編號(hào):1501013高性能FPGA計(jì)算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊(cè)( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計(jì)算研發(fā)中心Copyright

2016-04-27 11:51:14

資深玩家教您看筆記本鍵盤(pán)

筆記本電腦中鍵盤(pán)是成本比較低的部件,就大批量采購(gòu)成本而言,相比起cpu動(dòng)輒200美金以上的身價(jià),最

2010-01-19 11:43:16 684

684 看似簡(jiǎn)單的幾個(gè)問(wèn)題,Andrew卻回答的井井有條,小編已經(jīng)沒(méi)有辦法有什么其他詞語(yǔ)去形容了。本文Andrew不僅僅對(duì)FPGA入門(mén)學(xué)習(xí)流程做了詳細(xì)的分享,更是對(duì)FPGA開(kāi)發(fā)工作的要求分成大公司和小公司兩個(gè)層面來(lái)分析。你能想象曾經(jīng)從一個(gè)疏忽學(xué)業(yè)的人成為一名資深FAE的嘛?

2014-08-21 10:11:47 31136

31136 SuperVessel將包括賽靈思SDAccel開(kāi)發(fā)環(huán)境,支持用C、C++和OpenCL實(shí)現(xiàn)FPGA加速 All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司與IBM公司今天聯(lián)合宣布

2017-02-08 16:06:08 228

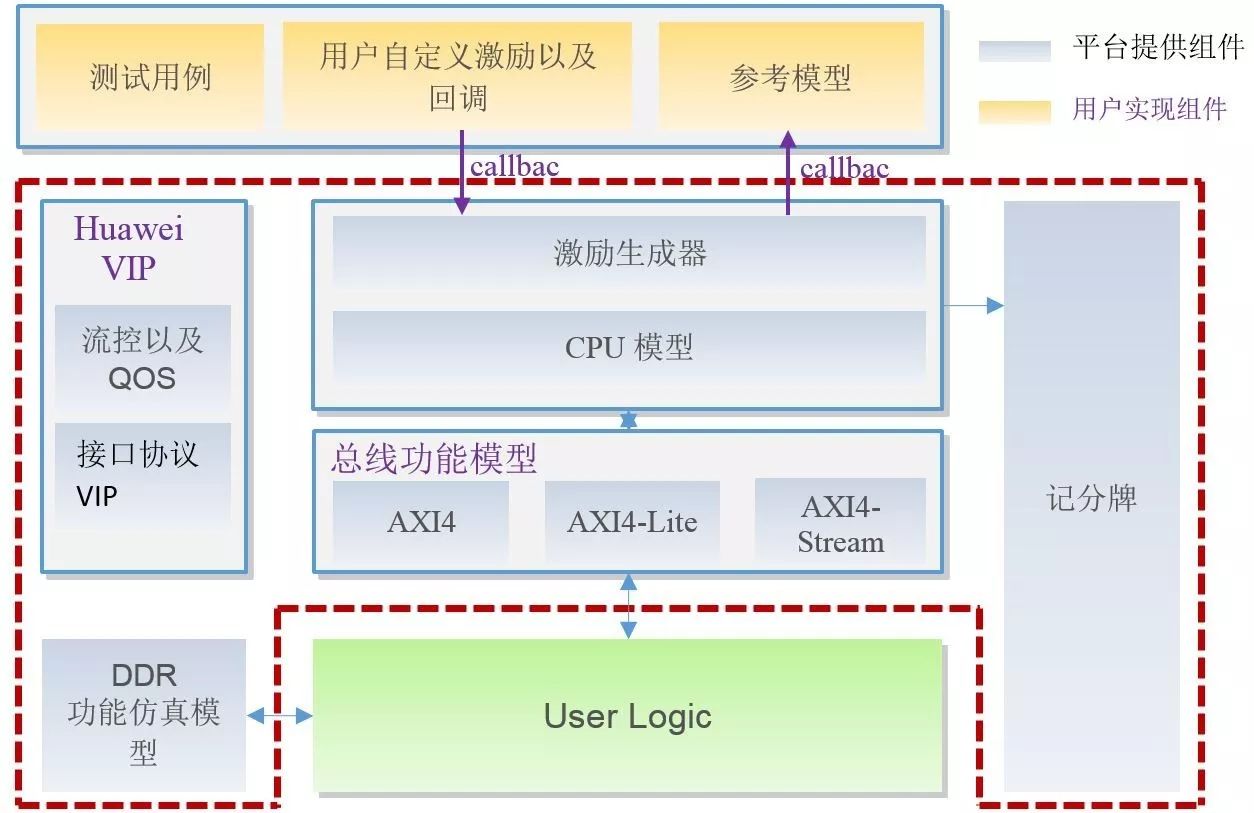

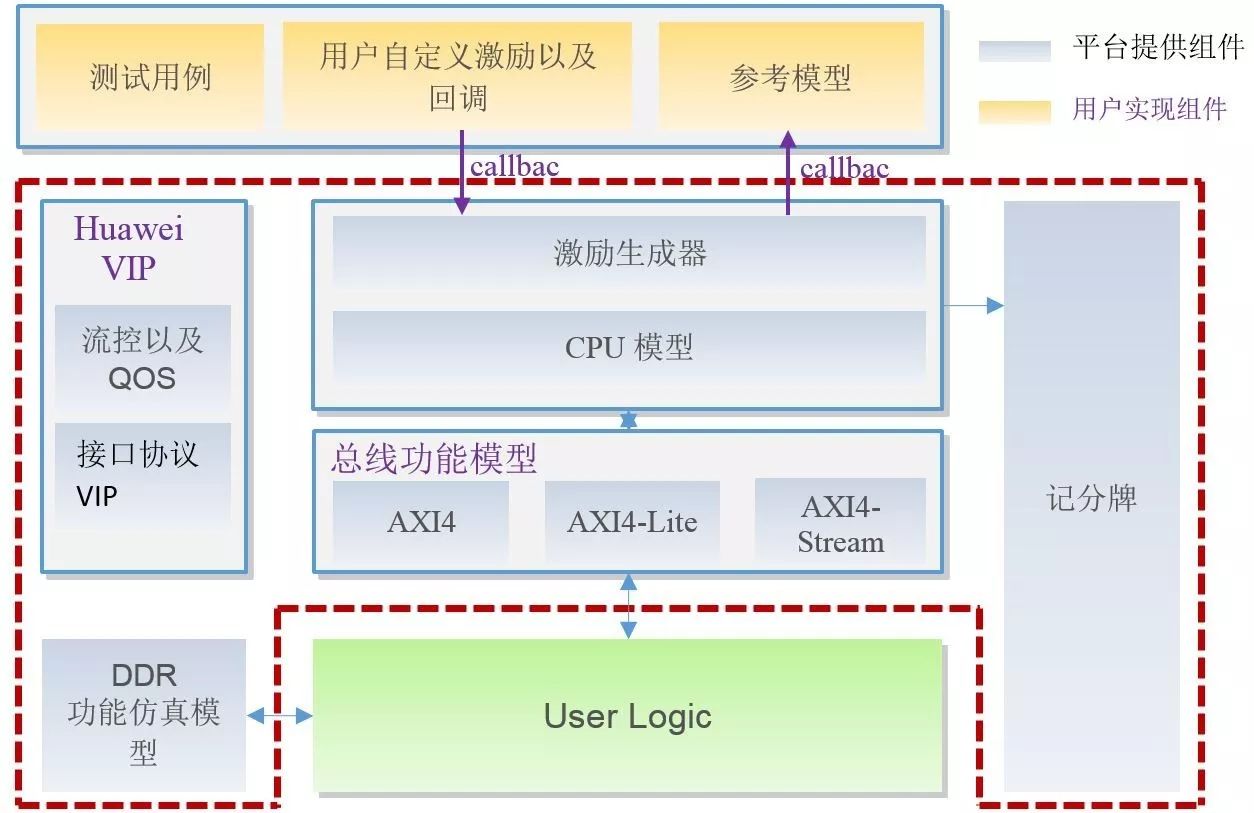

228 在數(shù)據(jù)中心引入 FPGA 并實(shí)現(xiàn)云化加速業(yè)務(wù)成為必然趨勢(shì)。隨著華為云 FPGA 加速服務(wù)的推出,打破原有 FPGA 開(kāi)發(fā)、測(cè)試和應(yīng)用存在的較高門(mén)檻,開(kāi)啟了一個(gè)顛覆 FPGA 開(kāi)發(fā)的新時(shí)代!

2017-10-10 10:49:17 4798

4798

據(jù)稱(chēng),本次三家聯(lián)合發(fā)布的解決方案是業(yè)界首個(gè)在電信云中采用FPGA完成商用級(jí)vBRAS數(shù)據(jù)面調(diào)度加速的端到端方案。該聯(lián)合方案硬件部分是聯(lián)想的交換機(jī)和服務(wù)器,其中包括英特爾的CPU和PAC;軟件部分由聯(lián)想的VIM、賽特斯的VNFM、還有中國(guó)電信北京研究院的NFVO組成。

2018-07-06 08:30:00 1120

1120 隨著IT和人工智能技術(shù)快速發(fā)展,尋找高能效比的數(shù)據(jù)中心加速方案至關(guān)重要。華為在賽靈思開(kāi)發(fā)者論壇上與賽靈思聯(lián)合發(fā)布了FX系列FPGA加速卡,為基因測(cè)序、視頻編碼、圖片處理、數(shù)據(jù)壓縮等業(yè)務(wù)提供了高能效比的加速解決方案

2018-11-07 09:29:33 9845

9845 近日,基于現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)的數(shù)據(jù)加速器件和高性能嵌入式FPGA(eFPGA)半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)領(lǐng)導(dǎo)性企業(yè)Achronix半導(dǎo)體公司,與Molex旗下的一家領(lǐng)先企業(yè)級(jí)FPGA加速器產(chǎn)品供應(yīng)商BittWare今日聯(lián)合宣布:推出一類(lèi)全新的、面向高性能計(jì)算和數(shù)據(jù)加速應(yīng)用的FPGA加速卡。

2019-10-31 15:11:33 737

737 Achronix半導(dǎo)體公司與Mo-lex旗下FPGA加速器產(chǎn)品供應(yīng)商BittWare聯(lián)合推出全新的、面向高性能計(jì)算和數(shù)據(jù)加速應(yīng)用的FPGA加速卡,可實(shí)現(xiàn)云計(jì)算與邊緣計(jì)算加速,助力高帶寬應(yīng)用。

2019-11-08 15:07:23 562

562 近日,FPGA的數(shù)據(jù)加速器件和高性能嵌入式FPGA半導(dǎo)體知識(shí)產(chǎn)權(quán)Achronix公司與Molex旗下的一家領(lǐng)先企業(yè)級(jí)FPGA加速器產(chǎn)品供應(yīng)商BittWare在深圳聯(lián)合舉行了新產(chǎn)品的媒體發(fā)布會(huì)

2019-11-08 15:11:59 1050

1050 華碩ROG玩家國(guó)度與NVIDIA聯(lián)合打造ROG Swift 360Hz,這是一款擁有360Hz超高刷新率的,24.5英寸專(zhuān)業(yè)競(jìng)賽屏。

2020-01-07 13:53:13 2167

2167 近日,元腦生態(tài)伙伴深維科技與浪潮聯(lián)合發(fā)布業(yè)內(nèi)首個(gè)基于FPGA的HEIF圖像處理加速方案。

2020-10-23 11:16:53 2200

2200

“創(chuàng)悅智行”聯(lián)合加速計(jì)劃由現(xiàn)代汽車(chē)集團(tuán)創(chuàng)新中心(北京)(Hyundai CRADLE Beijing)協(xié)同騰訊智慧出行、現(xiàn)代摩比斯(Hyundai Mobis)、Vπ張江孵化器聯(lián)合發(fā)起,旨在依托孵化加速、戰(zhàn)略協(xié)同、戰(zhàn)略投資這一完整創(chuàng)新鏈路,賦能智能汽車(chē)領(lǐng)域的初創(chuàng)企業(yè)。

2021-05-24 10:34:40 1271

1271 在去年電子創(chuàng)新網(wǎng)舉辦的2019FPGA應(yīng)用創(chuàng)新論壇上,一家低調(diào)的FPGA新玩家引發(fā)了大家極大的興趣,它就是EFINIX公司,為何全球FPGA領(lǐng)頭羊賽靈思會(huì)投資這家公司?它的創(chuàng)始人團(tuán)隊(duì)有多牛?他們搗鼓出來(lái)的FPGA新架構(gòu)到底有什么獨(dú)特性?本文為你詳細(xì)介紹。

2022-02-09 11:29:32 1

1 正值當(dāng)前硬件加速器依托異構(gòu)計(jì)算異軍突起之際,高性能FPGA和嵌入式FPGA(eFPGA)半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)領(lǐng)域的領(lǐng)導(dǎo)性企業(yè)Achronix半導(dǎo)體公司近期先后宣布:任命臺(tái)積電(TSMC)資深

2022-04-06 20:10:05 3169

3169

新技術(shù)星期二:加速 FPGA 計(jì)算的 2 張卡

2022-12-30 09:40:20 539

539 引言Preface隨著芯片設(shè)計(jì)規(guī)模的增加,傳統(tǒng)基于單顆FPGA的設(shè)計(jì)調(diào)試方法已經(jīng)不能滿(mǎn)足對(duì)大型設(shè)計(jì)的調(diào)試需求,因此多FPGA聯(lián)合調(diào)試技術(shù)應(yīng)運(yùn)而生。本次國(guó)微思爾芯白皮書(shū)《先進(jìn)多FPGA聯(lián)合深度調(diào)試方法

2022-06-16 10:16:48 627

627

電子發(fā)燒友網(wǎng)站提供《基于FPGA的加速基礎(chǔ)知識(shí).pdf》資料免費(fèi)下載

2023-09-18 10:12:20 0

0 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論