作者: Teledyne e2v 公司 Marie-Charlotte Leclerc

新的成像應用正在蓬勃發展,從工業 4.0 中的協作機器人,到無人機消防或用于農業,再到生物特征面部 識別,再到家庭中的護理點手持醫療設備。出現這些新應用程序的一個關鍵因素是,嵌入式視覺比以往任 何時候都更普及。嵌入式視覺不是一個新概念;它只是定義了一個系統,其中包括一個視覺設置,在沒有 外部計算機的情況下控制和處理數據。它已廣泛應用于工業質量控制,最為人熟悉的例子比如“智能相機”。

近年源于消費類市場經濟適用硬件器件的開發,相較于以往使用電腦的方案,這些器件大幅度減小了材料 清單(BOM)成本和產品體積。舉個例子,小型系統集成商或 OEM 現在能夠小批量采購諸如 NVIDIA Jetson 的單板機或模塊系統;而較大型的 OEM 則可以直接獲得如高通驍龍(Qualcomm Snapdragon)或英 特爾(Intel) Movidius Myriad 2 等圖像信號處理器。在軟件級方面,市面軟件庫能夠加快專用視覺系統的開 發速度,減小配置難度,即便是針對小批量生產。

第二個推動嵌入式視覺系統發展的變化是機器學習的出現,它使實驗室中的神經網絡能夠接受培訓,然后 直接上傳到處理器中,以便它能夠自動識別特征,并實時做出決定。

能夠提供適用于嵌入式視覺系統的解決方案,對于面向這些高增長應用的成像企業來說至關重要。圖像傳 感器由于能夠直接影響嵌入式視覺系統的效能和設計,因而在大規模引進中有重要角色,而它的主要推動 因素可概括為:更小尺寸、重量、功耗和成本,英語簡稱為“SWaP-C”(decreasing Size, Weight, Power and Cost)。

1. 降低成本至關重要

嵌入式視覺新應用的加速推動器是滿足市場需求的價格,而視覺系統成本正是實現這要求的一個主要制肘。

1.1. 節省光學成本

減小視覺模塊成本的第一個途徑是縮小產品尺寸, 原因有兩個:首先是圖像傳感器的像素尺寸愈小,晶圓 便可以制造更多的芯片;另一方面傳感器可以使用更小更低成本的光學組件,二者都能夠降低固有成本。 例如 Teledyne e2v 的 Emerald 5M 傳感器把像素尺寸減小至 2.8μm,讓 S 口(M12) 鏡頭能夠用于五百萬 像素全局快門傳感器上,帶來直接的成本節省──入門級的 M12 鏡頭的價格約為 10 美元,而較大尺寸的 C 口或 F 口鏡頭成本是其 10 到 20 倍。所以減小尺寸是降低嵌入式視覺系統成本的有效方法。

對于圖像傳感器制造商來說,這種降低的光學成本對設計有另一個影響,因為一般來說,光學成本越低, 傳感器的入射角越不理想。因此,低成本光學需要在像素上方設計特定的位移微透鏡,以補償來自廣角的 畸變和聚焦光。

1.2. 傳感器低成本接口

除了光學優化,傳感器接口的選擇也間接影響視覺系統的成本。MIPI CSI-2 接口是實現節約成本的最合適 選擇(它最初是由 MIPI 聯盟為移動行業開發的)。它已被大多數 ISP 廣泛采用,并已開始在工業市場采 用,因為它提供了一個從 NXP、Nvidia、高通公司或 Intel 等公司的低成本的片上系統(SOC)或模塊上 系統(SOM)的集成。設計一種具有 MIPI CSI-2 傳感器接口的 CMOS 圖像傳感器,無需任何中間轉換器 橋,直接將圖像傳感器的數據傳輸到嵌入式系統的主機 SOC 或 SOM,從而節省了成本和 PCB 空間,當 然,在基于多傳感器的嵌入式系統(如 360 度全景系統)中,這一優勢更為突出。

不過這些好處受到一些限制,因為 MIPI 接口的連接距離限制為 20 cm,這在傳感器距離主機處理器較遠 的遠程設置中可能不是最佳的。在這些配置中,以犧牲小型化為代價,使用集成更長接口的相機板解決方 案是比較好的選擇。一些現成的解決方案可以集成,例如工業相機制造商(如 Flir、AVT、Basler 等)的 相機板通常可在 MIPI 或 USB3 接口中使用,后者能夠達到的范圍可以超過 3 米至 5 米。

1.3. 減小開發成本

在投資新產品時,不斷上升的開發成本往往是一個挑戰;它可能會在一次性開發費上花費數百萬美元,并 給上市時間帶來壓力。對于嵌入式視覺,這種壓力變得更大,因為模塊化(即產品能否切換使用多種圖像 傳感器)是集成商的重要考慮。幸運的是,通過在傳感器之間提供一定程度的交叉兼容性,例如,通過定 義共享相同像素體系結構的組件系列以具有穩定的光電性能,通過具有共用光學中心來共享單個前端機制, 以及通過兼容的 PCB 組件來簡化評估,集成和供應鏈,從而減小開發費用。

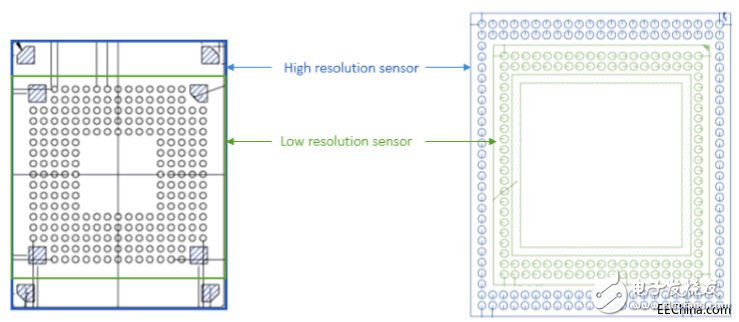

為簡化相機板設計(即使用于多款傳感器),有兩種方法設計傳感器封裝。針腳對針腳兼容是相機板設計 人員的首選設計,因為它能使多種傳感器共享同一電路和控制,使得組裝完全不受 PCB 設計影響。另一 個選擇是采用尺寸兼容的傳感器,這樣同一 PCB 可以使用多款傳感器,但是這也意味著他們可能要應付 每一款傳感器的接口和布線的差異狀況。

圖 1: 圖像傳感器可經設計提供針腳兼容 ( 圖左 ) 或尺寸兼容 ( 圖右 ) 以實現專有 PCB布局設計

2. 能效提供更佳單獨工作能力

微型電池驅動的設備是最明顯的受益于嵌入式視覺的應用程序,因為外部計算機阻止任何便攜式應用程序 的發生。為了降低系統的能耗,圖像傳感器現在包含了多種功能,使系統設計者能夠節省電力。

從傳感器角度出發,有多種方法減小嵌入式視覺系統功耗而不損采集幀率。最簡單的方法是通過盡可能長 時間使用待機或閑置模式,在系統級最小化傳感器本身的動態操作。待機模式通過關閉仿真電路,把傳感 器的功耗降低到工作模式的 10%以下。而閑置模式則可把功耗減半,并讓傳感器在數微秒內重新啟動獲取 圖像。

而在傳感器設計集成節能的另一個方法是采用先進光刻節點技術。技術節點越小,轉換晶體管所需的電壓 便越小,由于功耗與電壓成正比,這樣就能降低功耗。所以 10 年前使用 180nm 技術 生產的像素不單把晶體管縮小到 110nm,同時也把數字電路的電壓從 1.9 伏降到 1.2 伏。下一世代的傳感 器將使用 65nm 技術節點,使得嵌入式視覺應用更省能。

最后一點是,通過選擇合適的圖像傳感器,可以在某些條件下降低 LED 燈的能耗。有一些系統必須使用 主動照明,例如三維地圖生成、動作停頓、或是純粹使用順序脈沖指定波長來提高反差。在這些情形下, 減低圖像傳感器在低亮度環境下的噪聲便能實現更低的功耗。減小了傳感器噪聲,工程人員便可決定減小 電流密度強度,或是減小集成進嵌入式視覺系統的 LED 燈數目。在其他情況下,當圖像捕獲和 LED 閃爍 由外部事件觸發時,選擇適當的傳感器讀出結構可以顯著節省電能。使用傳統卷簾快門傳感器,幀全曝光 時 LED 燈必需全開,而全局快門傳感器則允許只在幀的某部份開動 LED 燈。所以如使用像素內相關雙采 樣(CDS)應用下,以全局快門傳感器替代卷簾快門傳感器就可以節省照明成本,同時仍保持與顯微鏡中使 用的 CCD 傳感器一樣低的噪聲。

3. 片上功能為應用程序設計的視覺系統鋪平了道路

嵌入式視覺的一些偏鋒延展概念,引導我們對圖像傳感器進行全面定制,以 3D 堆疊方式集成所有處理功 能(芯片上的系統) 以實現優化性能和功耗。不過,開發這一類產品的成本十分高昂,能夠達到這一集成 水平的全定制傳感器長遠來說并非完全不可能,而現在我們正處于一個過渡階段,包含將某些功能直接嵌 入到傳感器,以減省計算負載和加快處理時間。

例如在條形碼閱讀應用, Teledyne e2v 公司已擁有專利技術,將包含一個專有條形碼識別算法的嵌入式 功能加進傳感器芯片,這算法可以找出每一幀幅內的條形碼位置,讓圖像信號處理器只需聚焦于這些范圍, 提高數據處理效率。

圖二: Teledyne e2v Snappy 五百萬像素芯片,自動識別條形碼位置

另一個減少處理負載和優化“良好”數據的功能是 Teledyne E2V 的專利快速曝光模式,該模式使傳感器能 夠自動校正曝光時間,以避免照明條件變化時出現飽和。這項功能優化了處理時間,因為它適應了單幀中 光照的波動,而且這種快速反應最大限度地減少了處理器需要處理的“壞”圖像的數量。

這些功能通常是特定的,需要很好地理解客戶的應用程序。只要對應用程序有足夠的了解,就可以設計多 種其他片上功能來優化嵌入式視覺系統。

4. 減小重量尺寸以配合最小應用空間

嵌入式視覺系統的另一主要要求是能夠配合狹小空間,或是重量要小,以便用于手持式設備/或延長電池推 動產品的工作時間。這就是現在大部份嵌入式視覺系統使用只有 1MP 到 5MP 的低分辨率小型光學格式傳 感器的原因。

減小像素芯片的尺寸只是減小圖像傳感器占位面積和重量的第一步。現在的 65nm 工藝讓我們能夠把全局 快門像素尺寸減小至 2.5μm 而不損光電性能。這種生產工藝使得諸如全高清全局快門 CMOS 圖像傳感器 能夠配合手機市場要求小于 1/3 英寸的規格。

減小傳感器重量和占位面積的另一主要技術是縮小封裝尺寸。芯片級封裝在過去數年在市場迅速成長, 在移動、車載電子和醫療應用中特別明顯。相較用工業市場常用的傳統陶瓷 (Ceramic Land Grid Array, 簡稱 CLGA) 封裝,芯片級扇出封裝能夠實現更高密度連接,因而是嵌入式系統圖像傳感器輕量化小型化 挑戰的出色解決方案。例如 Teledyne e2v 的 Emerald 2M 圖像傳感器芯片級封裝,側高只是陶瓷封裝的 一半,而尺寸則減小 30%。

圖 3 :同一芯片采用 CLGA 封裝 ( 圖左 ) 和晶圓級扇出有機封裝 ( 圖右 ) 的比較。后者能夠減少占位、厚 度和成本。 。

展望未來,我們預期新的技術能進一步實現嵌入式視覺系統所需的更小傳感器尺寸。

三維堆棧是讓半導體器件生產的創新技術,它的原理是在不同晶圓上制造各種電路芯片,然后利用銅對銅 連接和過硅沖孔(Through Silicon Vias,簡稱 TSV)技術進行堆棧和互聯。三維堆棧因為是多層重迭芯片, 允許器件實現比傳統傳感器更小的占位尺寸。而在三維堆棧傳感器中,讀出和處理芯片可以置于像素芯片 和行譯碼器的下方。這樣,傳感器的占位尺寸因縮小的讀出和處理芯片而減小,并且可以在傳感器中加入 更多處理資源以減小圖像信號處理器的載荷。

圖 4 :三維芯片堆棧技術有助于實現像素芯片、仿真和數字電路,甚至是用于專門應用的附加處理芯片組合重迭,減小傳感器面積。

不過,要讓三維堆棧技術在圖像傳感器市場獲得廣泛應用,現在還面對著一些挑戰。首先這是一個新興的 技術,其次是它的成本較高,因為需要附加的工藝步驟,使得芯片成本比使用傳統技術的芯片高三倍以上。 因為三維埋迭將主要是高性能或非常小占位尺寸的嵌入式視覺系統的選擇。

總結而言,嵌入式視覺系統可以歸納為一種“輕量”視覺技術,可以用于包括 OEM、系統集成商和標準 相機廠商等不同類型企業。“嵌入式 “是一個可用于不同應用的概括性描述,因而不能開出列表說明它的特 征。不過優化嵌入式視覺系統有幾個適用法則,就是一般而言,市場推動力并非來自超級快的速度或超高 的靈敏度,而是尺寸、重量、功耗和成本。圖像傳感器是這些條件的主要推手,所以需要小心選擇合適的 圖像傳感器,以便于優化嵌入式視覺系統的總體性能。合適的圖像傳感器能為嵌入式設計人員帶來更多靈 活性,節省材料清單成本,減小照明和光學組件的占位面積。它也讓設計人員在無需面對更多復雜性的情 況下,選擇來自消費市場的大量經濟適用并具有優化深度學習功能的圖像信號處理器。

電子發燒友App

電子發燒友App

評論