1.引言

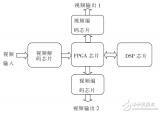

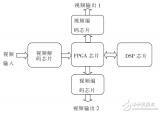

本文針對(duì)紅外圖像處理系統(tǒng)的實(shí)時(shí)性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構(gòu)。

隨著紅外焦

2010-07-22 15:18:50 796

796 我們提供完善的FPGA設(shè)計(jì)開(kāi)發(fā)、嵌入式系統(tǒng)、板卡設(shè)計(jì)開(kāi)發(fā)等相關(guān)解決方案。提供基于Xilinx/Altera FPGA的高性能計(jì)算(HPC)硬件平臺(tái)、FGPA加速卡;FPGA加速卡(平臺(tái))在數(shù)

2017-10-18 15:39:32

,都說(shuō)思想不一樣,要有硬件編程的思想。呵呵,至今也木有發(fā)現(xiàn)。設(shè)計(jì):設(shè)計(jì)方面,FPGA注重進(jìn)行的是芯片的設(shè)計(jì),而嵌入式所注重的是功能的設(shè)計(jì),由于本人還是在初級(jí)階段,FPGA沒(méi)做過(guò)什么項(xiàng)目,哎,有種無(wú)無(wú)力感。算法:我的導(dǎo)師要我看看圖像處理的算法。算了 以后再寫。

2013-10-12 20:18:08

多目標(biāo)優(yōu)化算法有哪些,該文圍繞包含柴油發(fā)電機(jī)、風(fēng)力發(fā)電、光伏發(fā)電和鉛酸蓄電池的獨(dú)立微網(wǎng)系統(tǒng)中的容量配置問(wèn)題,提出了包含微網(wǎng)全壽命周期內(nèi)的總成本現(xiàn)值、負(fù)荷容量缺失率和污染物排放的多目標(biāo)優(yōu)化設(shè)計(jì)模型。該

2021-07-12 06:52:54

本人想做數(shù)字圖像處理方面的課題,不知道DSP和FPGA的器件怎么選擇,希望有經(jīng)驗(yàn)的大神給點(diǎn)建議,我做的這個(gè)課題是用FPGA和DSP處理圖像 dsp作為主處理器,負(fù)責(zé)主要的算法,FPGA負(fù)責(zé)從處理

2012-08-06 10:54:12

最近在做一個(gè)四軸飛行器,需要在其上搭載攝像頭和圖像處理設(shè)備,能夠?qū)ε臄z到的視頻進(jìn)行實(shí)時(shí)的處理,進(jìn)而得到環(huán)境的信息。什么樣的系統(tǒng)(板?嵌入式?)能完成這個(gè)任務(wù)?我看到的這方面的一個(gè)例子中提到了:1.6

2014-03-12 18:47:39

Linux支持PowerPC、MIPS、ARM、DSP等多種嵌入式處理器,逐漸被用于多種關(guān)鍵性場(chǎng)合。其中實(shí)時(shí)多媒體處理、工業(yè)控制、汽車電子等特定應(yīng)用對(duì)Linux提出了強(qiáng)實(shí)時(shí)性需求。Linux提供了

2019-10-08 14:19:33

常所說(shuō)的單片機(jī)側(cè)重于控制,不支持信號(hào)處理,屬于低端嵌入式處理器,arm可以看做是低端單片機(jī)升級(jí)版,支持操作系統(tǒng)管理,更多接口如網(wǎng)卡,處理能力更強(qiáng);fpga是可編程邏輯器件,側(cè)重時(shí)序,可構(gòu)建從小型到

2018-10-10 18:02:03

嵌入式開(kāi)發(fā)中DSP與FPGA的關(guān)系常所說(shuō)的單片機(jī)側(cè)重于控制,不支持信號(hào)處理,屬于低端嵌入式處理器,arm可以看做是低端單片機(jī)升級(jí)版,支持操作系統(tǒng)管理,更多接口如網(wǎng)卡,處理能力更強(qiáng);fpga

2021-12-15 09:06:11

嵌入式系統(tǒng)中的目標(biāo)識(shí)別技術(shù)

2021-03-09 08:33:26

本文將回顧一系列的特征檢測(cè)算法,在這個(gè)過(guò)程中,看看一般目標(biāo)識(shí)別和具體特征識(shí)別在這些年經(jīng)歷了怎樣的發(fā)展。

2021-06-02 06:24:59

特性,使其成為各項(xiàng)生物識(shí)別技術(shù)中最突出的一項(xiàng)。本文論述了在基于Blackfin561的嵌入式操作系統(tǒng)uClinux的虹膜圖像采集以及預(yù)處理。為后期在嵌入式平臺(tái)上進(jìn)行虹膜圖像運(yùn)算提供了圖像來(lái)源。

2020-03-30 06:54:41

大神們,我是剛剛接觸ARM嵌入式圖像處理,之前也沒(méi)有接觸過(guò)ARM,有沒(méi)有誰(shuí)做過(guò)ARM嵌入式圖像處理的,都是用的哪種ARM開(kāi)發(fā)板,一般大家普遍用的、性價(jià)比高的具體是哪種型號(hào)的,有沒(méi)有同時(shí)有ARM

2014-08-19 09:56:26

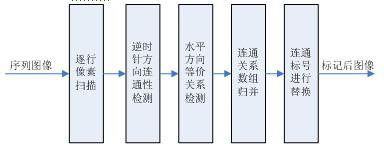

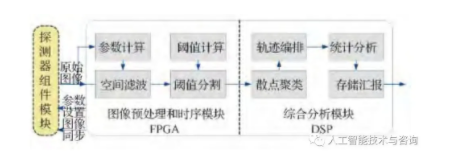

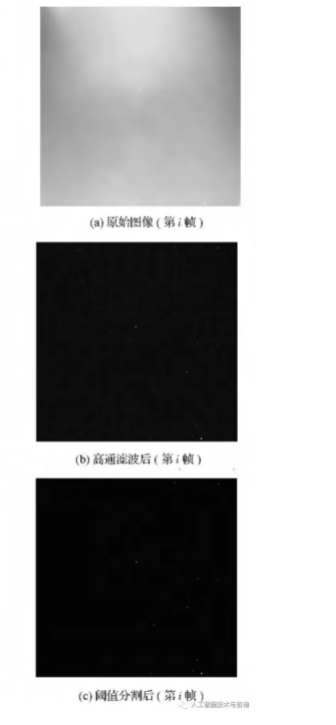

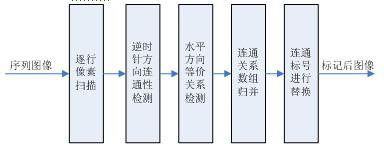

小目標(biāo)檢測(cè)系統(tǒng)的任務(wù)是根據(jù)探測(cè)器獲取的圖像序列實(shí)時(shí)地把小目標(biāo)從噪聲中檢測(cè)出來(lái),它的實(shí)現(xiàn)是目標(biāo)識(shí)別跟蹤的前提和基礎(chǔ)。小目標(biāo)檢測(cè)需要對(duì)探測(cè)到的圖像進(jìn)行實(shí)時(shí)處理,運(yùn)算量巨大。另外,特殊的應(yīng)用環(huán)境又對(duì)小目標(biāo)

2019-08-09 07:07:03

申請(qǐng)理由:1·國(guó)家級(jí)創(chuàng)新項(xiàng)目,本設(shè)計(jì)是一種針對(duì)現(xiàn)代大型物流倉(cāng)庫(kù)設(shè)計(jì)的的基于GPRS和DSP數(shù)字圖像處理的嵌入式火災(zāi)預(yù)警系統(tǒng),ARM是主控制器,DSP是數(shù)字圖像協(xié)處理器。在ARM和μC/OS-II系統(tǒng)

2015-07-29 18:50:00

很低,實(shí)時(shí)性完全達(dá)不到,必須要在高性能多核心的嵌入式處理器上剪裁具有針對(duì)性的Linux系統(tǒng),并搭建OpenCV運(yùn)行庫(kù),實(shí)現(xiàn)高性能驅(qū)動(dòng),來(lái)達(dá)到對(duì)實(shí)時(shí)性的要求。滿足要求,技術(shù)成熟的只有DSP和ARM架構(gòu)

2015-12-02 16:14:27

的同時(shí),對(duì)嵌入式系統(tǒng)有更深的理解。項(xiàng)目描述:首先移植Linux系統(tǒng)到板卡上,熟悉嵌入式操作系統(tǒng)后,像利用樹(shù)莓派一樣移植圖像處理庫(kù),接入外部攝像頭,實(shí)現(xiàn)運(yùn)動(dòng)檢測(cè),動(dòng)作識(shí)別,物體識(shí)別等常見(jiàn)的圖像操作。也可通過(guò)

2015-07-31 20:13:00

項(xiàng)目名稱:圖像目標(biāo)識(shí)別FPGA硬件加速試用計(jì)劃:申請(qǐng)理由 本人供職于一家AI公司,現(xiàn)在在使用FPGA硬件加速相關(guān)目標(biāo)檢測(cè)算法的端側(cè)實(shí)現(xiàn)(鑒黃/司機(jī)行為識(shí)別),公司已經(jīng)有非常成熟的軟件算法以及GPU

2019-01-09 14:51:09

地檢測(cè)出運(yùn)動(dòng)目標(biāo)并能對(duì)其實(shí)現(xiàn)識(shí)別跟蹤,且需要處理的視頻圖像信號(hào)信息量大、實(shí)時(shí)性高,對(duì)系統(tǒng)的處理能力提出了更高的要求。 在之前的幾十年內(nèi),有許多學(xué)者對(duì)視頻序列圖像中的運(yùn)動(dòng)目標(biāo)識(shí)別跟蹤做了大量的研究工作,并提出了很多不同

2015-09-10 11:18:52

申請(qǐng)理由:本人為北工大的研究生,專業(yè)為DSP與嵌入式系統(tǒng)。熟悉DSP和某些圖像算法。現(xiàn)在課題在研究跟蹤算法以及優(yōu)化實(shí)現(xiàn),所以想申請(qǐng)次開(kāi)發(fā)板!望通過(guò)項(xiàng)目描述:項(xiàng)目主要實(shí)現(xiàn)功能是通過(guò)Mean-shift

2015-09-09 16:59:45

申請(qǐng)理由:TMS320C6748是TI公司推出的高速DSP,將其應(yīng)用于微光視頻圖像的實(shí)時(shí)處理,對(duì)于提高系統(tǒng)的實(shí)時(shí)性和采集具有十分重要的意義,同時(shí)也可以講更加復(fù)雜的算法加入其中,對(duì)于微光視頻圖像處理算法

2015-10-09 15:12:31

WaRP7 i.MX 7開(kāi)發(fā)套件實(shí)現(xiàn)OpenCV算法代碼移植,實(shí)現(xiàn)整個(gè)項(xiàng)目完成。應(yīng)用項(xiàng)目:基于嵌入式圖像處理的遠(yuǎn)程終端設(shè)計(jì)項(xiàng)目總體描述和方案:1. 實(shí)現(xiàn)單片機(jī)在lLinux平臺(tái)使用V4L2控制攝像頭拍攝

2017-06-16 16:05:22

本文在研究ARM嵌入式系統(tǒng)原理的基礎(chǔ)上,設(shè)計(jì)了一種基于ARM的嵌入式圖像處理系統(tǒng),該系統(tǒng)包括硬件平臺(tái)的構(gòu)建和軟件架構(gòu)設(shè)計(jì),可以很方便實(shí)現(xiàn)圖像采集、顯示、存儲(chǔ)及處理。該系統(tǒng)采用Qt多線程技術(shù)編寫的圖形應(yīng)用程序,能實(shí)現(xiàn)圖像實(shí)時(shí)顯示和處理,提高了應(yīng)用程序運(yùn)行效率。

2019-07-08 14:55:06

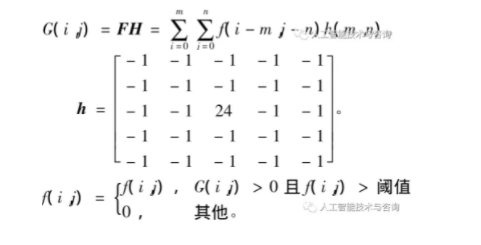

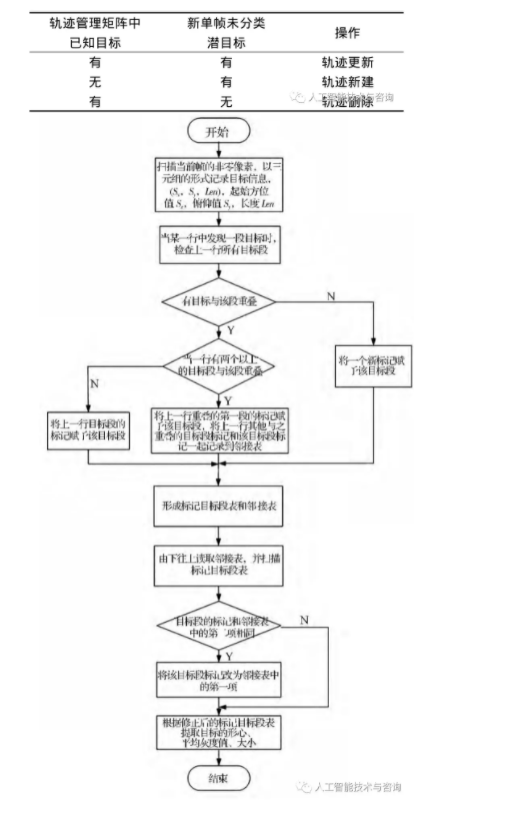

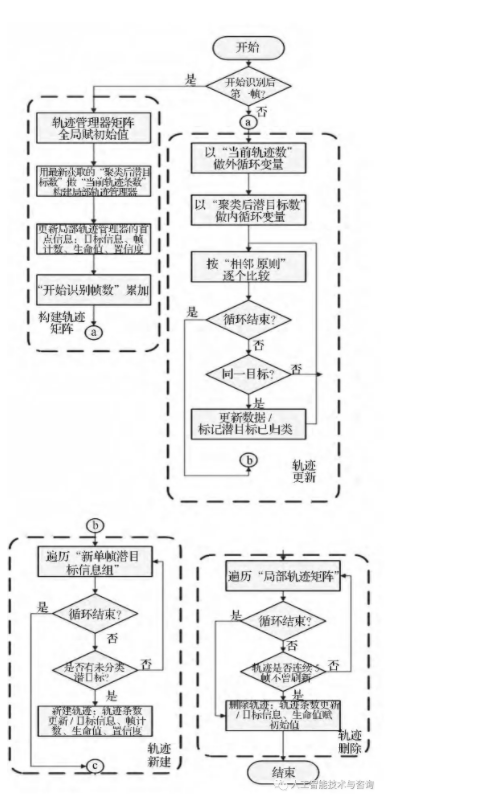

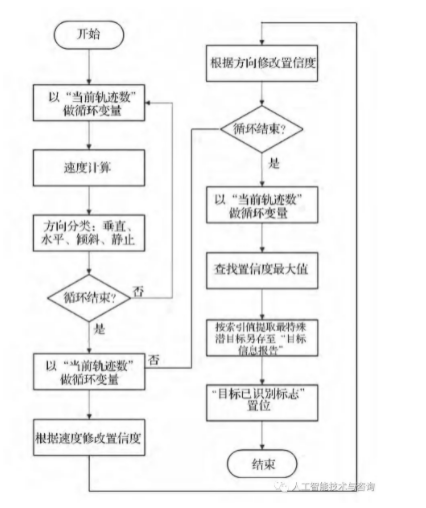

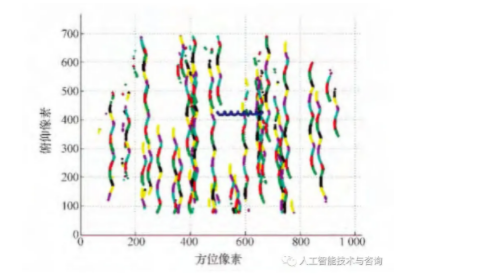

基于嵌入式圖像處理平臺(tái)的實(shí)時(shí)多目標(biāo)識(shí)別算法人工智能技術(shù)與咨詢 昨天本文來(lái)自《科學(xué)技術(shù)與工程》,作者王旭輝等摘 要提出了一種適用于空間觀測(cè)任務(wù)的實(shí)時(shí)多目標(biāo)識(shí)別算法,它基于DSP和FPGA組合的圖像處理

2021-12-21 07:02:06

和 指令 進(jìn)行了特殊設(shè)計(jì),使其適合于實(shí)時(shí)地進(jìn)行 數(shù)字 信號(hào)處理。在數(shù)字濾波、 FFT 、譜分析等方面, DSP 算法正大量進(jìn)入嵌入式領(lǐng)域, DSP 應(yīng)用正從在通用單片機(jī)中以普通指令實(shí)現(xiàn) DSP 功能

2020-04-16 09:53:31

公司的MCS-296和Siemens公司的TriCore。推動(dòng)嵌入式DSP處理器發(fā)展的另一個(gè)因素是嵌入式系統(tǒng)的智能化,例如各種帶有智能邏輯的消費(fèi)類產(chǎn)品、生物信息識(shí)別終端、帶有加解密算法的鍵盤、ADSL

2012-02-02 15:15:33

本人新手,之前從未接觸過(guò)圖像處理,現(xiàn)在因?yàn)轫?xiàng)目需要搭建一個(gè)關(guān)于圖像處理和目標(biāo)識(shí)別的MATLAB系統(tǒng),系統(tǒng)介紹如下: 想要從圖片中將目標(biāo)提取出來(lái)并與模板庫(kù)進(jìn)行匹配對(duì)比,以確定是否為我感興趣的目標(biāo)

2016-07-10 15:05:58

我是剛開(kāi)始學(xué)FPGA,基于FPGA的嵌入式圖像處理,可是我不知道怎么入手,希望可以有人提供一下自己的學(xué)習(xí)經(jīng)驗(yàn)。O(∩_∩)O謝謝!

2014-10-08 17:11:28

DSP是注重?cái)?shù)據(jù)處理。算法很重要。FPGA主要是做邏輯電路.現(xiàn)在很多框架都是基于DSP和FPGA的組合平臺(tái),DSP作算法,FPGA作邏輯時(shí)序!FPGA一樣可以做DSP(DSP就是數(shù)字信號(hào)處理英文縮寫

2021-07-28 09:16:02

電視圖像或紅外兩個(gè)波段,實(shí)現(xiàn)圖像跟蹤各項(xiàng)功能。本文提出的跟蹤算法與設(shè)計(jì)的跟蹤裝置可在一定程度上解決視頻跟蹤精度低、處理速度慢的問(wèn)題,同時(shí)本視頻跟蹤裝置也可作為進(jìn)一步研究圖像處理與跟蹤控制的平臺(tái)。

2019-06-26 06:09:46

請(qǐng)教一下,基于DSP和FPGA的嵌入式控制器該如何去設(shè)計(jì)?

2021-05-06 09:16:19

彈載信息處理系統(tǒng)是一種實(shí)時(shí)嵌入式數(shù)字處理系統(tǒng),用于對(duì)彈載導(dǎo)引系統(tǒng)接收信號(hào)進(jìn)行分析處理,實(shí)現(xiàn)對(duì)目標(biāo)信號(hào)的檢測(cè)、截獲和跟蹤以及目標(biāo)信息的提取,是彈載雷達(dá)導(dǎo)引系統(tǒng)的關(guān)鍵組成部分。

2019-09-19 07:07:17

本課題通過(guò)對(duì)現(xiàn)有圖像識(shí)別技術(shù)進(jìn)行研究和分析,針對(duì)當(dāng)前DSP(數(shù)字信號(hào)處理)技術(shù)的新發(fā)展,提出了基于DSP的快速圖像識(shí)別概念。快速圖像識(shí)別技術(shù)以嵌入式系統(tǒng)為算法的實(shí)現(xiàn)平臺(tái),它結(jié)合了當(dāng)前最新的數(shù)信號(hào)處理

2014-11-05 14:43:48

本帖最后由 丫菋00 于 2019-5-23 12:46 編輯

基于FPGA 的嵌入式圖像設(shè)計(jì),一本難得的基于FPGA的數(shù)字圖像處理教材。(2019-5-22)剛剛補(bǔ)發(fā)了中文版每天上傳容量有限

2018-09-13 08:44:21

移動(dòng))的實(shí)時(shí)邊界進(jìn)行跟蹤,為后期基于FPGA的人臉位置識(shí)別,字符識(shí)別(字符在鏡頭內(nèi)任意位置)等打下基礎(chǔ)。本節(jié)顆也是走向人工智能,機(jī)器識(shí)別的重要一課。算法實(shí)現(xiàn):對(duì)于彩色圖像直接使用FPGA進(jìn)行邊界查找難度比較

2018-08-10 09:15:05

幀率提升、彩色空間轉(zhuǎn)換等處理。FPGA器件具有可重復(fù)編程的靈活性以及并行處理能力,并且隨著微處理器、專用硬件單元、DSP算法以及IP核的嵌入使其功能越來(lái)越強(qiáng)大。本系統(tǒng)的設(shè)計(jì)是基于Altera公司的EP2S60系列的開(kāi)發(fā)板,板上集成兩片SDRAM存儲(chǔ)芯片、視頻輸入接口和VGA輸出接口。

2019-09-29 08:46:06

本帖最后由 mingzhezhang 于 2012-5-23 19:28 編輯

為了提高數(shù)字圖像的處理速度,提出了用FPGA來(lái)設(shè)計(jì)嵌入式sobel邊緣檢測(cè)系統(tǒng)的方法。構(gòu)建了嵌入式邊緣檢測(cè)系統(tǒng)

2012-05-23 19:16:14

轉(zhuǎn)帖摘要: 針對(duì)嵌入式軟件無(wú)法滿足數(shù)字圖像實(shí)時(shí)處理速度問(wèn)題,提出用硬件加速器的思想,通過(guò)FPGA實(shí)現(xiàn)Sobel邊緣檢測(cè)算法。通過(guò)乒乓操作、并行處理數(shù)據(jù)和流水線設(shè)計(jì),大大提高算法的處理速度。采用模塊

2017-11-29 08:57:04

摘要:本文基于atmega16微處理器和AVRX嵌入式實(shí)時(shí)操作系統(tǒng)設(shè)計(jì)并完成了水秋千的嵌入式控制器.為實(shí)現(xiàn)高級(jí)控制策略和非線性控制理論研究提供了一個(gè)能夠運(yùn)行多任務(wù)的實(shí)驗(yàn)平臺(tái)/通過(guò)移植和裁剪,嵌入式

2009-04-27 21:41:48

速率和位置控制。算法的FPGA實(shí)現(xiàn), 使得模塊具有極低的延遲:輸出偏差或平臺(tái)運(yùn)動(dòng)參數(shù)延遲小于1幀時(shí)間,可同步輸出,也可即時(shí)輸出。輸出偏差的低延遲,大大提高系統(tǒng)動(dòng)態(tài)性能,適合于快速目標(biāo)的跟蹤 。圖像處理

2013-10-22 10:27:01

1、基于RT-Thread和N32G457的嵌入式目標(biāo)識(shí)別系統(tǒng)設(shè)計(jì) 本演示示例移植蘇州大學(xué)計(jì)算機(jī)科學(xué)與技術(shù)學(xué)院王宜懷教授團(tuán)隊(duì)的金葫蘆嵌入式人工智能:物體認(rèn)知系統(tǒng)中的代碼在N32G457上實(shí)現(xiàn)。可以識(shí)別單獨(dú)的英文字母A B C D原作者:tai-he

2022-11-30 11:36:05

的軟件構(gòu)架。SPB中的軟件IP模塊可以屏蔽底層細(xì)節(jié),為FPGA嵌入式設(shè)計(jì)的快速開(kāi)發(fā)提供便利,提高研發(fā)效率。介紹了基于SPB的FPGA嵌入式設(shè)計(jì)關(guān)鍵技術(shù),并在智能開(kāi)發(fā)平臺(tái)NanoBoard 3000上實(shí)現(xiàn)了基于SPB的嵌入式音頻處理系統(tǒng)設(shè)計(jì)。

2020-03-11 07:12:23

彈載信息處理系統(tǒng)是一種實(shí)時(shí)嵌入式數(shù)字處理系統(tǒng),用于對(duì)彈載導(dǎo)引系統(tǒng)接收信號(hào)進(jìn)行分析處理,實(shí)現(xiàn)對(duì)目標(biāo)信號(hào)的檢測(cè)、截獲和跟蹤以及目標(biāo)信息的提取,是彈載雷達(dá)導(dǎo)引系統(tǒng)的關(guān)鍵組成部分。隨著軍事技術(shù)的發(fā)展,未來(lái)

2019-08-29 06:07:24

本文在對(duì)嵌入式實(shí)時(shí)操作系統(tǒng)進(jìn)行研究的基礎(chǔ)上,完成了基于TS101DSP芯片的嵌入式實(shí)時(shí)操作系統(tǒng)的設(shè)計(jì)。

2021-04-27 06:41:31

本文使用的系統(tǒng)硬件平臺(tái)采用Samsung公司的處理器S3C2410,并以此為基礎(chǔ),在基于嵌入式Linux系統(tǒng)平臺(tái)上設(shè)計(jì)了建立圖像視頻的一種方法。

2021-06-08 06:10:16

西電移動(dòng)計(jì)算與通信團(tuán)隊(duì)招聘:嵌入式軟件開(kāi)發(fā)(專職或兼職)研究方向:工業(yè)嵌入式計(jì)算平臺(tái)開(kāi)發(fā)。需求人數(shù):1人要求:1、熟悉linux操作系統(tǒng)和嵌入式實(shí)時(shí)操作系統(tǒng),具有嵌入式linux/RTOS軟件開(kāi)發(fā)

2021-10-12 09:32:52

TOPPERS的歷史、現(xiàn)狀及其下一個(gè)十年的發(fā)展計(jì)劃和目標(biāo),以及TOPPERS在國(guó)內(nèi)的發(fā)展情況和目前基于TOPPERS成果正在進(jìn)行的工作。關(guān)鍵詞:實(shí)時(shí)操作系統(tǒng);TOPPERS;ITRON;軟件平臺(tái);嵌入式系統(tǒng)

2012-12-06 10:06:35

大多選用這種算法。硬件實(shí)現(xiàn)上,最初是采用單片DSP芯片實(shí)現(xiàn),其原理為:圖像數(shù)據(jù)實(shí)時(shí)的傳輸給DSP,DSP接收完1塊數(shù)據(jù)后,再對(duì)整塊數(shù)據(jù)進(jìn)行增強(qiáng)處理,這樣勢(shì)必會(huì)造成時(shí)間的延遲,不能滿足精確制導(dǎo)武器系統(tǒng)實(shí)時(shí)性的要求。后來(lái)硬件結(jié)構(gòu)發(fā)展為采取DSP,FPGA芯片相結(jié)合的方式。

2019-08-16 07:10:22

Altium designer在FPGA及嵌入式智能方面有哪些優(yōu)勢(shì)?怎樣運(yùn)用Altium Designer平臺(tái)實(shí)現(xiàn)FPGA的嵌入式系統(tǒng)設(shè)計(jì)?

2021-04-28 07:05:33

天基嵌入式MPP圖像處理技術(shù)有哪些功能?天基嵌入式MPP圖像處理技術(shù)的結(jié)構(gòu)是如何構(gòu)成的?

2021-06-02 06:14:12

的處理器也是行業(yè)所需。當(dāng)然在實(shí)際應(yīng)用中我們要根據(jù)系統(tǒng)的實(shí)時(shí)性能、功耗、圖像精度和算法復(fù)雜度來(lái)選擇合適的處理器。為了協(xié)助用戶搭建自己的嵌入式視覺(jué)平臺(tái)和產(chǎn)品,Xilinx聯(lián)盟合作伙伴Avnet(安富利)推出

2019-08-08 06:53:56

本文介紹一種基于嵌入式實(shí)時(shí)內(nèi)核ARTXl66的電子差速算法

2021-05-13 06:46:56

開(kāi)發(fā)圖像處理和計(jì)算機(jī)視覺(jué)系統(tǒng)并將其部署到嵌入式目標(biāo)硬件。借助 MATLAB 和 Simulink,您能夠:開(kāi)發(fā)算法和建立系統(tǒng)模型集成第三方軟件框架為目標(biāo)硬件平臺(tái)生成代碼為目標(biāo)硬件平臺(tái)生成代碼以 CPU

2021-12-04 08:00:00

和DSP為主要處理平臺(tái)。隨著人們對(duì)便攜設(shè)備的安全性要求越來(lái)越高,傳統(tǒng)的處理系統(tǒng)在功耗和處理速度及實(shí)時(shí)性上已經(jīng)不能滿足需要。 指紋識(shí)別系統(tǒng)在很大程度上依靠指紋圖像的質(zhì)量。在實(shí)際應(yīng)用中由于采集條件和采集設(shè)備

2009-09-19 09:38:11

,這種產(chǎn)品要做到小型化、高效性、低功耗,而且要處理龐大的圖像數(shù)據(jù)集,比如同時(shí)處理多個(gè)每秒60幀的實(shí)時(shí)高清視頻流。 圖1給出了設(shè)計(jì)人員通常用來(lái)創(chuàng)建嵌入式視覺(jué)應(yīng)用的流程。算法設(shè)計(jì)是整個(gè)流程中最重要的一環(huán)

2014-04-21 15:49:33

系列:基于 FPGA 的圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì)(sobel算法)

FPGA設(shè)計(jì)中 Verilog HDL實(shí)現(xiàn)基本的圖像濾波處理仿真

基于FPGA的類腦計(jì)算平臺(tái) —PYNQ 集群的無(wú)監(jiān)督圖像識(shí)別類腦計(jì)算系統(tǒng)

需要

2023-06-08 15:55:34

如題:要實(shí)現(xiàn)實(shí)時(shí)圖像識(shí)別出,開(kāi)發(fā)板采用DSP ,還是ARM dsp,還是DSP FPGA哪個(gè)?

2014-04-29 21:31:34

高性能低功耗小尺寸輕重量的嵌入式高清視頻自動(dòng)跟蹤模塊,它提供了目標(biāo)捕捉、自動(dòng)跟蹤、多目標(biāo)檢測(cè)和跟蹤、平臺(tái)控制、OSD、圖像縮放平移旋轉(zhuǎn)、電子穩(wěn)像、圖像增強(qiáng)、視頻融合、視頻壓縮存儲(chǔ)與網(wǎng)絡(luò)傳輸?shù)葟?qiáng)大功能,其

2013-09-05 11:14:16

獵頭職位:嵌入式算法工程師【上海】工作職責(zé): 1.負(fù)責(zé)傳感器相關(guān)的圖像處理,模式識(shí)別,信號(hào)處理方面的算法開(kāi)發(fā);2.負(fù)責(zé)調(diào)試、改進(jìn)相關(guān)程序,驗(yàn)證算法原型,并在嵌入式系統(tǒng)上實(shí)現(xiàn);3. 文檔歸檔和研發(fā)

2016-10-26 15:28:47

計(jì)算機(jī)相關(guān)專業(yè),碩士以上,2年以上工作經(jīng)驗(yàn);2.精通C/C++,VC++,OpenCV;3.精通Matlab,能夠快速驗(yàn)證算法原型;4.精通常用圖像處理,模式識(shí)別以及機(jī)器學(xué)習(xí)算法。 5.有在嵌入式平臺(tái)

2016-10-21 11:14:36

最近在學(xué)習(xí)嵌入式Linux,需要進(jìn)行圖像的采集和處理,現(xiàn)在有mini2440開(kāi)發(fā)板,但做圖像處理速度感覺(jué)有點(diǎn)慢,能推薦幾款合適的嵌入式處理器嗎?

2014-02-20 14:29:37

介紹了一種有目標(biāo)識(shí)別功能的圖像采集系統(tǒng),用USB 接口芯片實(shí)現(xiàn)了數(shù)據(jù)的傳輸。闡述了系統(tǒng)的硬件、固件、設(shè)備驅(qū)動(dòng)程序和應(yīng)用軟件的設(shè)計(jì)與實(shí)現(xiàn)方法。詳細(xì)介紹了目標(biāo)識(shí)別算法

2009-08-13 08:42:45 14

14 針對(duì)微型航天探測(cè)器在星空運(yùn)動(dòng)背景下對(duì)目標(biāo)識(shí)別的要求,提出一種基于圖像配準(zhǔn)與邊緣提取的差分算法。該算法將采集的連續(xù)兩幀圖像配準(zhǔn)后差分,將差分圖像二值

2009-08-15 15:10:21 15

15 提出了一種運(yùn)動(dòng)目標(biāo)識(shí)別與跟蹤系統(tǒng)的方案,給出了系統(tǒng)的原理圖和結(jié)構(gòu)框圖。重點(diǎn)論述了圖像處理的過(guò)程和算法,包括顏色模型的選擇,圖像的預(yù)處理,圖像分割,目標(biāo)的識(shí)別及

2010-07-20 16:14:33 29

29 設(shè)計(jì)一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺(tái),運(yùn)用FPGA實(shí)現(xiàn)微處理器接口設(shè)計(jì),并對(duì)圖像數(shù)據(jù)進(jìn)行簡(jiǎn)單預(yù)處理,利用DSP進(jìn)行復(fù)雜圖像處理算法和邏輯控制,實(shí)現(xiàn)圖像數(shù)據(jù)的高速傳輸

2010-12-25 17:06:54 60

60 摘要:提出了在嵌入式平臺(tái)上用CPLD實(shí)現(xiàn)實(shí)時(shí)圖像增強(qiáng)算法的解決方案,并加以實(shí)現(xiàn)。重點(diǎn)討論了經(jīng)過(guò)改進(jìn)的圖像增強(qiáng)算法以及使用CPLD實(shí)現(xiàn)的具體方法,介紹了所采用的嵌入式

2006-03-11 12:44:08 708

708

基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)

介紹了基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)。該系統(tǒng)通過(guò)兩片TMS320C6201作為系統(tǒng)計(jì)算中心,通過(guò)可重構(gòu)成的FPGA計(jì)算系統(tǒng)獲得系

2009-12-08 14:25:35 1009

1009

基于DSP+FPGA+ASIC的實(shí)時(shí)圖像處理系統(tǒng)

1.引言

隨著紅外焦平面陣列技術(shù)的快速發(fā)展,紅外成像系統(tǒng)實(shí)現(xiàn)了高幀頻、高分辨率、高可靠性及微型化,在目標(biāo)跟蹤

2010-01-13 10:39:49 1115

1115

基于DSP和FPGA的通用圖像處理平臺(tái)設(shè)計(jì)

摘要:設(shè)計(jì)一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺(tái),運(yùn)用FPGA實(shí)現(xiàn)微處理器接口設(shè)計(jì),并對(duì)圖像數(shù)據(jù)進(jìn)行簡(jiǎn)單預(yù)處理,利用DSP

2010-02-01 11:10:21 1379

1379

介紹了一種基于$3C2440硬件平臺(tái)和移動(dòng)目標(biāo)識(shí)別技術(shù)的安防監(jiān)控系統(tǒng)的總體設(shè)計(jì)方案,在嵌入式Linux平臺(tái)下實(shí)現(xiàn)視頻數(shù)據(jù)的采集、編碼與傳輸l選擇時(shí)間差分圖像檢測(cè)移動(dòng)目標(biāo)算法,實(shí)現(xiàn)視

2011-08-25 15:35:33 67

67 針對(duì)圖像處理要求運(yùn)行復(fù)雜靈活的圖像處理算法和大數(shù)據(jù)量的數(shù)據(jù)傳輸處理的要求,提出了一種基于DSP和FPGA架構(gòu)的嵌入式圖像處理系統(tǒng),簡(jiǎn)要介紹了系統(tǒng)的工作原理,詳細(xì)介紹了系統(tǒng)硬

2011-12-05 14:12:28 62

62 自動(dòng)目標(biāo)識(shí)別(ATR)算法通常包括自動(dòng)地對(duì)目標(biāo)進(jìn)行檢測(cè)、跟蹤、識(shí)別和選擇攻擊點(diǎn)等算法。戰(zhàn)場(chǎng)環(huán)境的復(fù)雜性和目標(biāo)類型的不斷增長(zhǎng)使ATR算法的運(yùn)算量越來(lái)越大,因此ATR算法對(duì)微處理器的

2012-01-17 14:53:55 1781

1781

為了提高算法效率,實(shí)時(shí)處理圖像信息,本處理系統(tǒng)是基于DSP+FPGA混用結(jié)構(gòu)設(shè)計(jì)的。業(yè)務(wù)板以FPGA為處理核心,實(shí)現(xiàn)數(shù)字視頻信號(hào)的實(shí)時(shí)圖像處理,DSP實(shí)現(xiàn)了部分的圖像處理算法和FPGA的控

2012-10-16 11:02:47 2706

2706

基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì)

2017-01-03 11:41:35 9

9 多尺度Retinex算法在自動(dòng)目標(biāo)識(shí)別中的應(yīng)用_周澤華

2017-03-19 11:29:00 0

0 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì)

2017-10-23 14:09:42 9

9 針對(duì)被局部遮擋目標(biāo)的識(shí)別困難的問(wèn)題,將目標(biāo)圖像的SIFT( Scale Invariant Feature Transform)特征矢量作為視覺(jué)單詞,應(yīng)用視覺(jué)詞匯算法,提出了基于SIFT特征視覺(jué)詞匯算法

2017-11-14 11:04:14 5

5 為了能夠更好地滿足日益擴(kuò)大的目標(biāo)識(shí)別需求,提出了一種基于改進(jìn)KD樹(shù)與RANSC算法的目標(biāo)識(shí)別算法。通過(guò)對(duì)比改進(jìn)前后KD樹(shù)匹配算法匹配SIFT特征點(diǎn)的執(zhí)行效果,很明顯的看出改進(jìn)KD樹(shù)算法的匹配效果更佳

2017-11-16 17:45:02 17

17 為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號(hào)處理器TMS320C6416)和現(xiàn)場(chǎng)可編程門陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2017-11-18 12:34:02 4034

4034

本文主要介紹了一種基于DSP+FPGA的實(shí)時(shí)圖像去霧增強(qiáng)系統(tǒng)設(shè)計(jì),FPGA通常作為一種調(diào)度使用,圖像處理算法實(shí)現(xiàn)主要靠高速處理信號(hào)處理芯片DSP完成,在跟蹤等領(lǐng)域圖像數(shù)據(jù)只需單向進(jìn)入DSP,處理后輸出相應(yīng)參數(shù)即可,在實(shí)時(shí)視頻圖像處理中大量圖像數(shù)據(jù)只需通過(guò)EMIF輸入,且輸出數(shù)據(jù)量較小可以實(shí)時(shí)完成。

2017-12-25 10:24:21 3380

3380

的可能 CNN:嵌入式平臺(tái)目標(biāo)識(shí)別的下一個(gè)前沿領(lǐng)域 配有攝像頭的智能手機(jī)、平板電腦、可穿戴設(shè)備、監(jiān)控系統(tǒng)和汽車系統(tǒng)采用智能視覺(jué)功能將這個(gè)行業(yè)帶到了一個(gè)十字路口,需要更先進(jìn)的算法來(lái)實(shí)現(xiàn)計(jì)算密集型

2018-07-12 14:55:54 426

426 了實(shí)現(xiàn)的可能 CNN:嵌入式平臺(tái)目標(biāo)識(shí)別的下一個(gè)前沿領(lǐng)域 配有攝像頭的智能手機(jī)、平板電腦、可穿戴設(shè)備、監(jiān)控系統(tǒng)和汽車系統(tǒng)采用智能視覺(jué)功能將這個(gè)行業(yè)帶到了一個(gè)十字路口,需要更先進(jìn)的算法來(lái)實(shí)現(xiàn)計(jì)算密集型

2018-07-12 16:38:45 153

153 工作時(shí)鐘下,處理384×288像素的紅外圖像能夠達(dá)到400幀/秒以上的標(biāo)記速度,足夠滿足實(shí)時(shí)目標(biāo)識(shí)別系統(tǒng)的要求。處理速度可以滿足大部分實(shí)時(shí)目標(biāo)識(shí)別系統(tǒng)的要求。該算法同樣可以軟件編程方式應(yīng)用于嵌入式DSP系統(tǒng)中。

2018-11-14 10:07:00 6259

6259

利用模板匹配方法,采用基于遺傳算法的圖像識(shí)別技術(shù),完成了對(duì)圖像目標(biāo)識(shí)別的算法驗(yàn)證。在此基礎(chǔ)上進(jìn)行了基于該算法的圖像識(shí)別系統(tǒng)的FPGA實(shí)現(xiàn),并在相關(guān)驗(yàn)證平臺(tái)進(jìn)行了硬件仿真與時(shí)序分析。實(shí)驗(yàn)結(jié)果表明。所設(shè)計(jì)的圖像識(shí)別電路具有較高的識(shí)別精度和較快的識(shí)別速度。

2021-01-26 15:02:00 13

13 FPGA,通過(guò)并行處理結(jié)構(gòu)及流水線技術(shù),可實(shí)時(shí)處理每秒50幀780×582×12bits的可見(jiàn)光圖像。在處理視頻的過(guò)程中,由前一幀圖像的直方圖信息,來(lái)增強(qiáng)后一幀圖像。理論分析和實(shí)驗(yàn)結(jié)果均表明,該算法克服了直方圖均衡及平臺(tái)直方圖均衡增強(qiáng)

2021-02-03 15:21:00 10

10 出了四核心嵌入式并行處理器FPEP的結(jié)構(gòu)設(shè)計(jì)并建立了FPGA驗(yàn)證平臺(tái).為了對(duì)多核處理器平臺(tái)性能進(jìn)行評(píng)測(cè),提出了基于OpenMP的3種可行的圖像處理領(lǐng)域的經(jīng)典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 基于DSP的嵌入式圖像識(shí)別系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)總結(jié)(基于linux的嵌入式開(kāi)發(fā)環(huán)境的搭建過(guò)程)-該文檔為基于DSP的嵌入式圖像識(shí)別系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 11:37:15 25

25 基于ARM與FPGA的嵌入式實(shí)時(shí)圖像處理平臺(tái)(嵌入式開(kāi)發(fā)流程包含哪些步驟和內(nèi)容)-該文檔為基于ARM與FPGA的嵌入式實(shí)時(shí)圖像處理平臺(tái)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 11:41:52 5

5

?

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論