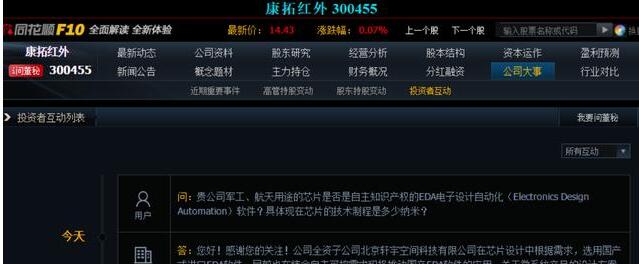

作為貫穿于集成電路設計、制造、封測等環節的戰略基礎支柱之一,EDA已成為國內無法繞開的“卡脖子”環節,也是國內半導體業必須攻克的環節。

?

近年來,隨著國家政策、資本以及生態的多重利好助力,國內EDA產業步入快車道,國產EDA工具在設計、制造和封裝領域多點開花。作為自主創新的高性能工業軟件及解決方案提供商,上海合見工業軟件集團有限公司(以下簡稱“合見工軟”)正式運營一年多,已經發布了多款EDA產品和解決方案,包括數字仿真器、FPGA原型驗證系統、仿真調試工具、驗證效率提升平臺、系統級IP驗證方案、先進封裝協同設計環境、電子設計數據管理平臺等,在高難度的數字驗證、協同設計等領域率先實現了突圍。

?

應對設計新需求 深化產品布局

?

后摩爾時代諸多新興應用的興起,如AI、GPGPU、HPC等芯片開發已成為市場熱點,這對芯片的規模、性能的要求日益走高。合見工軟CTO賀培鑫表示:“為了滿足對復雜功能的需求,我們可以看到市場上的大部分芯片采用多核結構;同時隨著工藝節點已趨近極限,晶圓廠已經在探索是否能突破2納米甚至1納米的標線。為了追求PPA和成本的最優解,采用多Die的Chiplet成為芯片設計的主流結構。因此,多核多Die是時下芯片設計的趨勢。”

賀培鑫指出,合見工軟選擇驗證作為EDA工具的首先突破點,也是綜合考量了芯片設計公司在這一趨勢下面臨的諸多復雜難題。

?

第一,驗證復雜度呈幾何倍數的增長。“舉個例子,我們可以看到業內的大規模SoC已從過去的8核、16核發展到現在的64核,規模一直在翻倍。由于多核復用,設計復雜度并不會隨著規模的增長而翻倍;然而多核之間的互連使得驗證的復雜度隨著規模成比例增長。”

第二,驗證的成本(時間、人力)高速增長。“過去開發一款芯片,一般2個設計工程師需要配1個驗證工程師;現在開發一款大規模芯片,1個設計工程師要配2-3個驗證工程師,同時驗證的時間也更長。”

?

第三,驗證工具越來越多樣化。“比如在芯片設計初期,采用數字仿真器一秒鐘跑一個時鐘周期,隨著設計推進到下一階段,我們需要更高的頻率來覆蓋更大的設計規模,這時我們需要采用不同的驗證工具,原型驗證系統一秒鐘可以跑一百萬個時鐘周期,這樣就快了一百萬倍。再如,設計中的某個區塊在很多測試用例下出現的bug特別多,此時就需要形式驗證工具窮盡所有可能性去修復這些bug。因而一個設計在不同的場景下是需要多款驗證工具來支撐的。”

?

只有解決驗證上的復雜難題才能幫助國內芯片公司設計出具有國際競爭力的產品。此外,僅考慮多核是不夠的,為了對芯片開發實現完整的EDA工具支撐,對于采用多Die結構的Chiplet,合見工軟也在先進封裝設計、板級設計領域進行了相應的布局。

?

實現新突破 彰顯新價值

?

要實現國產EDA驗證工具的突破,賀培鑫認為,最重要的是要在規模、性能和自動化層面全面提升。合見工軟去年推出了FPGA原型驗證系統,今年6月發布了UV APS全新功能升級版。

?

從規模上看,相比業界同類工具支持8-48顆FPGA容量,UV APS能夠支持高達100顆VU19P FPGA的級聯。

?

從性能上看,APS Compiler采用全路徑的時序驅動(Timing Driven)分割技術,相比一般只考慮切面大小(Cut-size Driven)的分割技術,APS Compiler可以充分考慮到FPGA間的連線和時序路徑之間的關系,通過采用TDM(時分復用)技術,識別并考慮每一根穿過FPGA的信號所在時鐘域的頻率,選擇最佳的時分復用比例,優化FPGA之間的跳數,實現邏輯電路運行速度最快的結果,TDM的范圍可以做到1-1024。

?

從自動化程度來看,對于FPGA不能支持的設計單元,比如多端口存儲(Multi-port Memory)、多維數組、跨模塊引用(XMR)、三態門(Tri-state)等,業界一些主流工具會要求用戶修改RTL代碼,而UV APS則可實現自動化轉換。

?

賀培鑫談到:“除此之外,還有很多值得探索的技術點。我們熟知的硬件仿真技術有基于FPGA和ASIC兩種,后者的編譯時間相對較快,因為ASIC只需要把RTL設計轉換成處理器的指令;而前者的仿真運行速度更快,因為FPGA可以迅速啟動Linux,且功耗小;ASIC通常需要采用水冷卻的辦法,價格昂貴,約為FPGA的四倍。因此,在設計不夠成熟、規模較小的階段,需要頻繁迭代,ASIC原型驗證技術由于其編譯時間短,優勢會更突出;在設計達到一定成熟度、規模較大的階段,FPGA原型驗證技術由于其仿真運行速度快,會更具優勢。所以說沒有哪一種技術具有全面的絕對性優勢,我們需要繼續探索更優化的方法,打磨更好的工具,以支持客戶開發更高性能的產品。”

?

另外,要應對Chiplet在先進封裝的挑戰,打破在復雜多維空間系統級設計互連,實現數據的一致性和信號、電源、熱、應力的完整性,合見工軟在去年發布了先進封裝協同設計環境之后,今年6月又推出了UVI功能增強版。

?

賀培鑫指出,此次發布的增強版首次真正意義上實現了系統級Sign-off功能,可在同一設計環境中導入多種格式的IC、Interposer、Package和PCB數據,支持全面的系統互連一致性檢查(System-Level LVS),同時在檢查效率、圖形顯示、靈活度與精度上都有大幅提升。

UVI能夠基于物理、圖形和數據等信息,根據不同應用需求,自動產生系統級互連關系網表、互連錯誤信息、網絡斷開類型及互連疊層信息等關鍵報告。這也使得其在處理大規模互連管腳數據時十分迅速,無論是命名一致性檢查、鏈路通斷檢查還是管腳缺失互連檢查,對于60萬Pin的規模都可以在5秒內完成,并且可以支持一對多Pin的基于面積算法的互連檢查。“開發人員利用UVI可以簡化設計流程、提升工作效率、提高設計質量、精準定位設計錯誤,并覆蓋所有節點和網絡的檢查。”

?

夯實產品技術 培養EDA人才

?

賀培鑫認為:“一款工具要獲得市場認可是需要時間的,用戶希望獲得性能穩定的產品,因此我們在推出新工具的同時,還會在已發布的產品上做持續優化升級,和國內用戶成為緊密的共贏伙伴,打造世界級芯片。業界主流的工具雖然相對比較成熟,但有一定的歷史包袱,經過二三十年的迭代相當于是疊床架屋負重前行。合見工軟可以基于最新的方法論從頭打造產品,在這樣的基礎上做優化會更快,因此我們有信心趕上并超過業界成熟工具。”

?

圍繞EDA產品路線,合見工軟將在驗證全流程領域持續發力,FPGA原型驗證系統預計在年底前進一步提升性能,在硬件仿真器、調試領域加快布局;在先進封裝設計領域,協同設計優化持續進階。

?

在培養EDA人才方面,“合見工軟的團隊中有很多人在全球EDA領域打拼了二三十年,積累了很多前沿技術和行業實踐經驗,我們很希望把這些經驗分享給國內熱愛半導體行業的莘莘學子,為國內培養EDA專業人才。我非常愿意貢獻自己的一份力量,幫助他們學習、快速成長,打造EDA更好的未來。”

?

近年來,隨著國家政策、資本以及生態的多重利好助力,國內EDA產業步入快車道,國產EDA工具在設計、制造和封裝領域多點開花。作為自主創新的高性能工業軟件及解決方案提供商,上海合見工業軟件集團有限公司(以下簡稱“合見工軟”)正式運營一年多,已經發布了多款EDA產品和解決方案,包括數字仿真器、FPGA原型驗證系統、仿真調試工具、驗證效率提升平臺、系統級IP驗證方案、先進封裝協同設計環境、電子設計數據管理平臺等,在高難度的數字驗證、協同設計等領域率先實現了突圍。

?

應對設計新需求 深化產品布局

?

后摩爾時代諸多新興應用的興起,如AI、GPGPU、HPC等芯片開發已成為市場熱點,這對芯片的規模、性能的要求日益走高。合見工軟CTO賀培鑫表示:“為了滿足對復雜功能的需求,我們可以看到市場上的大部分芯片采用多核結構;同時隨著工藝節點已趨近極限,晶圓廠已經在探索是否能突破2納米甚至1納米的標線。為了追求PPA和成本的最優解,采用多Die的Chiplet成為芯片設計的主流結構。因此,多核多Die是時下芯片設計的趨勢。”

賀培鑫指出,合見工軟選擇驗證作為EDA工具的首先突破點,也是綜合考量了芯片設計公司在這一趨勢下面臨的諸多復雜難題。

?

第一,驗證復雜度呈幾何倍數的增長。“舉個例子,我們可以看到業內的大規模SoC已從過去的8核、16核發展到現在的64核,規模一直在翻倍。由于多核復用,設計復雜度并不會隨著規模的增長而翻倍;然而多核之間的互連使得驗證的復雜度隨著規模成比例增長。”

第二,驗證的成本(時間、人力)高速增長。“過去開發一款芯片,一般2個設計工程師需要配1個驗證工程師;現在開發一款大規模芯片,1個設計工程師要配2-3個驗證工程師,同時驗證的時間也更長。”

?

第三,驗證工具越來越多樣化。“比如在芯片設計初期,采用數字仿真器一秒鐘跑一個時鐘周期,隨著設計推進到下一階段,我們需要更高的頻率來覆蓋更大的設計規模,這時我們需要采用不同的驗證工具,原型驗證系統一秒鐘可以跑一百萬個時鐘周期,這樣就快了一百萬倍。再如,設計中的某個區塊在很多測試用例下出現的bug特別多,此時就需要形式驗證工具窮盡所有可能性去修復這些bug。因而一個設計在不同的場景下是需要多款驗證工具來支撐的。”

?

只有解決驗證上的復雜難題才能幫助國內芯片公司設計出具有國際競爭力的產品。此外,僅考慮多核是不夠的,為了對芯片開發實現完整的EDA工具支撐,對于采用多Die結構的Chiplet,合見工軟也在先進封裝設計、板級設計領域進行了相應的布局。

?

實現新突破 彰顯新價值

?

要實現國產EDA驗證工具的突破,賀培鑫認為,最重要的是要在規模、性能和自動化層面全面提升。合見工軟去年推出了FPGA原型驗證系統,今年6月發布了UV APS全新功能升級版。

?

從規模上看,相比業界同類工具支持8-48顆FPGA容量,UV APS能夠支持高達100顆VU19P FPGA的級聯。

?

從性能上看,APS Compiler采用全路徑的時序驅動(Timing Driven)分割技術,相比一般只考慮切面大小(Cut-size Driven)的分割技術,APS Compiler可以充分考慮到FPGA間的連線和時序路徑之間的關系,通過采用TDM(時分復用)技術,識別并考慮每一根穿過FPGA的信號所在時鐘域的頻率,選擇最佳的時分復用比例,優化FPGA之間的跳數,實現邏輯電路運行速度最快的結果,TDM的范圍可以做到1-1024。

?

從自動化程度來看,對于FPGA不能支持的設計單元,比如多端口存儲(Multi-port Memory)、多維數組、跨模塊引用(XMR)、三態門(Tri-state)等,業界一些主流工具會要求用戶修改RTL代碼,而UV APS則可實現自動化轉換。

?

賀培鑫談到:“除此之外,還有很多值得探索的技術點。我們熟知的硬件仿真技術有基于FPGA和ASIC兩種,后者的編譯時間相對較快,因為ASIC只需要把RTL設計轉換成處理器的指令;而前者的仿真運行速度更快,因為FPGA可以迅速啟動Linux,且功耗小;ASIC通常需要采用水冷卻的辦法,價格昂貴,約為FPGA的四倍。因此,在設計不夠成熟、規模較小的階段,需要頻繁迭代,ASIC原型驗證技術由于其編譯時間短,優勢會更突出;在設計達到一定成熟度、規模較大的階段,FPGA原型驗證技術由于其仿真運行速度快,會更具優勢。所以說沒有哪一種技術具有全面的絕對性優勢,我們需要繼續探索更優化的方法,打磨更好的工具,以支持客戶開發更高性能的產品。”

?

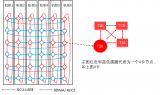

另外,要應對Chiplet在先進封裝的挑戰,打破在復雜多維空間系統級設計互連,實現數據的一致性和信號、電源、熱、應力的完整性,合見工軟在去年發布了先進封裝協同設計環境之后,今年6月又推出了UVI功能增強版。

?

賀培鑫指出,此次發布的增強版首次真正意義上實現了系統級Sign-off功能,可在同一設計環境中導入多種格式的IC、Interposer、Package和PCB數據,支持全面的系統互連一致性檢查(System-Level LVS),同時在檢查效率、圖形顯示、靈活度與精度上都有大幅提升。

UVI能夠基于物理、圖形和數據等信息,根據不同應用需求,自動產生系統級互連關系網表、互連錯誤信息、網絡斷開類型及互連疊層信息等關鍵報告。這也使得其在處理大規模互連管腳數據時十分迅速,無論是命名一致性檢查、鏈路通斷檢查還是管腳缺失互連檢查,對于60萬Pin的規模都可以在5秒內完成,并且可以支持一對多Pin的基于面積算法的互連檢查。“開發人員利用UVI可以簡化設計流程、提升工作效率、提高設計質量、精準定位設計錯誤,并覆蓋所有節點和網絡的檢查。”

?

夯實產品技術 培養EDA人才

?

賀培鑫認為:“一款工具要獲得市場認可是需要時間的,用戶希望獲得性能穩定的產品,因此我們在推出新工具的同時,還會在已發布的產品上做持續優化升級,和國內用戶成為緊密的共贏伙伴,打造世界級芯片。業界主流的工具雖然相對比較成熟,但有一定的歷史包袱,經過二三十年的迭代相當于是疊床架屋負重前行。合見工軟可以基于最新的方法論從頭打造產品,在這樣的基礎上做優化會更快,因此我們有信心趕上并超過業界成熟工具。”

?

圍繞EDA產品路線,合見工軟將在驗證全流程領域持續發力,FPGA原型驗證系統預計在年底前進一步提升性能,在硬件仿真器、調試領域加快布局;在先進封裝設計領域,協同設計優化持續進階。

?

在培養EDA人才方面,“合見工軟的團隊中有很多人在全球EDA領域打拼了二三十年,積累了很多前沿技術和行業實踐經驗,我們很希望把這些經驗分享給國內熱愛半導體行業的莘莘學子,為國內培養EDA專業人才。我非常愿意貢獻自己的一份力量,幫助他們學習、快速成長,打造EDA更好的未來。”

電子發燒友App

電子發燒友App

評論