ASIC和FPGA具有不同的價(jià)值主張,在作出選擇前必須仔細(xì)評(píng)估。兩種種技術(shù)對(duì)比。這里介紹了ASIC和FPGA 的優(yōu)勢(shì)與劣勢(shì)。

2011-03-31 17:30:09 5382

5382

使用邏輯分析儀Acute TravelLogic Analyzer進(jìn)行SPI NAND驅(qū)動(dòng)開發(fā)調(diào)試

2023-06-08 11:13:50 2997

2997

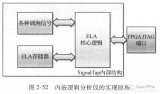

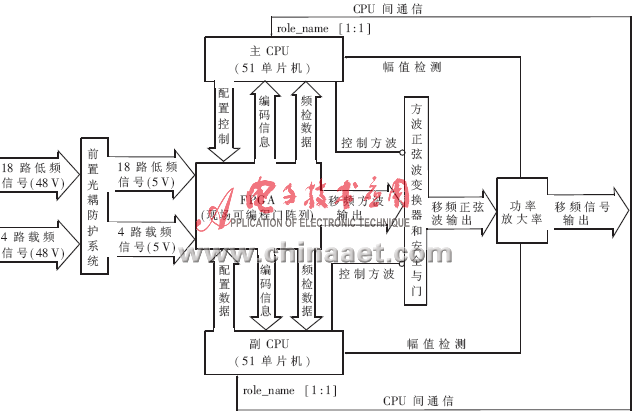

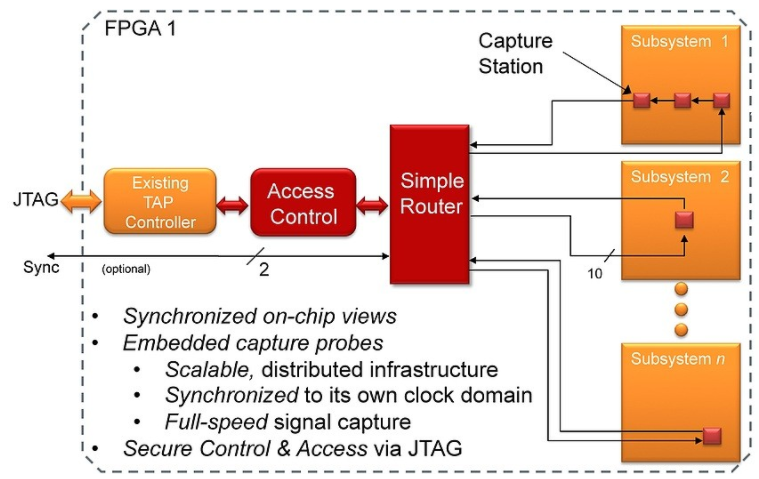

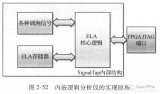

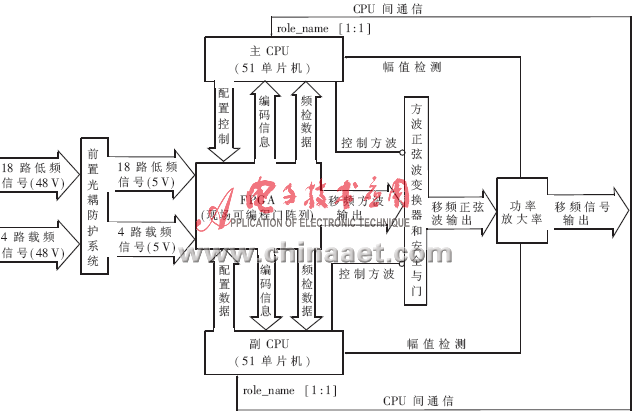

其中待測(cè)設(shè)計(jì)就是我們整個(gè)的邏輯設(shè)計(jì)模塊,在線邏輯分析儀也同樣是在FPGA設(shè)計(jì)中。通過一個(gè)或多個(gè)探針來采集希望觀察的信號(hào)。然后通過JTAG接口,將捕獲到的數(shù)據(jù)通過下載器回傳給我們的用戶界面,以便我們進(jìn)行觀察。

2023-07-25 09:52:58 503

503

在日常FPGA開發(fā)過程中,邏輯代碼設(shè)計(jì)完成后,為了驗(yàn)證代碼邏輯的正確性,優(yōu)先使用邏輯仿真(modesim)進(jìn)行驗(yàn)證。仿真驗(yàn)證通過后進(jìn)行板級(jí)驗(yàn)證時(shí),使用邏輯分析儀進(jìn)行分析和驗(yàn)證邏輯是否正確。FPGA

2023-10-01 17:08:00 1454

1454

對(duì)于FPGA調(diào)試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環(huán)境下進(jìn)行仿真和調(diào)試,開發(fā)板類型EP4CE15F17。

2024-01-12 09:34:14 785

785

原型驗(yàn)證過程中的ASIC到FPGA的代碼是怎樣進(jìn)行轉(zhuǎn)換的?

2021-05-08 09:16:18

進(jìn)行重新編程。 2、開發(fā)流程區(qū)別: FPGA開發(fā)是利用HDL和quartus、vivado等EDA工具,重新配置(configure)芯片的功能,而ASIC通常都具有較少的可重配置能力。 ASIC

2020-12-01 17:41:49

ASIC技術(shù)過時(shí)的報(bào)道是不成熟的。新的ASIC產(chǎn)品的數(shù)目可能有大幅度下降,但其銷售額仍然相當(dāng)高,尤其是在亞太區(qū)。此外,采用混合式方法,如結(jié)構(gòu)化ASIC,也為該技術(shù)注入了新的活力。同時(shí),FPGA(和其他可編程邏輯器件)也在發(fā)揮作用,贏得了重要的大眾市場(chǎng),并從低端應(yīng)用不斷向上發(fā)展。

2019-07-19 06:24:30

with Tcl...........................................953.9 Gate Clock 處理............................................993.10 多片 FPGA 驗(yàn)證

2015-09-18 15:26:25

FPGA 驗(yàn)證可以說就完成了 ASIC 整套流程的 50~80%。從設(shè)計(jì)成本來考慮,小批量上 FPGA 占優(yōu),大批量時(shí),ASIC 占優(yōu)。FPGA 本身就是一個(gè)芯片,只是你可以通過編程的方式修改內(nèi)部邏輯連接

2020-09-25 11:34:41

。FPGA本身就是一個(gè)芯片,只是你可以通過編程的方式修改內(nèi)部邏輯連接和配置實(shí)現(xiàn)自己想要的功能。實(shí)現(xiàn)ASIC,就如從一張白紙開始,你得有代碼,之后綜合,之后布局,布線,得到GDSII后去流片。比速度相同的工藝

2017-09-02 22:24:53

ASIC原本就是專門為某一項(xiàng)功能開發(fā)的專用集成芯片,比如你看攝像頭里面的芯片,小小的一片,集成度很低,成本很低,可是夠用了。一個(gè)山寨攝像頭賣才賣 30塊,買一片ARM多少錢?后來ASIC發(fā)展了一些

2021-11-24 07:09:18

ASIC是專用集成電路設(shè)計(jì),FPGA是可編程邏輯陣列,DSP和單片機(jī)(MCU?)是不是有點(diǎn)像?這四個(gè)我只接觸過FPGA,就是自己布置邏輯單元,可以使用IP核,最后下到開發(fā)板驗(yàn)證。現(xiàn)在我想問:如果我要實(shí)現(xiàn)一個(gè)電子系統(tǒng),這四個(gè)方案有什么區(qū)別?鑒于天朝的本科其實(shí)沒講什么東西,所以到現(xiàn)在沒搞清。。。

2015-09-21 11:34:58

擴(kuò)展性較好,可以通過增加芯片數(shù)量或使用更大容量的芯片來滿足更高的性能需求。而ASIC的可擴(kuò)展性相對(duì)較差,需要重新設(shè)計(jì)和制造。

驗(yàn)證和調(diào)試 :FPGA的驗(yàn)證和調(diào)試過程相對(duì)簡(jiǎn)單,可以在系統(tǒng)級(jí)進(jìn)行仿真和測(cè)試。而

2024-02-22 09:54:36

ASIC領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。設(shè)計(jì)師可以根據(jù)需要通過可編輯的連接把FPGA內(nèi)部的邏輯塊連接起來,就好像一個(gè)電路試驗(yàn)板被放在了

2017-06-12 15:56:59

FPGA與ASIC(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-10 11:34:28

比PCB板上的一些分立元器件。PCB通過導(dǎo)線將具有相關(guān)電氣特性的信號(hào)相連接,FPGA也需要通過內(nèi)部連線將相關(guān)的邏輯節(jié)點(diǎn)導(dǎo)通。PCB上的信號(hào)通過任何一個(gè)元器件都會(huì)產(chǎn)生一定的延時(shí),FPGA的信號(hào)通過邏輯門傳輸

2015-07-09 21:54:41

的板級(jí)調(diào)試方法有很多,借助于常規(guī)的示波器和邏輯分析儀的調(diào)試方法是最典型的手段。如圖10.1所示,基于傳統(tǒng)的臺(tái)式示波器或邏輯分析儀進(jìn)行板級(jí)調(diào)試有著諸多的不便,相對(duì)于設(shè)計(jì)電路深藏在芯片內(nèi)部的FPGA

2015-09-02 18:39:49

標(biāo)準(zhǔn),使用FPGA比ASIC更有競(jìng)爭(zhēng)力。●各種仿真驗(yàn)證系統(tǒng),由于工藝的提升,流片成本也不斷攀升,而在流片前使用FPGA做前期的驗(yàn)證已成為非常流行的做法。●片上系統(tǒng),如當(dāng)下炒得火熱的Soc FPGA。圖1.5 FPGA應(yīng)用精彩紛呈 `

2015-03-24 11:09:11

如何得到LUT與REG的使用比例?如何分析FPGA芯片上的組合邏輯(LUT)和時(shí)序邏輯(REG)的利用率?

2021-09-17 07:01:26

FPGA硬件系統(tǒng)的調(diào)試方法在調(diào)試FPGA電路時(shí)要遵循一定的原則和技巧,才能減少調(diào)試時(shí)間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進(jìn)行FPGA硬件系統(tǒng)的調(diào)試。(1)首先在焊接硬件電路時(shí),只焊接

2012-08-12 11:52:54

處理器讀出。不需要占用大量邏輯資源去調(diào)用邏輯分析儀,就可以通過處理器的串口連接計(jì)算機(jī)打印出來。調(diào)試過程中,如果發(fā)現(xiàn)某些模塊有輸入?yún)s沒輸出,或者是輸入個(gè)數(shù)與輸出個(gè)數(shù)不匹配,打印出所有計(jì)數(shù),就可以很快定位

2018-06-07 17:57:14

調(diào)試FPGA時(shí),TD軟件是否支持內(nèi)部邏輯分析(抓波形)功能?

2023-08-11 10:32:27

使用PrimeTIme進(jìn)行時(shí)序分析,滿足設(shè)計(jì)要求后即可進(jìn)行FPGA芯片投片前的最終物理驗(yàn)證。6)調(diào)試與加載配置設(shè)計(jì)開發(fā)的最后步驟就是在線調(diào)試或者將生成的配置文件寫入芯片中進(jìn)行測(cè)試。在ISE中使用iMPACT。

2021-06-24 08:00:01

成為基本的測(cè)試工具。 邏輯分析儀是利用時(shí)鐘從測(cè)試設(shè)備上采集和顯示數(shù)字信號(hào)的儀器,最主要作用在于時(shí)序判定。由于邏輯分析儀不像示波器那樣有許多電壓等級(jí),通常只顯示兩個(gè)電壓(邏輯1和0),因此設(shè)定了參考電壓

2017-09-28 09:30:56

邏輯分析儀在通訊協(xié)議分析上的應(yīng)用 前言 在科技時(shí)代里越來越多的電子裝置出現(xiàn),也越來越多的裝置電子化,而在這些許許多多的裝置就會(huì)需要相互溝通與控制以及傳遞

2010-04-26 14:35:11

和相關(guān)工具,即可通過互聯(lián)網(wǎng)進(jìn)行遠(yuǎn)程控制,從目標(biāo)文件格式中提取源碼和符號(hào),而且處理器可運(yùn)行各種控制操作。邏輯分析儀的分類目前市場(chǎng)上邏輯分析儀有兩類,一類是獨(dú)立式邏輯分析儀,主要供應(yīng)商有是德科技和泰克

2017-08-07 10:27:22

和相關(guān)工具,即可通過互聯(lián)網(wǎng)進(jìn)行遠(yuǎn)程控制,從目標(biāo)文件格式中提取源碼和符號(hào),而且處理器可運(yùn)行各種控制操作。邏輯分析儀的分類目前市場(chǎng)上邏輯分析儀有兩類,一類是獨(dú)立式邏輯分析儀,主要供應(yīng)商有是德科技和泰克

2017-08-18 10:06:38

先后順序逐一讀出信息,按設(shè)定的顯示方式進(jìn)行被測(cè)量的顯示。 邏輯分析儀的顯示形式 邏輯分析儀將被測(cè)數(shù)據(jù)信號(hào)用數(shù)字形式寫入存儲(chǔ)器后,可以根據(jù)需要通過控制電路將內(nèi)存中的全部或部分?jǐn)?shù)據(jù)穩(wěn)定的顯示在屏幕上。通常有以下

2016-01-11 17:10:27

,且在邏輯分析儀上增加模擬輸入通道也成為一種趨勢(shì)。邏輯分析儀的作用邏輯分析儀,從字面理解就知道它是一種分析數(shù)字信號(hào)邏輯時(shí)序的儀器。在數(shù)字電路里,信號(hào)是通過有序的0和1二進(jìn)制編碼傳輸,當(dāng)“序”出現(xiàn)紊亂或

2016-08-23 16:31:00

摘要:邏輯分析儀作為基礎(chǔ)儀器,應(yīng)該在基礎(chǔ)數(shù)字電路教學(xué)中得到廣泛應(yīng)用。本文介紹了基于FPGA的液晶顯示控制設(shè)計(jì)方案,通過使用OLA2032B邏輯分析儀,對(duì)控制線進(jìn)行監(jiān)測(cè)與分析,保證設(shè)計(jì)方案的準(zhǔn)確性

2017-10-19 09:07:43

設(shè)計(jì)。 現(xiàn)代ASIC常包含整個(gè)32-bit處理器,類似ROM、RAM、EEPROM、Flash的存儲(chǔ)單元和其他模塊. 這樣的ASIC常被稱為SoC(片上系統(tǒng))。 FPGA是ASIC的近親,一般通過

2012-02-27 17:46:03

主板、4.3寸TFT屏、矩陣鍵盤、紅外遙控外設(shè)。設(shè)計(jì)使用FPGA采集10路數(shù)字波形數(shù)據(jù),并存儲(chǔ)在FPGA片上緩存RAM中,然后使用4.3寸TFT觸摸液晶顯示組件進(jìn)行波形顯示。整個(gè)邏輯分析儀系統(tǒng)可使

2020-02-17 18:16:57

FPGA(Field-Program](一)FPGA的工作原理FPGA一般來說比ASIC(專用集成芯片)的速度要慢,無法完成復(fù)雜的設(shè)計(jì),但是功耗較低。但是]FPGA采用了邏輯單元陣列LCA

2019-08-11 04:30:00

調(diào)試核, 通過JTAG 硬核組件將采集信號(hào)發(fā)送到IDE進(jìn)行調(diào)試。上一篇演示了LED流水燈,這一篇我們基于此進(jìn)行在線邏輯分析儀調(diào)試體驗(yàn)。 過程菜單欄 Tools->Inserter 右下角點(diǎn)擊

2023-02-05 21:40:57

工程師使用最多的儀器,示波器主要用來觀察信號(hào)的模擬特性,如邊沿時(shí)間、電壓幅度、是否有寄生干擾等。而邏輯分析儀主要測(cè)量數(shù)字電路,因?yàn)閿?shù)字電路固有的特性,邏輯分析儀對(duì)電壓的具體值和被測(cè)信號(hào)的一些模擬特性都不進(jìn)行

2017-10-13 09:23:54

置邏輯模塊CLB(Confi gurable logic Block)線(Internet)三個(gè)部分。FPGA的基本特點(diǎn)主要有:1) 采用FPGA設(shè)計(jì)ASIC電路,用戶不需要投片生產(chǎn),就能得到合用

2018-02-26 10:10:07

[導(dǎo)讀]什么是FPGA,單片機(jī),DSP,ASIC?你真的知道嗎?ASIC原本就是專門為某一項(xiàng)功能開發(fā)的專用集成芯片,比如你看攝像頭里面的芯片,小小的一片,集成度很低,成本很低,可是夠用了。一個(gè)山寨

2021-07-16 08:13:27

Integrated Circuits縮寫,即專用集成電路,是指應(yīng)特定用戶要求和特定電子系統(tǒng)的需要而設(shè)計(jì)、制造的集成電路。目前用CPLD(復(fù)雜可編程邏輯器件)和FPGA(現(xiàn)場(chǎng)可編程邏輯陣列)來進(jìn)行ASIC設(shè)計(jì)是最為

2009-10-05 16:32:12

)采用FPGA設(shè)計(jì)ASIC電路,用戶不需要投片生產(chǎn),就能得到合用的芯片。2)FPGA可做其它全定制或半定制ASIC電路的中試樣片。3)FPGA內(nèi)部有豐富的觸發(fā)器和I/O引腳。4)FPGA是ASIC電路

2016-12-13 15:22:16

)采用FPGA設(shè)計(jì)ASIC電路,用戶不需要投片生產(chǎn),就能得到合用的芯片。2)FPGA可做其它全定制或半定制ASIC電路的中試樣片。3)FPGA內(nèi)部有豐富的觸發(fā)器和I/O引腳。4)FPGA是ASIC電路

2016-12-13 18:12:57

,分析電路設(shè)計(jì)(硬件設(shè)計(jì)和軟件設(shè)計(jì)) 中的錯(cuò)誤,邏輯分析儀是設(shè)計(jì)中不可缺少的設(shè)備,通過它,可以迅速地定位錯(cuò)誤,解決問題,達(dá)到事半功倍的效果。 邏輯分析儀是利用時(shí)鐘從測(cè)試設(shè)備上采集和顯示數(shù)字信號(hào)的儀器

2010-04-26 14:23:57

在 FPGA、GPU 或 ASIC 控制的系統(tǒng)板上,僅有為數(shù)不多的幾種電源管理相關(guān)的設(shè)計(jì)挑戰(zhàn),但是由于需要反復(fù)調(diào)試,所以這類挑戰(zhàn)可能使系統(tǒng)的推出時(shí)間嚴(yán)重滯后。

2019-10-09 06:21:11

在 FPGA、GPU 或 ASIC 控制的系統(tǒng)板上,僅有為數(shù)不多的幾種電源管理相關(guān)的設(shè)計(jì)挑戰(zhàn),但是由于需要反復(fù)調(diào)試,所以這類挑戰(zhàn)可能使系統(tǒng)的推出時(shí)間嚴(yán)重滯后。

2019-09-30 06:59:24

0.5kb-2kb左右。而FPGA片上macro IP(RAMB18E1)提供的BRAM/FIFO 的單位尺寸為18kb,顯著地大于scratchpad的需求。 于是這個(gè)scratchpad在FPGA上的實(shí)現(xiàn)

2023-03-28 11:14:04

摘要介紹一種16通道便攜式邏輯分析儀,通過FPGA將高速數(shù)據(jù)采樣并緩存,采用USB控制芯片和FPCA協(xié)同控制將數(shù)據(jù)通過USB接口發(fā)送到電腦的上位機(jī)上顯示,簡(jiǎn)化了以往邏輯分析儀硬件電路部分,降低

2019-06-18 07:56:45

。

用戶使用FPGA時(shí),可以通過硬件描述語言(Verilog或VHDL),完成的電路設(shè)計(jì),然后對(duì)FPGA進(jìn)行“編程”(燒寫),將設(shè)計(jì)加載到FPGA上,實(shí)現(xiàn)對(duì)應(yīng)的功能。

加電時(shí),FPGA將EPROM

2024-01-23 19:08:55

使設(shè)計(jì)修改和產(chǎn)品升級(jí)變得十分方便,而且極大地提高了電子系統(tǒng)的靈活性和通用能力。 目前集成度已高達(dá) 200 萬門/片,它將掩膜 ASIC 集成度高的優(yōu)點(diǎn)和可編程邏輯器件設(shè)計(jì)生產(chǎn)方便的特點(diǎn)結(jié)合在一起,特別

2019-02-26 10:08:08

進(jìn)行無數(shù)次的寫入,所以基于SRAM技術(shù)的FPGA可以進(jìn)行無限次編程。但是,SRAM具有數(shù)據(jù)易失性的特點(diǎn),即一斷電,其原有的邏輯功能將消失,所以在使用這類FPGA時(shí)外部需要一個(gè)PROM保存編程數(shù)據(jù),上電后

2021-07-13 08:00:00

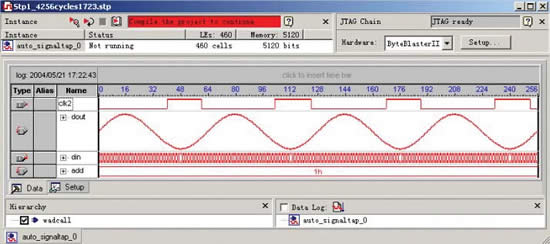

今天FPGA的高容量,很多元件可以集成到一個(gè)器件中,但邏輯分析儀不能檢測(cè)到設(shè)計(jì)內(nèi)部的信號(hào)。SignalTap II邏輯分析儀是一個(gè)系統(tǒng)級(jí)調(diào)試工具,它可在一個(gè)系統(tǒng)級(jí)可編程芯片(SoPC)上捕獲和顯示實(shí)時(shí)

2012-02-27 15:18:09

我的設(shè)計(jì)完全在Verilog中,并且已經(jīng)使用Spartan FPGA進(jìn)行了測(cè)試。我將源代碼提供給ASIC工廠,以實(shí)現(xiàn)作為ASIC使用他們(我認(rèn)為)的概要工具。我的問題是,有沒有辦法使用任何

2019-07-25 13:44:31

ASIC驗(yàn)證能夠采用的主要技術(shù)是什么?如何利用現(xiàn)成FPGA開發(fā)板進(jìn)行ASIC原型開發(fā)?

2021-05-08 07:51:04

,FPGA只需要實(shí)現(xiàn)上層USB協(xié)議。任何從USB主設(shè)備收到的命令都會(huì)通過SIE傳遞到FPGA.FPGA需要包含邏輯來對(duì)這些命令進(jìn)行恰當(dāng)?shù)捻憫?yīng)。例如,在枚舉過程中,USB外設(shè)會(huì) 從主設(shè)備得到一個(gè)命令,請(qǐng)求它

2012-11-22 16:11:20

推動(dòng)FPGA調(diào)試技術(shù)改變的原因是什么外部邏輯分析儀受到的限制是什么如何用內(nèi)部邏輯分析儀調(diào)試FPGA

2021-04-30 06:44:08

切片是整個(gè)切片數(shù)量的一部分還是它們?cè)?b class="flag-6" style="color: red">FPGA上共享資源?2)如果我們沒有進(jìn)行任何DSP操作,那么DSP48E Slice是否可以用于實(shí)現(xiàn)某些常規(guī)邏輯,或者這些DSP Slice是否專門用于實(shí)現(xiàn)DSP

2019-04-04 06:36:56

(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。 本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時(shí)序邏輯來詳細(xì)的分析

2019-06-17 09:03:28

進(jìn)的FPGA相對(duì)通用 GPU或NPU會(huì)更有效率。這使得以下應(yīng)用FPGA比ASIC和GPU具有獨(dú)特的優(yōu)勢(shì):用于 ASIC開發(fā)的數(shù)字邏輯的原型設(shè)計(jì)和測(cè)試一些最新研究的算法通過FPGA搭建自研的數(shù)字集成電路并進(jìn)行

2023-02-08 15:26:46

`單片機(jī)開發(fā)工程師和電子愛好者,每天都要和各種各樣的數(shù)字電路打交道。在制作調(diào)試電路時(shí)除了使用萬用表、示波器等工具,邏輯分析儀也是必不可少的。 邏輯分析儀是利用時(shí)鐘從測(cè)試設(shè)備上采集和顯示數(shù)字信號(hào)的儀器

2012-03-22 13:35:46

Achronix 最新基于臺(tái)積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網(wǎng)絡(luò)(2D NoC)。2D NoC如同在FPGA可編程邏輯結(jié)構(gòu)上

2020-05-12 08:00:00

邏輯分析儀是常用的電子儀器之一,主要應(yīng)用于做數(shù)字電路測(cè)試,FPGA調(diào)試,CPU/DSP調(diào)試,數(shù)字IQ/IF分析,無線通信/雷達(dá)接收機(jī)測(cè)試等場(chǎng)合。邏輯分析儀由模塊和計(jì)算機(jī)組成(當(dāng)然還有探頭),模塊負(fù)責(zé)

2019-06-28 07:51:30

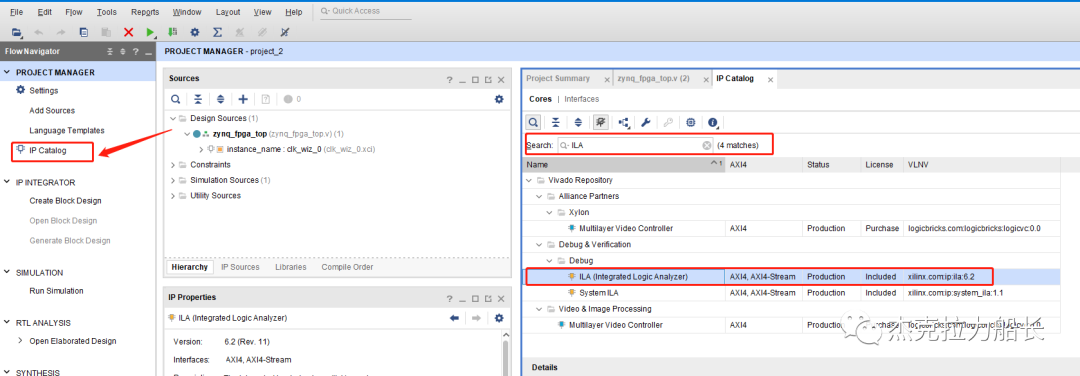

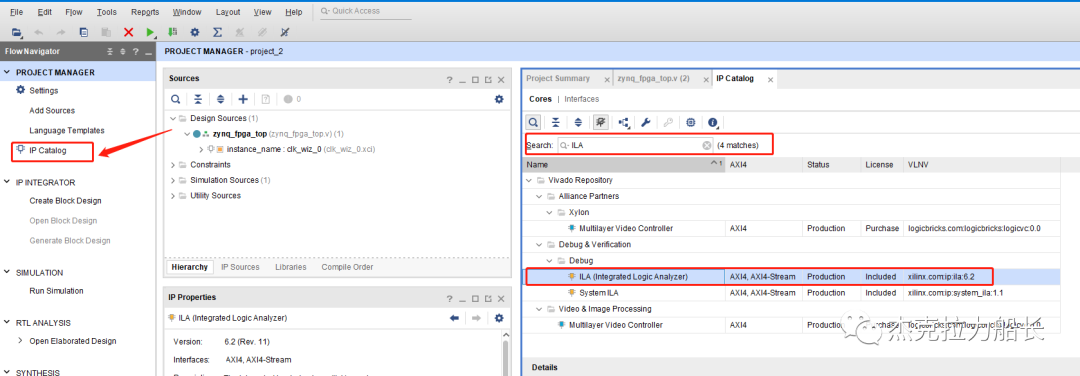

我們看看Vivado中支持的一些重要調(diào)試方式。ILA(Integrated LogicAnalyzer),即內(nèi)嵌邏輯分析儀。可以在FPGA器件上對(duì)已實(shí)現(xiàn)的設(shè)計(jì)進(jìn)行板級(jí)在線調(diào)試。ILA可用于板級(jí)調(diào)試

2019-05-24 15:16:32

在調(diào)試MCU 的SPI 接口時(shí),偶爾發(fā)現(xiàn)通信不成功的情況,為了找出問題原因,使用MI1062 抓取了數(shù)字信號(hào)和模擬信號(hào)進(jìn)行對(duì)比分析。 1、邏輯分析儀測(cè)試信號(hào)邏輯 啟動(dòng)MI1062 邏輯分析儀功能

2017-07-27 09:51:02

時(shí)序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來實(shí)現(xiàn)的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊

2016-12-07 15:51:20

在 FPGA、GPU 或 ASIC 控制的系統(tǒng)板上,僅有為數(shù)不多的幾種電源管理相關(guān)的設(shè)計(jì)挑戰(zhàn),但是由于需要反復(fù)調(diào)試,所以這類挑戰(zhàn)可能使系統(tǒng)的推出時(shí)間嚴(yán)重滯后。不過,如果特定設(shè)計(jì)或類似設(shè)計(jì)已經(jīng)得到

2018-10-15 10:30:31

失敗的原因不是時(shí)序或者功率的問題,而是邏輯或功能錯(cuò)誤。為此,功能驗(yàn)證已經(jīng)成為ASIC開發(fā)周期中一個(gè)最關(guān)鍵的環(huán)節(jié),通常最耗費(fèi)時(shí)間。越來越多的ASIC設(shè)計(jì)人員發(fā)現(xiàn)通過采用FPGA進(jìn)行功能原型設(shè)計(jì)能夠最好

2019-07-15 07:00:39

TLA邏輯分析儀原理與應(yīng)用硬件調(diào)試基礎(chǔ)教程:數(shù)字系統(tǒng)的調(diào)試過程– 首先啟動(dòng)硬件電路– 調(diào)試硬件的設(shè)計(jì)錯(cuò)誤– 調(diào)試部局或結(jié)構(gòu)錯(cuò)誤 短路, 開路, 連接錯(cuò)誤等

2009-10-17 17:33:59 19

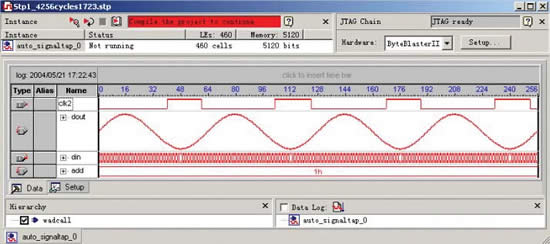

19 本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個(gè)具體的設(shè)計(jì)實(shí)例,詳細(xì)介紹使用SignalTap II對(duì)FPGA調(diào)試的具體方法和步驟。關(guān)鍵字 : S

2009-11-01 14:49:39 45

45 簡(jiǎn)化Xilinx和Altera FPGA調(diào)試過程:通過FPGAViewTM 解決方案,如混合信號(hào)示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動(dòng)探點(diǎn),而無需重新編譯設(shè)計(jì)方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 26

26 實(shí)用FPGA的調(diào)試工具—ChipScope Pro

ChipScope Pro應(yīng)用于FPGA調(diào)試階段,它具有傳統(tǒng)邏輯分析儀的功能,可以觀察FPGA內(nèi)部的任何信號(hào),觸發(fā)條件,數(shù)據(jù)寬度和深度等的設(shè)

2010-02-09 15:10:46 95

95 TLA邏輯分析儀原理與應(yīng)用 -硬件調(diào)試基礎(chǔ)教程。

2010-08-05 15:08:02 49

49 虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)

隨著FPGA技術(shù)的廣泛使用,越來越需要一臺(tái)能夠測(cè)試驗(yàn)證FPGA芯片中所下載電路邏輯時(shí)序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

邏輯分析儀測(cè)試在基于FPGA的LCD顯示控制中的應(yīng)用

摘要:邏輯分析儀作為基礎(chǔ)儀器,應(yīng)該在基礎(chǔ)數(shù)字電路教學(xué)中得到廣泛應(yīng)用。本文介紹了

2008-11-27 09:38:24 1031

1031

摘 要 :本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個(gè)具體的設(shè)計(jì)實(shí)例,詳細(xì)介紹使用SignalTap II對(duì)FPGA調(diào)試的具體方

2009-06-20 10:42:18 1365

1365

邏輯分析儀自1973年問世以來,在短短幾十年的時(shí)間內(nèi)得到了迅速的發(fā)展。傳統(tǒng)邏輯分析儀利用芯片的引腳對(duì)信號(hào)采樣,并送到顯示部分對(duì)系統(tǒng)進(jìn)行分析,但對(duì)于無引腳的封裝類型,傳統(tǒng)邏輯分析儀很難有效的監(jiān)測(cè)系統(tǒng)內(nèi)部信號(hào)。而在FPGA測(cè)試中,嵌入式邏輯分析儀(ELA

2011-03-15 14:52:53 38

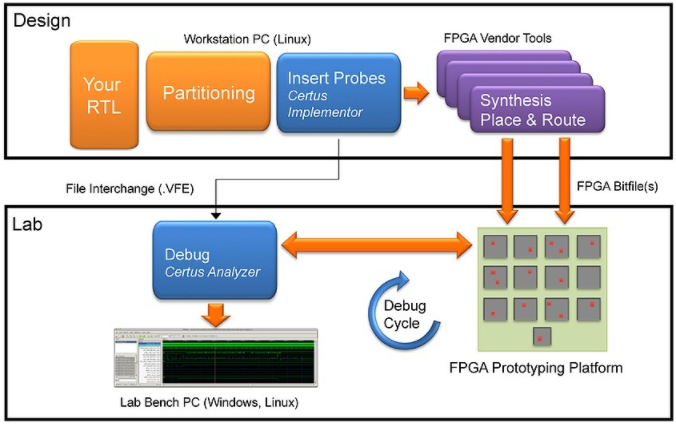

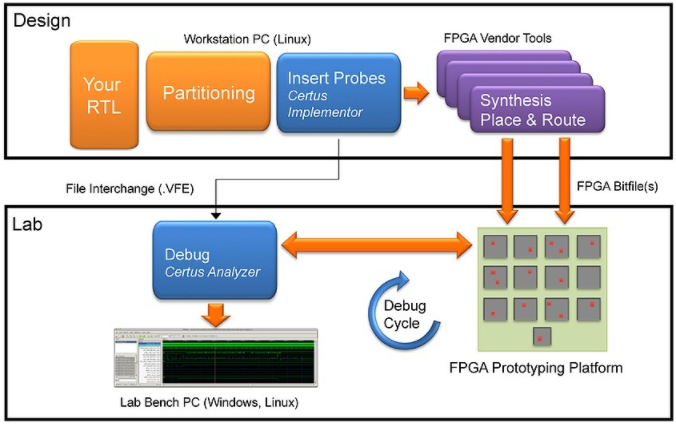

38 對(duì)ASIC設(shè)計(jì)進(jìn)行FPGA原型驗(yàn)證時(shí),由于物理結(jié)構(gòu)不同,ASIC的代碼必須進(jìn)行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計(jì)中,芯片的規(guī)模和復(fù)雜度正呈指數(shù)增加。尤其在ASIC設(shè)計(jì)流程中

2011-03-25 15:16:20 108

108 5月14日,泰克公司宣布,將在2013設(shè)計(jì)自動(dòng)化大會(huì)上展出其最新推出的Certus 2.0 ASIC原型調(diào)試解決方案。與基于RTL嵌入式儀器一起,幫助實(shí)現(xiàn)完整的RTL級(jí)可視性使FPGA內(nèi)部可視成原型平臺(tái)。

2013-05-14 11:36:18 765

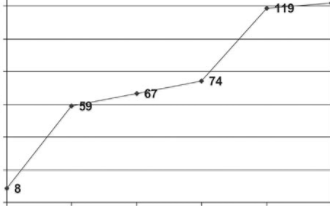

765 ASIC設(shè)計(jì)在尺寸和復(fù)雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進(jìn)展意味著這些設(shè)計(jì)中的2/3能夠使用單個(gè)FPGA進(jìn)行建模。

2017-02-11 16:26:11 795

795

測(cè)信號(hào)通過比較器進(jìn)行判定,高于參考電壓者為High,低于參考電壓者為L(zhǎng)ow,在High與Low之間形成數(shù)字波形。邏輯分析儀與示波器相同,是通過采集指定的信號(hào),并通過圖形化的方式展示給開發(fā)人員,開發(fā)人員根據(jù)這些圖形化信號(hào)按照協(xié)議分

2017-10-16 15:35:29 3

3 到高達(dá)10Gbps,高速IO的測(cè)試和驗(yàn)證更成為傳統(tǒng)專注于FPGA內(nèi)部邏輯設(shè)計(jì)的設(shè)計(jì)人員面臨的巨大挑戰(zhàn)。這些挑戰(zhàn)使設(shè)計(jì)人員會(huì)把絕大部分設(shè)計(jì)周期時(shí)間放在調(diào)試和檢驗(yàn)設(shè)計(jì)上。

2018-07-19 14:19:00 13242

13242

ASIC設(shè)計(jì)在尺寸和復(fù)雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進(jìn)展意味著這些設(shè)計(jì)中的2/3能夠使用單個(gè)FPGA進(jìn)行建模。然而,這些設(shè)計(jì)中仍然保留有1/3(那就是說,所有ASIC

2017-11-25 09:05:02 924

924 ASIC 和 FPGA 具有不同的價(jià)值主張,選擇其中之一之前,一定要對(duì)其進(jìn)行仔細(xì)評(píng)估。2種技術(shù)的比較信息非常豐富。這里介紹了ASIC和FPGA的優(yōu)勢(shì)與劣勢(shì)。

2017-11-25 09:24:44 4374

4374 一旦僅用于膠合邏輯,FPGA已經(jīng)發(fā)展到可以在單個(gè)器件上構(gòu)建片上系統(tǒng)(SoC)設(shè)計(jì)的程度。門和功能的數(shù)量急劇增加,以與傳統(tǒng)上僅通過ASIC設(shè)備提供的功能相競(jìng)爭(zhēng)。本文介紹了FPGA設(shè)計(jì)方法優(yōu)于ASIC的一些優(yōu)勢(shì),包括早期上市,輕松過渡到結(jié)構(gòu)化ASIC,以及降低NRE成本。

2019-09-14 12:28:00 2307

2307 進(jìn)行硬件設(shè)計(jì)的功能調(diào)試時(shí),FPGA的再編程能力是關(guān)鍵的優(yōu)點(diǎn)。CPLD和FPGA早期使用時(shí),如果發(fā)現(xiàn)設(shè)計(jì)不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察的FPGA內(nèi)部信號(hào)引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。

2020-09-14 15:08:00 527

527

FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設(shè)計(jì)流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測(cè)試設(shè)備■使用 FPGAVIEW改善外部測(cè)試設(shè)備方法■FPGA中高速O的信號(hào)完整性測(cè)試和分析

2020-09-22 17:43:21 9

9 FPGA_ASIC-DSP和FPGA共用FLASH進(jìn)行配置的方法(哪些專業(yè)適合嵌入式開發(fā))-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進(jìn)行配置的方法講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 11:16:55 21

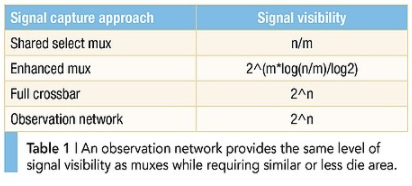

21 隨著復(fù)雜性的增加和對(duì)探測(cè)點(diǎn)的訪問受限,ASIC 和 FPGA 驗(yàn)證和調(diào)試變得乏味且耗時(shí)。隨著越來越多的功能集成到每個(gè)芯片中,對(duì)探測(cè)點(diǎn)的物理訪問變得不可能。

2022-06-19 07:40:00 750

750

后面有專門的人員進(jìn)行布局布線,而且是專用的布局布線軟件工具。 不同點(diǎn) 可編程性:FPGA可重構(gòu)電路,完全由用戶通過軟件進(jìn)行配置和編程,從而完成某種特定的功能,且可以反復(fù)擦寫;ASIC永久電路,ASIC需要較長(zhǎng)的開發(fā)周期,風(fēng)險(xiǎn)較大,一旦有問題,成片全部作廢。 功耗:在相同工藝條件下,

2022-11-28 10:30:13 770

770 FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場(chǎng)可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 1 推動(dòng)FPGA調(diào)試技術(shù)改變的原因 進(jìn)行硬件設(shè)計(jì)的功能調(diào)試時(shí),FPGA的再編程能力是關(guān)鍵的優(yōu)點(diǎn)。CPLD和FPGA早期使用時(shí),如果發(fā)現(xiàn)設(shè)計(jì)不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察

2023-12-20 13:35:01 147

147

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論