linear.com.cn/altera 查閱。凌力爾特的解決方案滿足了 Arria 10 FPGA開發(fā)套件及其支持性系統(tǒng)構(gòu)件的關(guān)鍵功率要求。例如: LTC3877 VID 控制器和 LTC3874 相位擴展器 DC/DC 穩(wěn)壓器可采用一個 12V 輸入為內(nèi)核電源軌在 0.95V 提供 105A。

2015-08-28 14:58:15 2314

2314

今日,三星電子正式宣布已經(jīng)開始大規(guī)模生產(chǎn)基于10nm FinFET技術(shù)的SoC,這是業(yè)界內(nèi)首家提供10nm工藝代工廠商。新工藝下的SoC性能可以提供27%,功耗將降低40%。

2016-10-17 14:07:01 873

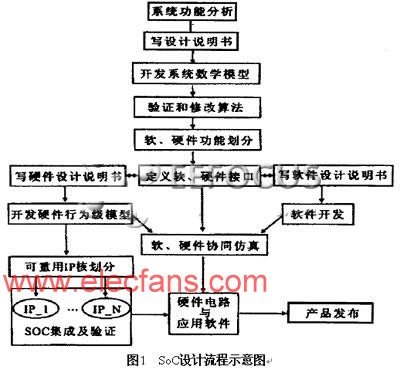

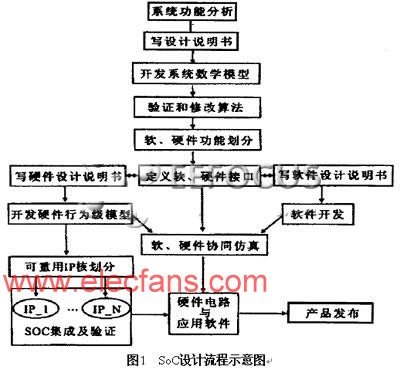

873 片上系統(tǒng)(soc)正日益成為一種網(wǎng)絡(luò),您可以在其中添加單獨的知識產(chǎn)權(quán)(IP)模塊。SoC IP模塊包括處理器、內(nèi)存控制器、專用子系統(tǒng)和 I/O——這些模塊可以從互連IP中分離開來,并放入日益復(fù)雜的SoC分區(qū)。

2020-05-04 11:31:00 1136

1136 各種考慮因素在設(shè)計過程中發(fā)揮了特殊作用:指定 FPGA 的 I/O 接口、識別不同的時鐘域、定義基本設(shè)計功能的框圖、集成 IP 塊、制定功能的驗證/測試計劃整個團隊(可制造性設(shè)計)。

2022-08-15 11:23:40 213

213 在系統(tǒng)芯片(SoC)設(shè)計中, DDR模塊是一種重要的組成部分。它不僅在提高系統(tǒng)性能方面起著關(guān)鍵作用,還對于優(yōu)化系統(tǒng)功耗管理具有重要意義。

2023-09-13 09:47:54 1544

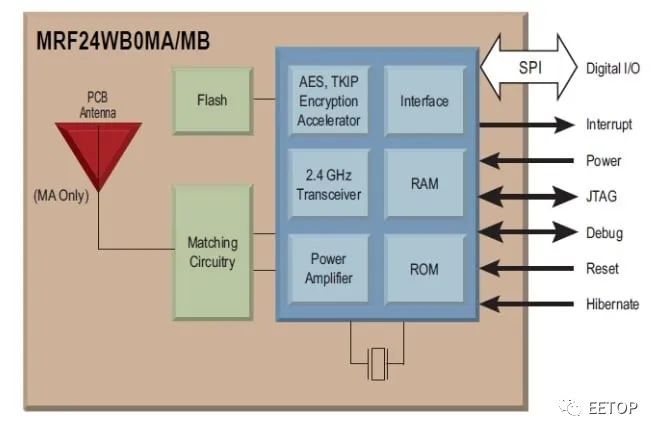

1544 在設(shè)計物聯(lián)網(wǎng) (IoT) 設(shè)備時,是使用無線模塊還是片上系統(tǒng) (SoC) 可能是一個關(guān)鍵且具有挑戰(zhàn)性的決定。

2023-12-01 13:42:50 655

655

BOARD BATTERY FOR SOC'S

2023-03-29 19:51:22

為什么現(xiàn)在原來越多的模塊封裝成SOC

2023-11-02 06:47:31

隨著SOC越來越復(fù)雜,包含的IP越來越多,單個SOC上實現(xiàn)了CPU、射頻模塊、DDR控制模塊、外設(shè)等等功能。各種功能,多種IP也帶來了多檔電源的需求。同時為了滿足低功耗的要求,SOC通常被分為多個

2021-10-28 09:45:05

擁有成本,從而帶來可持續(xù)的長期盈利能力。美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本優(yōu)化的封裝

2019-06-24 07:29:33

傾向?qū)?b class="flag-6" style="color: red">SoC定義為將微處理器、模擬IP核、數(shù)字IP核和存儲器(或片外存儲控制接口)集成在單一芯片上,它通常是客戶定制的,或是面向特定用途的標準產(chǎn)品。SoC定義的基本內(nèi)容主要在兩方面:其一是它的構(gòu)成,其二

2016-05-24 19:18:54

描述This power supply design is used as the main power converter for the Altera Arria GX II FPGA.The

2018-09-06 09:17:06

FPGA 供電時所需的所有電源軌。為提供正確的電源定序,此設(shè)計采用 UCD90120A 電源序列發(fā)生器和監(jiān)視器,并可通過 I2C 對它們進行控制。主要特色提供為 Altera Arria V FPGA

2018-09-12 09:08:24

描述PMP9449 參考設(shè)計提供為 Altera 的 Arria? V GX 系列 FPGA 供電時所需的所有電源軌。它使用 TPS38600 監(jiān)控輸入電流并提供上電定序。此設(shè)計采用低成本、小尺寸

2018-12-04 11:33:24

描述Power Solution Reference Design for Arria V FPGA from Altera.This solution uses integrated

2018-12-21 11:44:05

DK-SOC-10AS066S-A

2023-03-28 13:19:47

DEV KIT ARRIA 10 SX SOC

2024-03-14 20:40:18

使用DS5連接arria 10 soc的hps,出現(xiàn)unable to connect to TCP:localhost失敗,請問有熟悉的能解釋是啥原因嗎

2017-08-23 13:54:47

,RF和藍牙。它還提供了一堆可配置的GPIO,這些GPIO被配置為數(shù)字外設(shè),用于不同的應(yīng)用和控制用途。DT-BL10 WiFi模塊使用BL602作為Wi-Fi和BLE共存SOC芯片。DT-BL10 WiFi模塊集

2022-02-10 07:57:45

剛剛?cè)胧謋pga,要求設(shè)計一個簡單的soc,帶有基本的模塊CPU,RAM,串口通信模塊,支持與外部的SPI Flash進行通信,求設(shè)計思路,學(xué)習(xí)步驟等,時間比較緊迫

2015-04-19 17:26:18

描述A 4 phase buck regulator design fully complaint to power the core rail of Intel Arria 10 GX FPGAs

2018-12-06 11:44:20

因客戶退單,有900顆 Intel Arria10芯片,料號:10AX066N2F40I2LG有意請聯(lián)系 QQ/郵箱:22101076

2019-03-13 23:10:30

了3款足夠“有料”的FPGA及SoC系列:Arria 10、Stratix 10以及MAX 10,它們都是Altera在創(chuàng)新大潮中重磅推出的“第10代”(Generation 10)產(chǎn)品,也為

2019-07-01 08:14:44

我最近嘗試用arria 10 soc實現(xiàn)與ad9680之間的jesd204B協(xié)議,看了很多資料,卻依然感覺無從下手,不知道哪位大神設(shè)計過此協(xié)議,希望可以請教一番,在此先謝過。

2017-12-13 12:47:27

從ALtera官網(wǎng)下載了一個參考設(shè)計,其基于stratix V,但我的開發(fā)板型號為Arria 10 SOC,做相應(yīng)修改后,編譯出現(xiàn)以下,不知道有人遇到過沒有,求幫助。Error (14566

2018-01-07 21:16:13

。根據(jù)設(shè)計只要時鐘輸入正確,加載程序后就能通過光口發(fā)送數(shù)據(jù)。該程序在開發(fā)板上能夠正常輸出數(shù)據(jù),在設(shè)計板上沒有任何反應(yīng)。問題:1、兩種芯片都是Arria10 系列,程序移植是否存在問題?程序編譯沒報錯

2019-08-15 16:21:31

基于DSP核控制的SoC系統(tǒng)是由哪些部分組成的?基于DSP核控制的SoC系統(tǒng)該如何去設(shè)計?

2021-06-18 09:42:47

SoC芯片結(jié)構(gòu)及物理實現(xiàn)流程介紹SoC芯片時序約束設(shè)計的關(guān)鍵在于功耗管理控制模塊的時序約束時鐘樹設(shè)計的內(nèi)容有哪些?

2021-04-13 06:45:17

NCV-RSL10是通過藍牙5認證并符合車規(guī)的系統(tǒng)單芯片(SoC),具有極高的安全性和可靠性,用于汽車無匙進入、信息娛樂控制、主動安全和自動駕駛等應(yīng)用,為汽車行業(yè)帶來行業(yè)最低功耗。

2021-01-27 07:17:41

工業(yè)系統(tǒng)通常由微控制器和FPGA器件等組成,美高森美(Microsemi? )基于 SmartFusion?2 SoC FPGA的馬達控制解決方案是使用高集成度器件為工業(yè)設(shè)計帶來更多優(yōu)勢的一個范例。

2019-10-10 07:15:34

怎樣去設(shè)計一種基于SoC的音頻IP模塊?

2021-06-07 06:25:00

關(guān)于altera arria GX260的flash是直接連到芯片上的還通過CPLD連上的,這個型號的最簡單的配置芯片是那一個啊~~~~~~~~~~~~~~~跪求高手指教指教~~~~~~~~~~~~~~小弟感激涕零~~~~~~~~~~~~

2012-06-13 15:58:08

單個芯片上集成一個完整的系統(tǒng),一般包括系統(tǒng)級芯片控制邏輯模塊、微處理器/微控制器CPU內(nèi)核模塊、數(shù)字信號處理器DSP模塊、嵌入的存儲器模塊、和外部進行通信的接口模塊、含有ADC/DAC的模擬前端模塊

2016-08-05 09:08:31

設(shè)計和實現(xiàn)方面的某些妥協(xié)。這一點在電源中最為明顯,電源必須更精確,更靈活,更可控,更小,更高效,并且每次新一代FPGA都具有更多的故障感知能力。在本文中,我們將特別介紹Altera Arria 10 FPGA

2018-09-10 10:38:23

`描述及特性This power supply design is used as the main power converter for the Altera Arria GX II FPGA.

2015-04-20 14:41:27

內(nèi)核供電,這有幾個特點以配合 SoC 的節(jié)能方案: Arria 10 的 SmartVID 采用 DC/DC 穩(wěn)壓器的集成型 6 位并行 VID 接口,以控制 DC/DC 穩(wěn)壓器以及降低靜態(tài)和動態(tài)狀態(tài)

2018-10-29 17:01:56

電源調(diào)試時間。 一個很好的例子:給 Arria 10 FPGA 和 Arria 10 SoC 供電 系統(tǒng)開發(fā)人員可以使用 FPGA 開發(fā)工具評估 FPGA,而無須設(shè)計一個完整的系統(tǒng)。圖 1 和圖

2018-11-20 10:46:52

,因為這樣可以節(jié)省電源調(diào)試時間。 一個很好的例子:給 Arria 10 FPGA 和 Arria 10 SoC 供電 系統(tǒng)開發(fā)人員可以使用 FPGA 開發(fā)工具評估 FPGA,而無須設(shè)計一個完整的系統(tǒng)

2018-10-15 10:30:31

提出了一種在HDTV SOC 系統(tǒng)中實現(xiàn)多模塊共享存儲單元的高效SDRAM 控制器。通過利用合理的請求仲裁、Full Page 讀寫、指令與數(shù)據(jù)分離、指令緩存和前后相關(guān)處理等機制,實現(xiàn)了高吞吐

2009-08-14 16:09:14 13

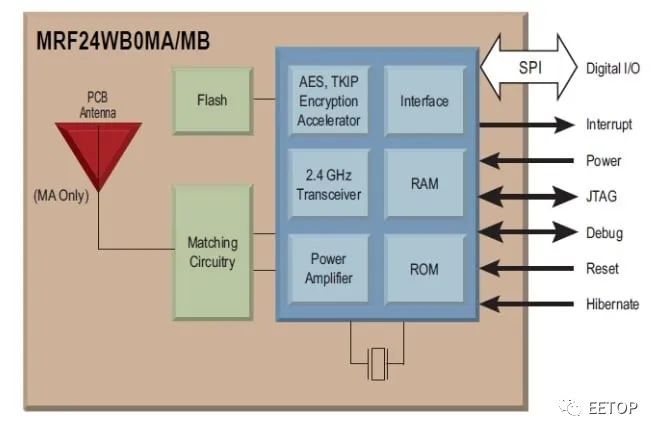

13 SOC 無線收發(fā)模塊(內(nèi)置MCU)

2023-10-08 16:37:54

基于DC/DC轉(zhuǎn)換器,針對Altera Arria II G的高性能電源解決方案,電路如圖:

2010-12-12 10:40:31 36

36 Altera宣布Altera 40-nm Arria II GX FPGA通過PCI-SIG的PCIe Express 2.0規(guī)范測試

Altera公司宣布,其40-nm Arria II GX FPGA符合

2009-07-30 08:13:09 610

610 基于SoC的音頻IP模塊設(shè)計

隨著集成電路設(shè)計技術(shù)和深亞微米制造技術(shù)的發(fā)展,集成電路已進入了片上系統(tǒng)時代。由于SoC結(jié)構(gòu)極其復(fù)雜,對于設(shè)計者而言,數(shù)百萬門規(guī)模

2009-12-11 11:08:12 917

917 Altera 40-nm Arria II GX FPGA轉(zhuǎn)入量產(chǎn)

Altera公司今天宣布,開始量產(chǎn)發(fā)售40-nm Arria® II GX FPGA系列的第一款器件。Arria II GX器件系列專門針對3-Gbps收發(fā)器應(yīng)用,為用戶提供了

2010-02-25 09:21:16 986

986 介紹了Arria II GX FPGA亮點,高速收發(fā)器特性,Arria II GX FPGA架構(gòu)以及Arria II GX FPGA 開發(fā)套件主要特性,開發(fā)板方框圖,詳細的開發(fā)

2010-07-27 17:03:44 3196

3196

什么是soc芯片

SoC(System on Chip)。SoC是在一個芯片上由于廣泛使用預(yù)定制模塊IP而得以快速開發(fā)的集成電路。

2010-09-10 22:50:51 45585

45585

Altera公司(NASDAQ: ALTR)今天宣布,開始發(fā)售其28-nm Arria? V FPGA。Arria V器件是目前市場上支持10.3125-Gbps收發(fā)器技術(shù)、功耗最低的中端FPGA

2011-11-30 16:26:41 1229

1229 本文是基于Arria V和Cyclone V精度可調(diào)DSP模塊的高性能DSP應(yīng)用與實現(xiàn)(英文資料)

2012-09-05 14:18:43 35

35 Altera的Arria FPGA設(shè)計用于對成本和功耗敏感的收發(fā)器應(yīng)用。Arria FPGA系列提供豐富的存儲器、邏輯和數(shù)字信號處理(DSP)模塊資源,結(jié)合10G收發(fā)器優(yōu)異的信號完整性,幫助您集成更多的功能,

2012-09-06 19:53:53 4950

4950 Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行發(fā)布的包括高端Stratix10和中端Arria10系列。目標是替代傳統(tǒng)的ASSP和ASIC。

2013-06-13 14:26:14 2150

2150 9月26號,北京——Altera公司(Nasdaq: ALTR)今天宣布,開始量售其Cyclone? V SoC芯片以及Arria? V SoC工程樣片。隨著處理器峰值時鐘頻率的提高——商用

2013-09-26 17:48:23 993

993 現(xiàn)在,您可以采用 Altera SoC 器件來設(shè)計定制器件,這是我們流行的28 nm Cyclone V 和 Arria V 系列中的型號。我們的 SoC 器件將幫助您滿足多變的市場需求和接口標準。

2013-10-10 15:51:34 137

137 2013年12月3號,北京——Altera公司(Nasdaq: ALTR)今天發(fā)布了Arria 10版Quartus II軟件,這是業(yè)界第一款支持20 nm FPGA和SoC的開發(fā)工具。基于TSMC

2013-12-03 10:48:47 1607

1607 2014年8月19號,北京——Altera公司(Nasdaq: ALTR)今天發(fā)布Quartus? II軟件Arria? 10版v14.0——業(yè)界最先進的20 nm FPGA和SoC設(shè)計環(huán)境。

2014-08-19 15:53:24 2582

2582 2014年,12月16號,北京——Altera公司(Nasdaq: ALTR)今天發(fā)布其Quartus? II軟件v14.1,擴展支持Arria? 10 FPGA和SoC——FPGA業(yè)界唯一具有硬核浮點DSP模塊的器件,也是業(yè)界唯一集成了ARM處理器的20 nm SoC FPGA。

2014-12-16 13:48:53 1396

1396 基于AMBA與WISHBONE的SoC總線橋KBar控制器的設(shè)計_陳俊銳

2017-03-19 11:31:31 0

0 SoC中的六項隱性成本 在無線模塊和無線SoC之間選擇時的考慮因素

2017-09-05 15:12:50 1

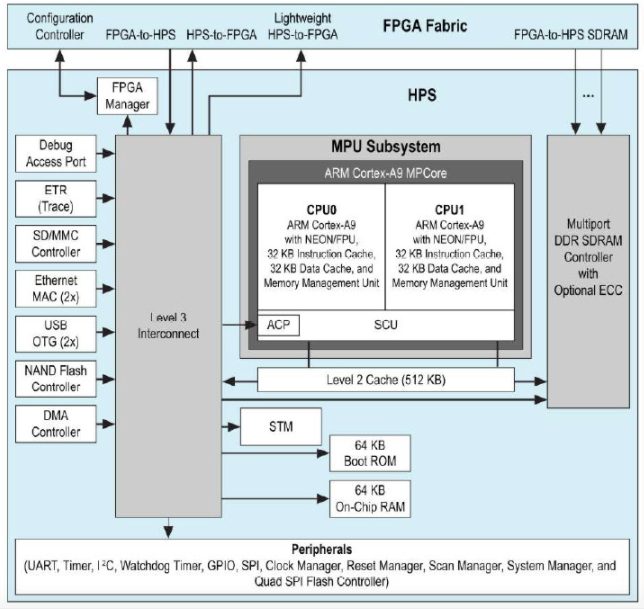

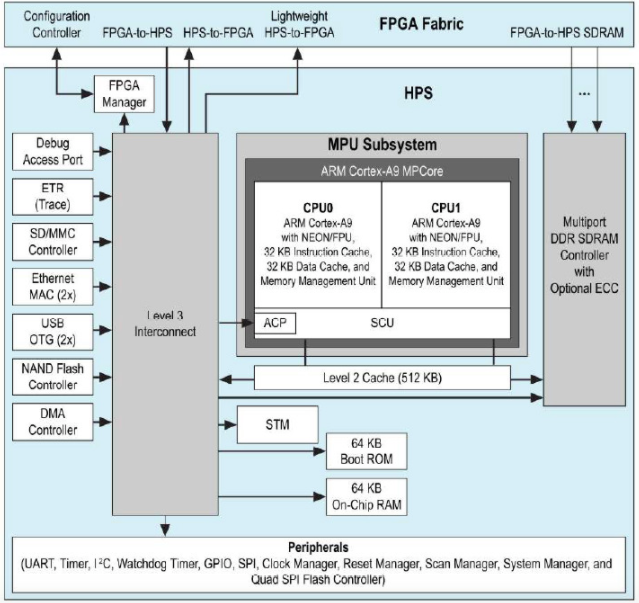

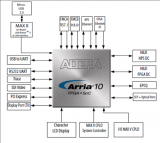

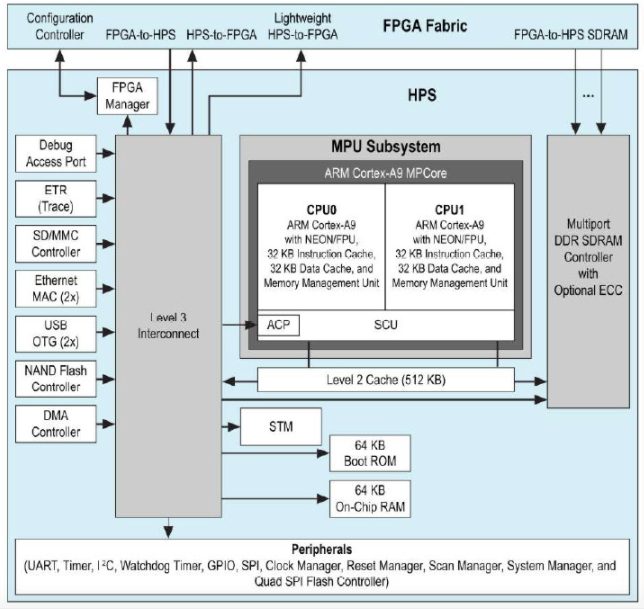

1 本文介紹了Arria 10 SoC FPGA主要特性,框圖以及Arria 10 SoC開發(fā)板主要特性,電源分布網(wǎng)絡(luò)圖和電路圖。

2018-06-16 06:31:00 9763

9763

您是否需要不斷提供越來越多的設(shè)計功能,同時還要跟上新標準的變化,降低成本和功耗?請觀看這一新的7分鐘視頻,看看在我們具有高端功能的低成本收發(fā)器FPGA——Arria II GX上實現(xiàn)各種協(xié)議。您將

2018-06-22 06:56:00 3278

3278 如何為 LVDS SERDES約束Arria 10 器件 IOPLL 位置

2018-06-22 08:47:00 5539

5539

使用廠商內(nèi)存模型運行 Arria 10 RLDRAM3 示例設(shè)計仿真

2018-06-20 01:48:00 1865

1865

為 Arria 10 開發(fā)套件構(gòu)建 RLDRAM3 EMIF 設(shè)計

2018-06-22 01:19:00 2941

2941

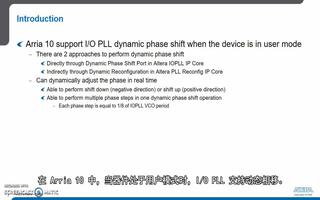

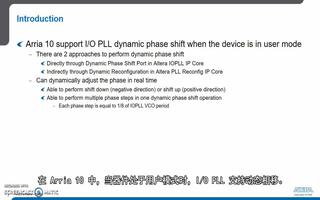

如何在 Arria 10 中實現(xiàn) I/O 鎖相環(huán) (PLL) 動態(tài)相移

2018-06-20 04:56:00 3156

3156

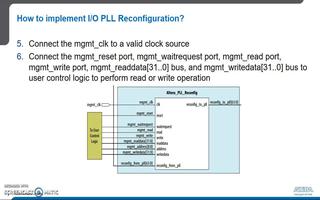

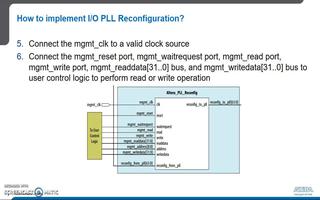

如何在 Arria 10 中實現(xiàn) I/O 鎖相環(huán) (PLL) 重配置

2018-06-20 00:57:00 3438

3438

Arria 10混合存儲器立方體控制器演示第二部分

2018-06-22 02:59:00 3195

3195

Arria 10 單工發(fā)送器和接收器

2018-06-20 01:01:00 3645

3645

Arria 10混合存儲器立方體控制器演示第一部分

2018-06-22 01:02:00 3176

3176

Arria 10 早期功耗估算器

2018-06-20 00:05:00 3239

3239

Arria10接口的JESD204B與ADI9144的互操作性

2018-06-20 00:06:00 4052

4052

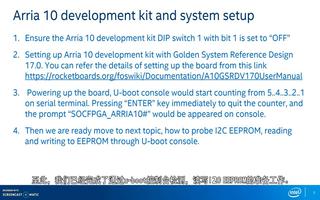

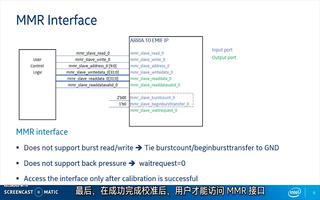

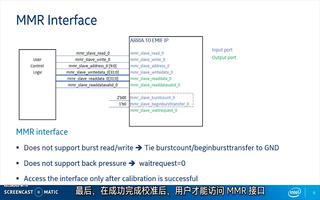

在 Arria 10 中設(shè)計 I2C EEPROM

2018-06-22 01:11:00 2915

2915

Arria? 10 用戶控制刷新

2018-06-26 00:14:00 2496

2496

如何在Arria 10 PCI Express (PCIe)中更改串行(Serial)和PIPE仿真

2018-06-20 00:27:00 4869

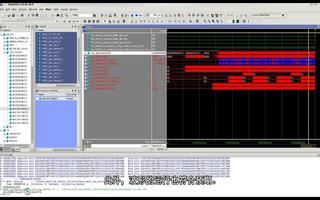

4869 為Arria10自動生成預(yù)定義的signaltap II文件

2018-06-22 05:33:00 2855

2855 Arria 10外部存儲器接口(EMIF)工具包

2018-06-11 17:10:20 1985

1985

了一片Arria 10 SoC和集成雙核ARM Cortex-A9處理器,同時采用了Mobiveil的固態(tài)硬盤(SSD)控制器,以及NVMdurance的NAND優(yōu)化軟件。這一參考設(shè)計提高了NAND應(yīng)用的性能和靈活性,同時延長了數(shù)據(jù)中心設(shè)備的使用壽命,從而降低了NAND陣列的成本。

2018-08-24 16:47:00 605

605 美高森美公司(Microsemi) 宣布提供帶有模塊化電機控制IP集和參考設(shè)計的SmartFusion2 SoC FPGA雙軸電機控制套件。這款套件使用單一SoC FPGA器件來簡化電機控制

2018-08-24 17:29:00 1129

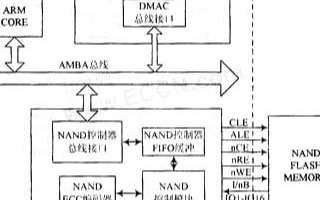

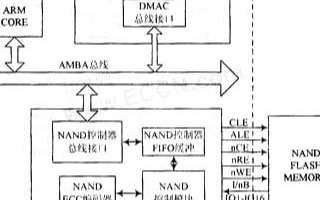

1129 本文所討論的NAND FLASH控制器是針對一款基于ARM7TDMI的SoC芯片,該控制器在芯片中的位置如圖1所示,作為AMBA總線上的一個從設(shè)備集成于AHB上。主要模塊包括總線接口模塊、FIFO緩沖模塊、ECC編碼模塊以及邏輯控制模塊。

2020-05-20 08:00:00 1734

1734

超聲流量計SoC:精度提高10倍

2020-05-30 12:13:00 1570

1570 ADI Guneet Chadha探討電源系統(tǒng)管理(PSM)如何確定Intel Arria ARM Cortex 20nm SoC FPGA上8個電源的時序或按照預(yù)定順序開啟各電源

2019-07-24 06:16:00 1618

1618 Intel正式宣布,以現(xiàn)在準備開始量產(chǎn)Xeon Scalable處理器——Xeon Gold 6138P,該處理器整合了Arria 10 FPGA,并開始向供應(yīng)商發(fā)貨了。

2019-08-15 17:46:30 862

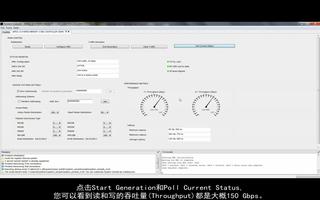

862 英特爾至強6138P包括一個Arria10 GX 1150 FPGA內(nèi)核,和高達160Gbps的I/O吞吐量的帶寬和高速緩存接口,可實現(xiàn)緊耦合加速。

2019-09-16 17:48:55 7167

7167 MLink-DO10 10路繼電器輸出模塊是脈聯(lián)公司針對設(shè)備控制與RS485總線監(jiān)測的裝置。MLink-DO10 10路繼電器輸出模塊基于成熟的嵌入式軟硬件平臺,具有實時性強、可靠性高的特點,提供6組共用公共端繼電器控制輸出,3組獨立公共端繼電器控制輸出,1組繼電器通過模塊自身邏輯判斷輸出。

2020-05-11 14:47:40 1014

1014 10 路繼電器輸出模塊是脈聯(lián)公司針對設(shè)備控制與 RS485 總線監(jiān)測的裝置。 MLink-DO10 10 路繼電器輸出模塊基于成熟的嵌入式軟硬件平臺,具有實時性強、可靠性高的特點,提供 6 組共用公共端繼電器控制輸出, 3 組獨立公共端繼電器控制輸出, 1 組繼電器通過模塊自身邏輯判斷輸出。

2020-05-11 16:45:31 973

973 英特爾的SoC開發(fā)套件提供了開發(fā)定制ARM快速和簡單的方法*處理器的SoC設(shè)計。設(shè)計生產(chǎn)率是Arria 10 SoC架構(gòu)的驅(qū)動理念之一。Arria 10 SoC提供與上一代SoC的完全軟件兼容性

2020-05-20 14:05:56 1243

1243 Altera Arria V系列FPGA的電源解決方案

2021-04-29 08:58:06 9

9 DK-SOC-10AS06S-A設(shè)備原理圖套件

2021-05-19 11:31:29 1

1 更改AN-710(AD6674/AD9234/AD9680/AD9690 Stratix5-Arria10)

2021-05-22 09:51:27 10

10 可提供中端市場中的最佳性能和能效。英特爾 Arria 10 FPGA 和 SoC 的高性能邏輯結(jié)構(gòu),結(jié)合了適用于芯片至芯片和芯片至模塊接口、

2021-05-31 09:42:42 2704

2704 FPGA-SoC芯片中EDAC模塊的設(shè)計與實現(xiàn)(深圳市宇衡源電源技術(shù))-該文檔為FPGA-SoC芯片中EDAC模塊的設(shè)計與實現(xiàn)簡介文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 。------------------------------------------隨著SOC越來越復(fù)雜,包含的IP越來越多,單個SOC上實現(xiàn)了CPU, 射頻模塊,相機模塊,DDR控制模塊,外設(shè)等等功能。多...

2022-01-11 15:43:49 7

7 開發(fā)具有強大架構(gòu)的產(chǎn)品是確保系統(tǒng)設(shè)計滿足現(xiàn)在和未來性能要求的關(guān)鍵。借助用于嵌入式系統(tǒng)的 SoC,設(shè)計立足于堅實的基礎(chǔ)。用于中型應(yīng)用的 FPGA 可顯著節(jié)省空間并在功耗、成本和性能之間取得良好平衡。Arria 10 SoC就是這樣一個典型代表。

2022-06-08 09:31:24 503

503 因此,英特爾 Arria 10 SoC 為嵌入式外設(shè)、硬核浮點 DSP 模塊、嵌入式高速收發(fā)器、硬核存儲器控制器和協(xié)議 (IP) 控制器提供了具有廣泛功能范圍的處理器。

2022-06-08 09:50:57 1047

1047

借助 Arria 10 SoC,您可以通過將 GHz 級處理器、FPGA 邏輯和數(shù)字信號處理 (DSP) 集成到單個可定制的片上系統(tǒng)中來減小電路板尺寸,同時提高性能。

2022-06-30 09:50:09 914

914 具有硬化浮點 DSP 模塊的 FPGA 在中端 Arria 10 構(gòu)建模塊中提供 160 到 1,500 GFLOPS 的容量。這些峰值 GFLOPS 指標的計算基于 CPU、GPU 和 DSP 上使用的相同透明方法。

2022-08-15 11:34:28 831

831 SoC中的FPGA核,如Zynq MPSoC系列或Intel(原Altera)SoC,如Stratix SoC、Arria SoC等。

2022-09-15 09:17:42 975

975

電子發(fā)燒友App

電子發(fā)燒友App

評論