隨著摩爾定律的每轉變,設計人員在開發過程的每個階段都面臨著新的復雜程度的挑戰。芯片設計師不僅要在塊硅片上獲得正確的集成電路( IC) 邏輯、性能、功率和產量。

此外,系統開發人員必須將首次成功擴展到板級參考設計、引導代碼、操作系統 (OS) 端口和應用軟件,更不用說閃存編程、制造測試方法和現場支持了。同時,滿足緊迫的期限和成本目標從未如此具有挑戰性。

改變瓶頸隨著硬件和軟件開發技術的發展,系統測試和調試的性質也在不斷發展。摩爾定律不僅影響了處理器和內存設計,而且在集成系統功能、將操作系統(或實時操作系統 (RTOS))集成到嵌入式系統以及捆綁到嵌入式系統的應用軟件數量方面也發生了類似的變化。終產品。

讓我們倒計時。在大規模集成 (LSI) 組件(至少 1000 個門)時代,中央處理器( CPU) 只是 CPU,受到當時半導體工藝技術、功耗和產量的限制。

調試在很大程度上僅限于集成硬件功能、調整芯片間時序和驗證邏輯功能的過程。系統軟件大約有數百 KB,并且受到預算內存空間中可容納的代碼量的限制。

時代變了。如今,內存空間和高CPU時鐘頻率“幾乎”。設計、調試和測試挑戰已經從硬件組件集成和調試發展到系統硬件設計的仿真,先于 SOC 流片,再到系統軟件建模,然后是數百兆字節 (MB) 的集成) 系統軟件。

在系統級,當今的大多數嵌入式設備都需要功能齊全的嵌入式操作系統,運行多個由內存管理單元 (MMU) 管理的應用程序,并且越來越多地提供某種網絡功能,例如局域網 (LAN) 或無線網絡連接用于控制或網絡訪問數據庫或語音、數據和視頻服務。

當代嵌入式解決方案的是具有數百萬個門的片上系統 (SOC),將高速緩存、暫存器隨機存取存儲器 (RAM) 和外圍功能集成到一個芯片上;許多組件接口被埋在芯片內,不再可用于系統測試/調試的引腳或板級。CPU 內核現在以數百兆赫茲(MHz) 的頻率運行,并集成了許多硬件接口,因此歷史測試方法已不復存在。

JTAG 的救援——邊界掃描測試聯合測試行動小組 (JTAG) 在 1990 年代開始通過標準化串行掃描鏈方法(JTAG;IEEE 1149.1)來訪問片上資源和內置的額外移位寄存器來解決板級測試問題進入每個 IC 的I/O路徑以進行邊界掃描測試。

在邊界掃描測試出現之前,很難調試芯片組件下方的潛在焊料凸點問題。在電路板組裝之前,每個 IC 都經過測試以確保其完美運行。因此,如果組裝好的印刷電路板PCB不能正常工作,則故障一定是由印刷電路板中的焊橋、間隙或缺陷引起的。但是,如果缺陷位于芯片組件下方,無法看到或不易修復怎么辦?

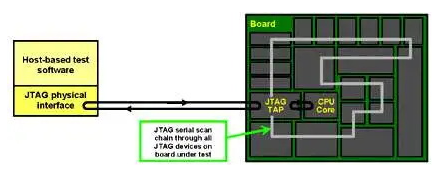

邊界掃描測試方法解決了這個問題。如圖 1 所示,添加了一條通過 I/O 寄存器的串行掃描路徑,并由每塊板獨有的復雜測試程序執行,以幫助識別有故障的芯片或其他設備,以便對它們進行返工或更換。在圖 1 的圖表中,每個灰色框代表一類設備功能,例如閃存、外圍設備、I/O 端口等。

圖 1. 用于邊界掃描測試的 JTAG 連接JTAG 方法提供了一種測試非常復雜的系統的方法,同時保持較低的引腳數。具體來說,無論掃描鏈寄存器路徑有多長,IEEE1149.1 規范只需要 5 個引腳用于 JTAG 連接。JTAG 測試訪問端口的標準引腳功能包括:

TRST 測試復位(從 JTAG 探針輸出到芯片以復位 JTAG 測試邏輯)TCK 測試時鐘(從 JTAG 探針輸出到芯片以設置 JTAG 掃描速率)TDI 測試數據輸入(串行測試數據輸入到芯片)TDO 測試數據輸出(串行測試數據從芯片輸出)TMS 測試模式選擇(通過 TCK 上升沿的狀態確定運行或調試模式)幾家公司幾乎完全專注于邊界掃描測試,專注于 JTAG 硬件連接設備和基于主機的測試軟件工具,以使測試程序適應每個電路板設計。

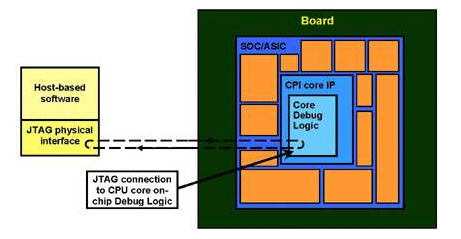

JTAG 的第二個角色——用于軟件/硬件調試的 CPU 內核訪問鑒于 CPU 處理器內核現在通過內核中的集成緩存、本地片上總線、動態分配內存的 MMU 以及其他 SOC 外設和 I/O 塊,JTAG 路徑提供了到 CPU 內部調試邏輯的直接連接。因此,我們現在有了一種觀察和控制程序執行的方法。由于緩存和外圍設備已移至芯片上,因此調試邏輯也必須移至芯片上(下圖 2)。

圖 2. 用于軟件調試/開發的 JTAG 連接通過這種直接內核訪問,基于主機的調試器軟件現在可以斷言“調試異常”,重定向處理器以從調試邏輯寄存器而不是程序計數器獲取下一條指令,從而有效地控制處理器以執行軟件調試操作:

* Run-control: Start, Stop, Single-Step, Step Into/Over (source or instruction)* 設置硬件和軟件斷點* 指定在斷點處要滿足的條件或要執行的腳本* 控制目標系統的復位和初始化*要調試的代碼或要編程到閃存中的代碼*執行閃存編程和其他半托管實用程序請注意,在上述兩種應用中,邊界掃描和軟件調試,JTAG 的作用只是提供物理層通信接口,類似于ISO開放系統互連模型中的 PHY 層。

支持哪些調試功能的協議體現在調試邏輯中,設計到 CPU 內核和主機上運行的調試器軟件功能中。

JTAG 調試優點使用具有 JTAG 訪問權限的調試器的主要優點是:

* JTAG 連接提供對否則隱藏的 CPU 內核的直接訪問* JTAG接口不占用系統 I/O 端口(串行、以太網)* JTAG 調試方法使用很少或沒有系統內存分配(如在監視器中)* 沒有監視器會隨著系統崩潰而崩潰(在電路板啟動時沒有用)* JTAG 連接不需要目標系統電源(一些僅 USB 探頭除外)* JTAG 調試器可以在不停止 CPU 的情況下“竊取周期”來讀取寄存器/內存(假設 CPU 中內置的調試邏輯提供此功能)* JTAG 調試會話可以重置和/或初始化系統(注意:系統重置不是 JTAG 的一部分。相反,它是使用 JTAG 進行遠程調試的附屬物,可以通過網絡遠程重置 JTAG 探針和目標。) * JTAG 調試器可以在不干擾系統的情況下連接到調試邏輯JTAG 調試限制JTAG 調試連接并不能解決世界上所有的調試問題,因為存在一些嚴重的限制:

1) 通過 JTAG 代碼并不是大型程序 (》20MB) 的快方式,尤其是對于依賴 10/100BaseT 以太網訪問的目標系統。

2) 多核系統調試,其中多個 CPU 內核以菊花鏈方式連接在同一個掃描鏈上并且可以單獨訪問,但實現同步調試操作需要額外的片上硬件來避免與 JTAG 操作相關的打滑。

隨后,在發出異步JTAG 停止命令后可能會經過數百個 CPU 周期。這些功能的示例現在開始出現,例如,Cavium Networks Octeon 系列中的全局處理器間控制邏輯,具有多達 16 個64 位cnMIPS 內核。

3)“Printf”仍然為提取各種調試狀態提供了一個簡單的補充。

其他調試功能并非所有調試功能本身都使用 JTAG 掃描鏈。例如,一些處理器包括收集跟蹤信息的能力,這是一種非常有價值的調試工具,因為它可以通過分支和中斷跟蹤執行,通常可以節省數小時或數天的時間來尋找特別虛幻的錯誤。

在代跟蹤實現中,第二個調試邏輯塊以流水線時鐘速率(片外和板外)卸載跟蹤數據,以便在用于控制 JTAG 操作的同一調試探針中收集。

原始的 ARM 嵌入式跟蹤宏單元 (ETM) 和 MIPS EJTAG 調試邏輯的 PCTrace 組件均未使用 JTAG 來上傳跟蹤數據。兩者都使用 JTAG 來設置操作模式,但每個都有自己獨立的并行總線、跟蹤協議和時鐘線,可在 CPU 運行時卸載跟蹤數據。

這為三個限制奠定了基礎:(1) 可靠地收集有效數據的頻率,(2) 在芯片上添加多達 20 個額外焊盤、封裝上的引腳以及使調試探針成本加倍的成本,以及 (3 ) 沒有實用的方法來在具有多個 CPU 內核的 SOC 中實現跟蹤收集。

片上跟蹤緩沖器下一階段的跟蹤技術開發使用片上跟蹤緩沖器來收集有關程序執行流的數據。這種方法帶來雙重好處。首先,它支持以CPU 時鐘速率收集跟蹤數據。同時,這種方法將成本降至,因為跟蹤數據是通過用于正常“運行控制”調試的相同 JTAG 掃描鏈路徑/引腳上傳的。

ARM 的新嵌入式跟蹤緩沖器 (ETB) 和 MIPS 使用跟蹤控制塊 (TCB) 的新 PDTrace 為后續主機處理提供了全面的跟蹤信息,盡管芯片面積和成本有所增加。

英特爾 XScale 應用處理器(IOP、IXC、IXP 和 PXA)在其實現中使用了這一主題的創造性變體。分支數據和分支計數數據不是收集每條指令的大量跟蹤狀態信息,而是收集在一個小得多的片上跟蹤緩沖區中。根據這些數據,可以重建執行流程,只是沒有實時標記可用。

根據所使用的技術和片上緩沖區的大小,可以顯示的跟蹤數據量需要權衡取舍。因此,適用通常的成本與收益權衡。一定量的跟蹤信息總比沒有好,在典型的調試場景中,應該考慮多少才是真正足夠的。

雖然大量的跟蹤信息提供了一種無需“檢測”代碼(這可能會影響性能)就可以分析代碼執行情況的方法,但與之相關的開發工具成本也會增加。

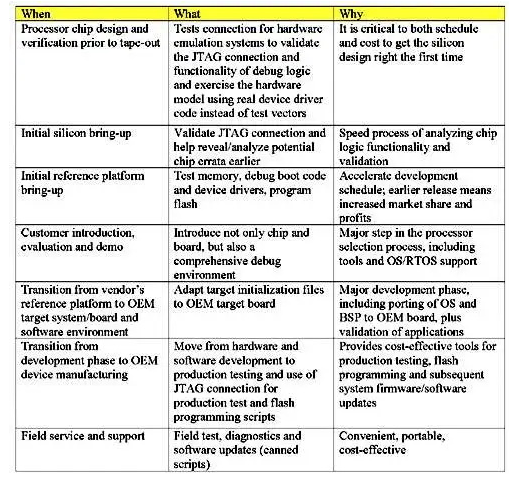

表 1:JTAG 在整個開發和產品生命周期中的適用性和優勢其他 JTAG 應用除了硬件/軟件調試和邊界掃描測試,JTAG 連接還被各種工具供應商用于直接在線閃存編程、發送命令腳本以在目標板上執行、編程現場可編程邏輯器件( FPLD),并為數字信號處理器(DSP) 等其他功能塊提供類似的專用調試功能。許多復雜的 IC 包括內置的自測功能,這些功能通過 JTAG 啟動和后分析。

電子發燒友App

電子發燒友App

評論