賦值何時使用阻塞賦值才能設計出符合要求的電路。 他們也不完全明白在電路結構的設計中,即可綜合風格的Verilog模塊的設計中,究竟為什么還要用非阻塞賦值,以及符合IEEE 標準的Verilog 仿真器究竟如何來處理非阻塞賦值的仿真。 本小節的目的是盡可能地把阻塞和非阻

2021-08-17 16:18:17 6000

6000 Verilog是一種硬件描述語言,用于描述數字電路的結構和行為。與傳統的編程語言不同,Verilog更加注重電路的行為和時序特性。

2023-08-01 09:00:07 1722

1722

。由于他們的模擬、仿真器產品的廣泛使用,Verilog HDL作為一種便于使用且實用的語言逐漸為眾多設計者所接受 。在一次努力增加語言普及性的活動中,Verilog HDL語言于1990年被推向公眾

2019-08-12 10:19:13

嵌入式開發Verilog教程(二)——Verilog HDL設計方法概述前言一、Verilog HDL語言簡介1.1 Verilog HDL語言是什么1.2前言在數字邏輯設計領域,迫切需要一種共同

2021-11-08 09:30:31

Verilog HDL語言有什么優越性Verilog HDL語言在FPGA/CPLD開發中的應用

2021-04-23 07:02:03

:① 邏輯功能正確,②可快速仿真,③ 綜合結果最優(如果是hardware model),④可讀性較好。2. 范圍本規范涉及Verilog HDL編碼風格,編碼中應注意的問題, Testbench的編碼

2017-12-08 14:36:30

的復雜性可以介于簡單的門和完整的電子數字系統之間。數字系統能夠按層次描述,并可在相同描述中顯式地進行時序建模。Verilog HDL 語言具有下述描述能力:設計的行為特性、設計的數據流特性、設計的結構

2020-11-30 19:03:38

Verilog HDL的基礎教程.pdf 硬件描述語言 是硬件設計人員和電子設計自動化工具之間的界面其主要目的是用來編寫設計文件建立電子系統行為級的仿真模型即利用

2008-05-20 13:07:14

Verilog可綜合子集

2013-04-01 12:44:46

在看FPGA的資料,有一個關于Verilog語言的問題突然想不明白~{:16:}關于時序的,Verilog中,判斷if成立的條件是當前值(感覺是電平式),還是過去值(感覺是時序)?例如:if(a==2) out

2013-03-25 21:31:58

Verilog阻塞和非阻塞原理分析在Verilog語言最難弄明白的結構中“非阻塞賦值”要算一個。甚至是一些很有經驗的工程師也不完全明白“非阻塞賦值”在仿真器(符合IEEE標準的)里是怎樣被設定執行

2009-11-23 12:02:57

求,verilog語言1,4,15 位二進制加減法器設計的代碼急用,謝謝:)

2011-04-03 21:52:44

可綜合模型的結構如果程序只用于仿真,那么幾乎所有的語法和編程語句都可以使用。但如果程序是用于硬件實現,那么我們就必須保證程序的可綜合性,即所編寫的程序能被綜合器轉化為相應的電路結構。不可綜合的HDL

2012-10-20 08:10:13

1,在一個verilog程序里,如果循環是一個循環次數不可定的循環,那么它能被綜合工具綜合嗎2,如果程序里有always @(clock)里面又嵌套了@(clock)這樣的控制事件,這個能被綜合嗎

2015-02-03 15:29:11

,若不是,則只能用于仿真),while, 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

,arrays,memories,repeat,task,while。建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點: (1)不使用initial。 (2)不使

2012-02-27 15:01:27

verilog的仿真和綜合有什么區別,請具體一點?

2018-06-06 22:41:18

verilog設計練習進。我們可以先理解樣板模塊中每一條語句的作用,然后對樣板模塊進行綜合前和綜合后仿真,再獨立完成每一階段規定的練習。當十個階段的練習做完后,便可以開始設計一些簡單的邏輯電路和系統

2012-08-15 16:29:30

轉換成HDL代碼,跳過了中間的C語言改寫步驟12.常規從算法到硬件電路的開發過程:算法的開發C語言的功能描述并行結構的C語言改寫verilog的改寫仿真、驗證、修正綜合、布局布線、投入實用13.C語言

2012-01-12 15:15:21

了中間的C語言改寫步驟12.常規從算法到硬件電路的開發過程:算法的開發C語言的功能描述并行結構的C語言改寫verilog的改寫仿真、驗證、修正綜合、布局布線、投入實用13.C語言改寫成verilog

2017-11-30 09:01:53

可綜合的Verilog語法和語義(劍橋大學,影印)

2012-08-06 13:03:57

全球領先的設備軟件優化(DSO)廠商風河系統公司(Wind River)宣布推出Wind River Workbench On-Chip Debugging 3.1.1,將這套綜合性開發工具的支持

2019-08-28 08:14:28

apex20ke_atoms.v編譯到其中。2:在圖形界面中的Load Design對話框中裝入仿真設計時,在Verilog 標簽下指定預編譯庫的完整路徑。(見下圖)邏輯綜合目前可用的FPGA綜合工具

2020-05-15 07:00:00

,都有Xilinx公司自己寫好的可綜合的模塊,想請教一下為什么要分成這樣兩項?它們里面的模塊有區別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區別呢?

2013-09-28 18:17:54

總的來說,UFS3.0的綜合性能,特別是持續讀寫速度有著秒殺UFS2.1前輩的表現,只是在隨機讀寫和SQLite性能上,卻依舊和雙通道的UFS2.1持平,有些小遺憾。最后,咱們再來科普一下eMMC

2021-07-22 07:17:09

、固核與硬核:1.3Verilog HDL設計流程:注:Verilog HDL語法的兩個部分第一章Verilog基礎知識1.1Verilog HDL開發的優勢:語法簡單,可綜合性與系統仿真性能強,支持

2022-03-22 10:26:00

:Verilog HDL程序設計語句和描述方式第四章:Verilog HDL數字邏輯電路設計方法第五章:仿真驗證與Testbench編寫第六章:Verilog HDL高級程序設計舉例第七章:數字集成電路設計流程(測試仿真、綜合)超級干貨,精選內容不可錯過!

2021-03-30 14:31:41

我們以Imagination新發布的兩款內核產品為例,來分析不同應用市場對嵌入式AI的綜合性能指標。

2021-01-14 06:53:15

肇慶學院光機電一體化綜合性實驗教學示范中心實驗教材之二十六計算機控制技術實 驗 教 程肇慶學院電子信息與機電工程學院編二00八年九月內容簡介本書主要是基于清華大學出版社出版的由于海生先生所編著

2021-09-01 06:50:57

問題:用vhdl語言和Verilog語言和matlab協仿真同一個程序,在modelsim上跑出來的結果不一樣。導致時序有問題。網上查了很多資料沒有結果。(調用的.m函數一樣即輸入信號一樣)。例子

2015-04-28 09:12:50

功能仿真:可以驗證代碼的邏輯性,不加任何的時延信息。仿真工具為modelsim(組合邏輯和時序邏輯都可以功能仿真),modelsim不能綜合。在modelsim中添加相應的激勵信號,調用

2016-08-23 16:57:06

數字集成電路設計入門--從HDL到版圖于敦山北大微電子學系?介紹Verilog HDL,內容包括:–Verilog應用–Verilog語言的構成元素–結構級描述及仿真–行為級描述及仿真–延時的特點

2012-08-03 00:23:48

、可維護性,又可以提高仿真效率,且容易被重用。(絕大部分設計人員將這個階段的仿真叫功能仿真!)二、綜合后門級功能仿真 (前仿真) 一般在設計流程中的第二個仿真是綜合后門級功能仿真。絕大多數的綜合工具

2018-01-24 11:06:12

`該資料對STM32微控制器作了詮釋和指導,STM32的基礎實驗,進階應用,硬件描述和綜合性實驗的詳細資料概述包括了實物圖和原理圖。`

2018-09-04 14:35:45

讓大家能夠搭建簡單的 UT 單元測試環境。Verilog 也有適用于仿真的代碼,這些代碼是不可以綜合的。可以使用Verilog 來搭建基本的單元測試環境。本問介紹了如何編寫測試驗證程序(test

2023-10-13 08:11:45

描述語言,它主要應用于數字電路和系統設計、數字電路和系統仿真等,即利用計算機和相關軟件對VERILOG HDL等硬件語言建模的復雜數字電路設計進行仿真驗證,再利用綜合軟件將設計的數字電路自動綜合,以得到

2018-11-05 20:24:23

少部分才是用于電路設計,詳細可以參考本書的“可綜合邏輯設計”一節。Verilog中用于設計的語法,才是學習的重點。掌握好設計的語法,熟練應用于各種復雜的項目,這是技能的核心。其他測試用的語法,需要

2018-10-08 15:19:23

大神,求51單片機綜合性編程題越多越好!

2013-11-04 16:24:05

語言標準的時候,并沒有考慮這些代碼如何用硬件來實現。換句話說,有些代碼寫起來簡單,實現起來卻可能非常復雜,或者幾乎不可能實現。三、HDL代碼的可綜合性現在回到最初的問題上。為什么諸如除法、循環之類

2019-03-27 07:00:00

在本篇里,我們討論 Verilog 語言的綜合問題,Verilog HDL (Hardware Description Language) 中文名為硬件描述語言,而不是硬件設計語言。這個名稱提醒我們

2021-07-29 07:42:25

粘土混砂機實驗(綜合性實驗)一、實驗內容學生自行用實驗用混砂機所帶配件組裝成一種機型的混砂機,并調整到所選定的工作參數;確定型砂配方,在已

2009-05-14 23:49:33 0

0 實驗 譯碼器及其應用(綜合性設計性)

一、實驗目的1. 掌握中規模集成譯碼器的邏輯功能2. 熟悉數碼管的使用3. 能使用譯碼器進行綜合性設計二、實驗預習

2009-07-15 18:43:09 20

20 Verilog HDL 綜合實用教程第1章 基礎知識第2章 從Verilog結構到邏輯門第3章 建模示例第4章 模型的優化第5章 驗證附錄A 可綜合的語言結構附錄B 通用庫

2009-07-20 11:21:13 86

86 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實現了RISC_CPU 的關鍵部件狀態控制器的設計,以及在與其它各種數字邏輯設計方法的比較下,顯示出使用Verilog HDL語言的優越性.關鍵詞

2009-08-21 10:50:05 69

69 分析了模擬硬件描述語言 Verilog-A 的特點及模型結構,根據仿真速度和仿真精度的折衷考慮,設計實現了模擬開關、帶隙基準電壓源及運放的Verilog-A 行為模型。根據數模轉換器

2009-11-21 15:37:55 30

30 LCCT-01A 魯爾接頭綜合性能測試儀產品簡介LCCT-01A 型魯爾接頭綜合性能測試儀是根據“GB/T1962.1-2015(ISO594-1:19)(ISO80369)注射器、注射針

2023-11-23 12:40:54

此綜合與仿真設計指南提供了使用硬件描述語言(HDL)設計FPGA。它包括為HDL設計新手提供設計提示,以及為第一次使用FPGA做設計的經驗豐富的工程師。在使用綜合和仿真設計指南前

2010-11-02 10:06:37 43

43 摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優越性。

2009-06-20 11:51:28 1857

1857

基于Verilog的順序狀態邏輯FSM的設計與仿真

硬件描述語言Verilog為數字系統設計人員提供了一種在廣泛抽象層次上描述數字系統的方式,同時,為計算機輔助設計工具

2010-02-04 09:32:41 1665

1665

Verilog HDL語言簡介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。VHDL是在1987年成為IEEE標準,Verilog HDL

2010-02-09 09:01:17 10317

10317 有許多可綜合狀態機的Verilog代碼描述風格,不同代碼描述風格經綜合后得到電路的物理實現在速度和面積上有很大差別。優秀的代碼描述應當易于修改、易于編寫和理解,有助于仿真和調

2011-12-24 00:52:00 30

30 可綜合的Verilog語法和語義(劍橋大學,影印):第七版

2012-05-21 14:50:14 27

27 verilog硬件描述語言課程講義

2012-05-21 15:01:29 33

33 Verilog HDL 數字設計教程【作者:賀敬凱;出版社:西安電子科技大學出版社】(本資料為ppt) 內容簡介:介紹了Verilog HDL語言,狀態機設計,仿真,還有好幾個可綜合設計的舉例,除了

2012-11-28 13:43:11 489

489 Verilog硬件描述語言參考手冊,Verilog語法內容介紹

2015-11-12 17:20:37 0

0 基于verilog語言的數字頻率計設計基于verilog語言的數字頻率計設計基于verilog語言的數字頻率計設計基于verilog語言的數字頻率計設計

2015-12-08 15:57:23 0

0 介紹Verilog HDL數字設計與綜合的課件

2015-12-23 10:58:54 0

0 VHDL語言編程學習Verilog硬件描述語言

2016-09-01 15:27:27 0

0 ;第4章至第6章主要討論如何合理地使用Verilog HDL語言描述高性能的可綜合電路;第7章和第8章重點介紹了如何編寫測試激勵以及Verilog的仿真原理;第9章展望HDL語言的發展趨勢。

2016-10-10 17:04:40 566

566 Verilog語言練習與講解2,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 1

1 Verilog語言練習與講解1,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 2

2 Verilog語言入門,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 5

5 新型離散小波系統的綜合性能評價_許鳳慧

2017-03-15 09:35:00 1

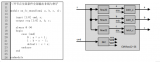

1 基于Verilog HDL語言的電路設計、仿真與綜合 (一)頂層模塊 本程序采用結構化設計方法,將其分為彼此獨立又有一定聯系的三個模塊,如圖1所示:

2017-11-28 14:36:03 16

16 Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。而C語言是一門通用計算機編程語言,應用廣泛。

2017-12-08 16:43:30 11804

11804 如何應用Verilog語言進行數字電路和系統的設計和驗證,從基本概念講起,井逐漸過渡到編程語言接口以及邏輯綜合等高級主題。

2018-12-24 08:00:00 0

0 中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-06 06:12:00 3449

3449

Verilog HDL語言不僅定義了語法,而且對每個語法結構都定義了清晰的模擬、仿真語義。因此,用這種語言編寫的模型能夠使用Verilog仿真器進行驗證。語言從C編程語言中繼承了多種操作符和結構。

2019-09-27 07:09:00 1518

1518

Verilog中提供了四種循環語句,可用于控制語句的執行次數,分別為:for,while,repeat,forever。其中,for,while,repeat是可綜合的,但循環的次數需要在編譯之前就確定,動態改變循環次數的語句是不可綜合的。forever語句是不可綜合的,主要用于產生各種仿真激勵。

2019-10-13 12:23:00 18103

18103 Verilog HDL簡稱Verilog,它是使用最廣泛的硬件描述語言。

2020-03-22 17:29:00 4355

4355 本文主要闡述了verilog中端口的三種類型及verilog語言入門教程。

2020-08-27 09:29:28 10284

10284 的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標準。Verilog HDL具有C語言基礎就很容易上手,而VHDL語言則需要Ada編程基礎。另外Verilog

2020-09-01 11:47:09 4002

4002

Verilog是一種流行的硬件描述語言,他是由工業界開發的,1984年,Verilog作為一種私用的硬件描述語言,由Gateway Design Automation公司給出,1988

2020-09-11 17:24:00 12

12 Verilog黃金參考指南是一個緊湊的快速參考指南Verilog硬件描述語言,其語法,語義,綜合和應用程序的硬件設計。

2021-02-01 15:37:00 22

22 Verilog標準前,由于Cadence公司的 Verilog-XL 仿真器廣泛使用,它所提供的Verilog LRM成了事實上的語言標準。許多第三方廠商的仿真器都努力向這一已成事實的標準靠攏。

2021-02-05 16:24:00 72

72 1、如何使用Verilog HDL描述可綜合電路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語言僅是對已知硬件電路的文本描述。所以編寫前: 對所需實現的硬件

2021-04-04 11:19:00 3837

3837

簡單介紹Verilog HDL語言和仿真工具。

2021-05-06 16:17:10 617

617 條件語句的可綜合性 HDL語言的條件語句與算法語言的條件語句,最大的差異在于: 1.不管條件:當前輸入條件沒有對應的描述,則該條件為不管條件(Don’t?Care)。對應不管條件的信號稱為不管信號

2021-05-12 09:12:22 1558

1558

阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進程管理的術語。由于Verilog團隊是從C語言發展

2021-05-12 09:45:09 2398

2398

VHDL與Verilog硬件描述語言在數字電路的設計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設計復雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2021-08-04 14:16:44 3307

3307 知乎上刷到一個問題,問性能最強的編程語言是什么?看到高贊回答到是Verilog,然后在評論區就引發了一場Verilog到底算不算編程語言的爭論,我覺得比較有意思,所以就也打算嘮嘮這個事情。 趁著最近

2021-08-23 14:30:49 5558

5558 綜合性CPLD/FPGA軟件Quartus 13.0下載

2021-09-12 09:35:13 17

17 Vivado 仿真器支持混合語言項目文件及混合語言仿真。這有助于您在 VHDL 設計中包含 Verilog 模塊,反過來也是一樣。 本文主要介紹使用 Vivado 仿真器進行混合語言仿真的一些要點

2021-10-28 16:24:49 2774

2774 要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。

2022-07-07 09:54:48 1124

1124 綜合工具讀入源文件,通過綜合算法將設計轉化為網表,比如DC。能夠綜合的特性要求Verilog語言能夠描述信號的各種狀態(0,1,x,z)、信號和模塊的連接(例化)以及模塊的邏輯(賦值以及各種運算符)。

2022-07-07 09:53:52 727

727 Icarus Verilog(以下簡稱iverilog )號稱“全球第四大”數字芯片仿真器,也是一個完全開源的仿真器。

2022-08-15 09:11:07 4821

4821 Verilog 是硬件描述語言,顧名思義,就是用代碼的形式描述硬件的功能,最終在硬件電路上實現該功能。 在 Verilog 描述出硬件功能后需要使用綜合器對 Verilog 代碼進行解釋并將代碼

2023-03-21 10:31:40 663

663

要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。在當下的教學過程中,教師和教材都過于強調Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級語法

2023-05-25 15:10:21 642

642

要想深入理解Verilog就必須正視Verilog語言同時具備硬件特性和軟件特性。在當下的教學過程中,教師和教材都過于強調Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級語法

2023-05-25 15:10:44 576

576

建立用于RTL綜合的Verilog標準化子集。他是貝爾實驗室所開發的ArchSyn綜合系統的主要設計者之一。他曾為AT&T和Lucent的許多設計師講授Verilog HDL語言和Verilog HDL綜合課程。

2023-05-26 16:59:30 934

934

Verilog 是一種用于數字邏輯電路設計的硬件描述語言,可以用來進行數字電路的仿真驗證、時序分析、邏輯綜合。

2023-06-10 10:04:44 786

786

近日,清華大學新聞與傳播學院發布了《大語言模型綜合性能評估報告》,該報告對目前市場上的7個大型語言模型進行了全面的綜合評估。近年,大語言模型以其強大的自然語言處理能力,成為AI領域的一大熱點。它們

2023-08-10 08:32:01 605

605

VHDL與Verilog硬件描述語言在數字電路的設計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設計復雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2023-09-09 10:16:56 721

721

簡要分享如何評估所選購焊錫膏綜合性能的優劣?

2023-10-23 09:08:41 209

209 Verilog語言是一種硬件描述語言(HDL),用于描述數字邏輯電路和系統。它是一種非常強大且廣泛使用的語言,在數字電路設計中扮演著重要的角色。其中, inout 是Verilog中的一種信號類型

2024-02-23 10:15:48 176

176

電子發燒友App

電子發燒友App

評論