啟動(dòng)環(huán)境設(shè)置

在啟動(dòng)DC之前,首先要配置DC啟動(dòng)環(huán)境,指定工藝庫和綜合庫。

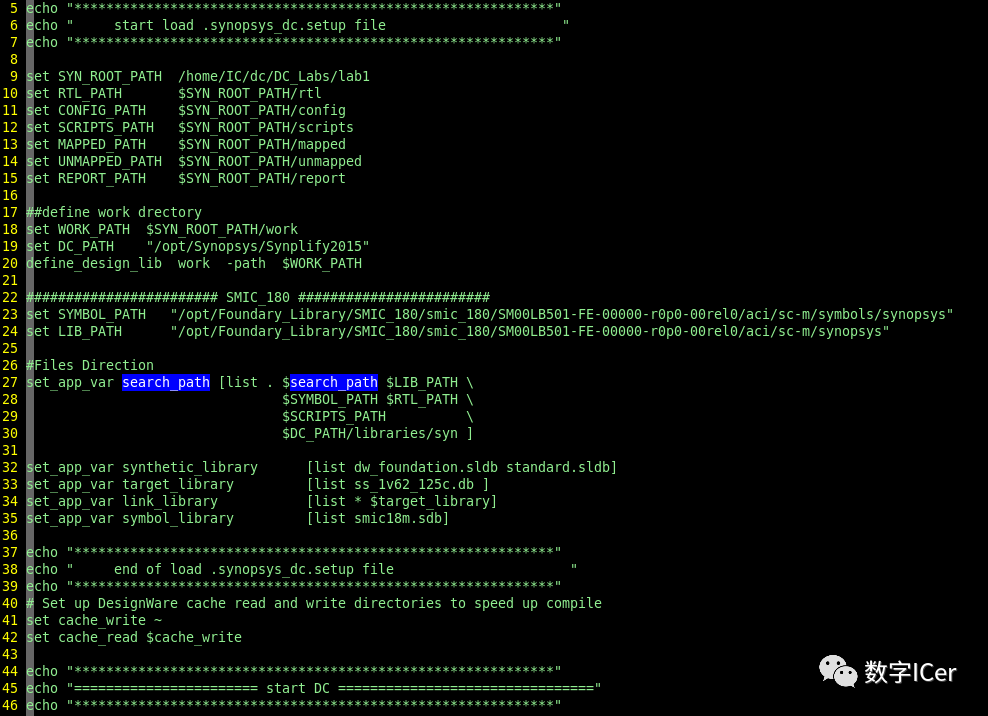

DC的啟動(dòng)配置文件.synopsys_dc.setup,配置了DC啟動(dòng)過程中要執(zhí)行的庫等信息。

.synopsys_dc.setup,這個(gè)文件名不能更改,必須是.synopsys_dc.setup,這個(gè)文件存在于3個(gè)位置:

synopsys的安裝目錄下,基本不需要?jiǎng)舆@個(gè)文件;$SYNOPSYS/admin/setup(/opt/Synopsys/dc/admin/setup/.synopsys_dc.setup)

用戶目錄下,基本不需要?jiǎng)舆@個(gè)文件;~user(/home/IC/.synopsys_dc.setup)

當(dāng)前工作目錄下,(/home/IC/dc/DC_work/work/.synopsys_dc.setup)

配置DC的啟動(dòng)環(huán)境,就是在啟動(dòng)的目錄創(chuàng)建.synopsys_dc.setup文件并進(jìn)行修改。

當(dāng)啟動(dòng)DC時(shí),首先會(huì)在當(dāng)前啟動(dòng)位置尋找.synopsys_dc.setup文件并加載,如果沒有找到則回到當(dāng)前用戶主目錄下尋找,若還沒有找到則加載DC安裝路徑下的.synopsys_dc.setup。

新建并修改.synopsys_dc.setup文件:

.synopsys_dc.setup

其中:

設(shè)置工程路徑

DC運(yùn)行時(shí)的工作路徑(WORK_PATH);

DC軟件安裝路徑(DC_PATH);

指定設(shè)計(jì)和庫的工作路徑:define_design_lib ?work ?-path $WORK_PATH

指定四個(gè)相關(guān)庫路徑:

鏈接工藝庫(link library):鏈接庫是target_library一樣的單元庫或者IP核。

*號(hào)表示開辟一塊單獨(dú)的內(nèi)存空間給DC使用;

目標(biāo)工藝庫(target library):DC將RTL級(jí)的HDL描述映射到實(shí)際的門級(jí)電路時(shí)所需要的標(biāo)準(zhǔn)單元庫。是工藝廠商提供的工藝庫。

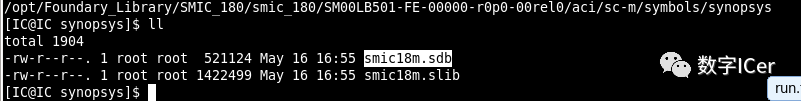

圖形化符號(hào)庫(symbol_library)(SYMBOL_PATH):指定符號(hào)庫的路徑,關(guān)聯(lián)圖形化庫,使用GUI界面的時(shí)候,可以看到綜合得到的門級(jí)網(wǎng)表的圖形化界面。

文件位置:工藝庫SMIC_180下

?

?

/opt/Foundary_Library/SMIC_180/smic_180/SM00LB501-FE-00000-r0p0-00rel0/aci/sc-m/symbols/synopsys

?

?

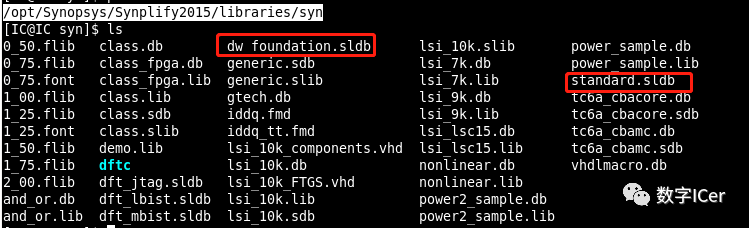

綜合庫(synthetic_library) :也叫IP庫,synopsys做映射自帶的庫:DesignWare library優(yōu)化算術(shù)器件DW_ foundation.sldb和標(biāo)準(zhǔn)單元庫standard.sldb;

文件位置:dc安裝目錄下

?

?

/opt/Synopsys/Synplify2015/libraries/syn

?

?

上面的庫設(shè)置僅僅適用于邏輯綜合,也就是非拓?fù)淠J较碌木C合;

拓?fù)淠J较拢枰玫轿锢韼欤蛘呦嚓P(guān)的物理布局等信息;

create_mw_lib :主要使用DC的物理綜合的時(shí)候,需要生成物理庫;

set與set_app_var區(qū)別:

set: 自己自定義的一些變量;

set_app_var :定義DC內(nèi)部的系統(tǒng)變量等,如果不是合法的名字set_app_var會(huì)報(bào)錯(cuò)。

主要指定有:search_path、synthetic_library、target_library、link_library、symbol_library 以及其他的一些命令開關(guān)等。

DC啟動(dòng)的三種方式

1、design_vision(GUI)

?

?

design_vision?&

design_vision?-topographical_mode?&

?

?

使用拓?fù)浣Y(jié)構(gòu)啟動(dòng)時(shí)必須提供相關(guān)的物理約束和物理庫;

2、dc_shell(shell)

?

?

dc_shell?|?tee?-i?run.log

?

?

3、batch mode

前面兩種方式只是將DC啟動(dòng)起來,還沒有開始工作,需要通過source命令把腳本寫進(jìn)去以后DC讀取才開始工作。

而這種批處理模式,在啟動(dòng)的同時(shí),DC執(zhí)行run.tcl腳本即可工作,其中包括約束要求等:

?

?

dc_shell?-topo?-f?run.tcl?|?tee?-i?run.log

?

?

-topo 使用拓?fù)淠J絾?dòng)DC,啟動(dòng)的同時(shí)執(zhí)行run.tcl腳本,并且把啟動(dòng)過程顯示在終端并打印到run.log中。

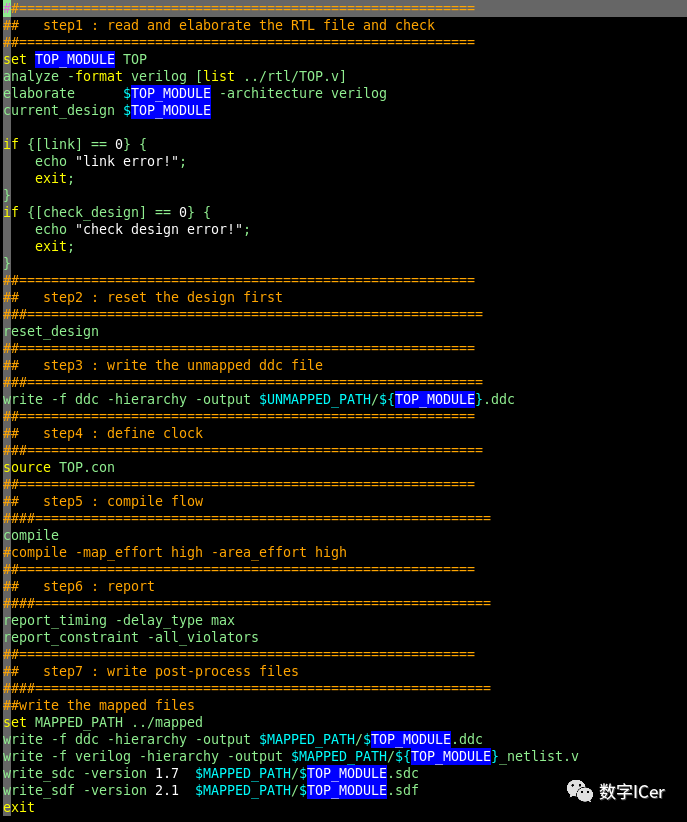

綜合流程實(shí)操

DC綜合流程:

1.準(zhǔn)備好文件

2.啟動(dòng)DC

3.讀入設(shè)計(jì)前的檢查

4.讀入設(shè)計(jì)和查看設(shè)計(jì)及庫

5.約束設(shè)計(jì)

6.綜合

7.綜合后檢查與優(yōu)化

8.保存優(yōu)化后的設(shè)計(jì)

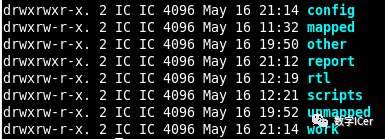

工程目錄:

config: DC的配置文件

rtl:rtl代碼

scripts:腳本

unmapped:DC轉(zhuǎn)換后的GTECH文件或unmapped.ddc文件

mapped:編譯后的網(wǎng)表文件

report: 綜合后的報(bào)告

work:運(yùn)行DC的工作夾

啟動(dòng)DC和檢查庫

1.啟動(dòng)DC

?

?

dc_shell?|?tee?-i?run.log

?

?

可以看到log位置,說明庫加載ok:

?

?

start?load?.synopsys_dc.setup?file????? end?of?load?.synopsys_dc.setup?file

?

?

2.讀入設(shè)計(jì)前檢查:

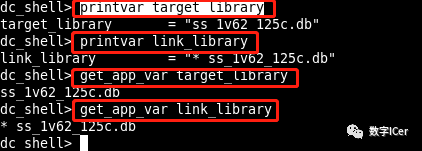

查看設(shè)置的庫文件:

?

?

printvar?target_library????? printvar?link_library???? 或者 get_app_var?target_library???? get_app_var?link_library????

?

?

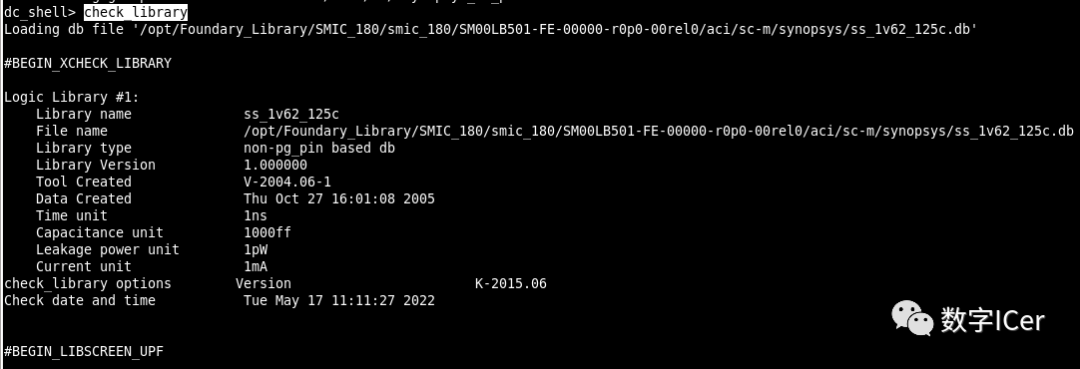

檢查邏輯庫信息:

?

?

check_library

?

?

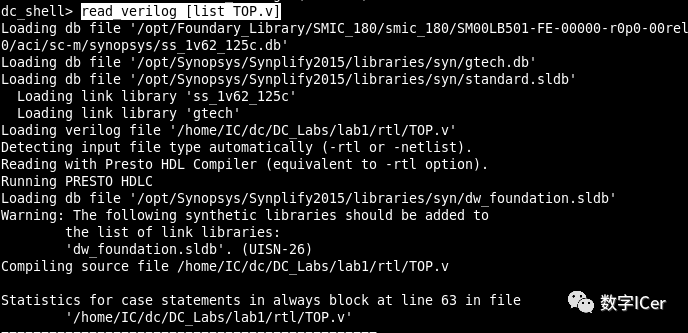

3.讀入設(shè)計(jì)文件:

?

?

read_verlog?[list?TOP.v] 或者 read_vhdl?[list?TOP.vhd]

?

?

或者

?

?

analyze?-format?verilog?[list?TOP.v]?//讀入設(shè)計(jì) elaborate?-architecture?verilog?TOP???//設(shè)置頂層

?

?

dc會(huì)自己尋找?guī)煳募蛂tl文件:

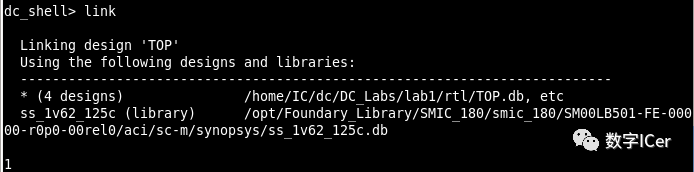

執(zhí)行鏈接命令:查看當(dāng)前要綜合的設(shè)計(jì)是否缺少子模塊

?

?

link

?

?

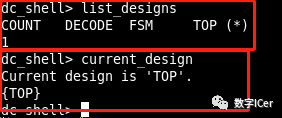

查看設(shè)計(jì)文件,*代表當(dāng)前設(shè)計(jì)頂層 :

?

?

list_designs

?

?

顯示當(dāng)前設(shè)計(jì)頂層 :

?

?

current_design

?

?

更改當(dāng)前設(shè)計(jì)頂層:

?

?

current_design?COUNT

?

?

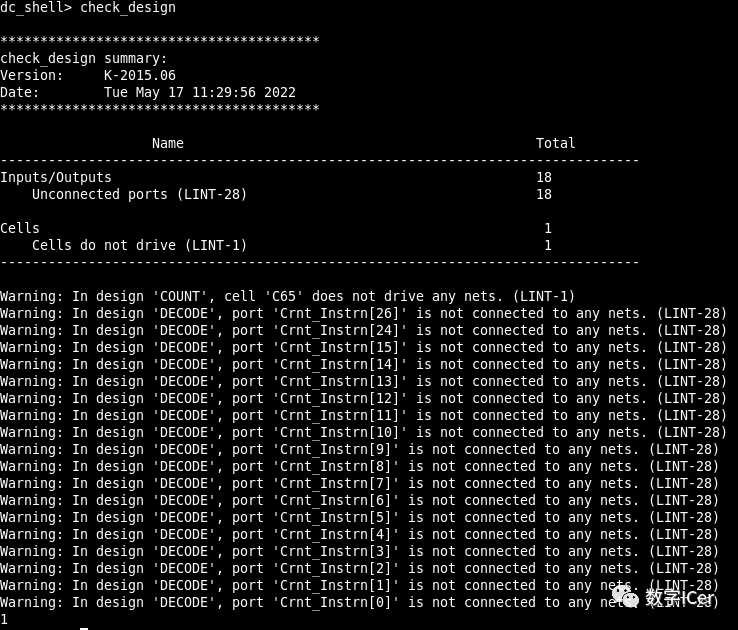

檢查設(shè)計(jì):如果返回0,表明當(dāng)前設(shè)計(jì)存在問題,無法綜合;

?

?

check_design

?

?

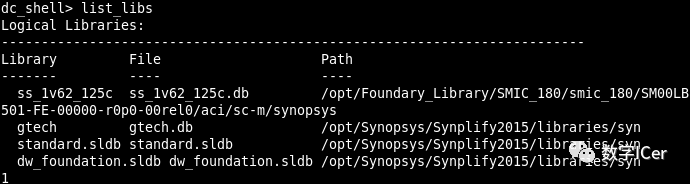

4.檢查庫

查看工藝庫和synopsys庫文件:

?

?

list_libs

?

?

查看庫內(nèi)容(需要安裝Library Compiler):

?

?

report_lib?ss_1v62_125c

?

?

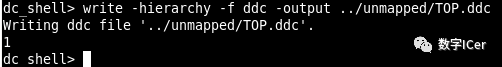

5.以ddc的格式保存未映射的設(shè)計(jì):

?

?

write?-hierarchy?-format?ddc?-output?../unmapped/TOP.ddc

?

?

其他:查看命令解釋:

?

?

man?set_app_var???? set_app_var?-help

?

?

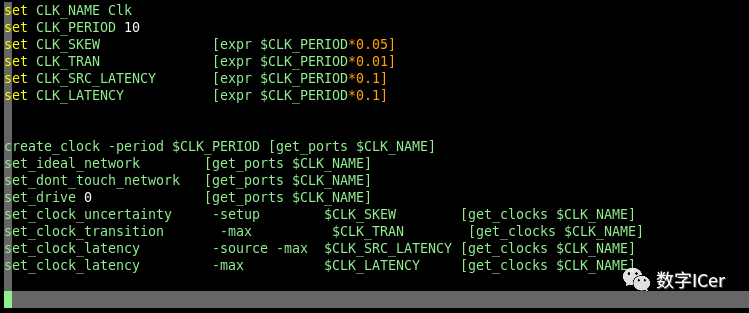

設(shè)置約束

?

?

source?TOP.con

?

?

檢查時(shí)序:檢查有無路徑?jīng)]有約束

?

?

check_timing

?

?

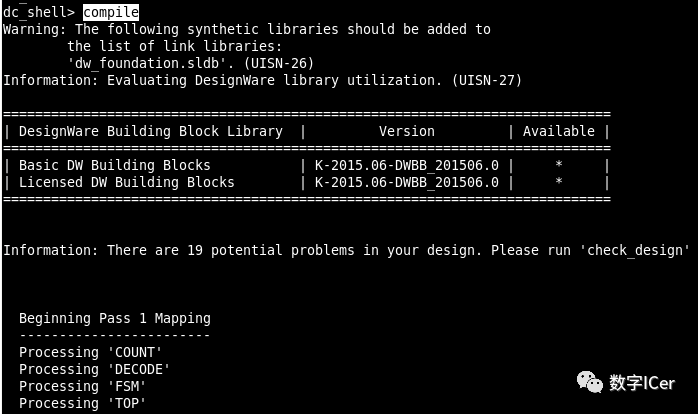

綜合

?

?

compile

?

?

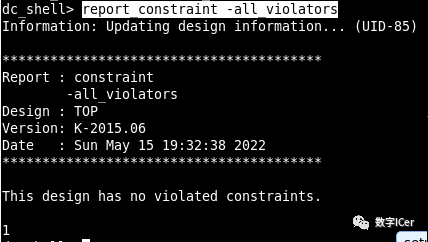

綜合后,進(jìn)行檢查約束是否違例:

?

?

report_constraint?-all_violators

?

?

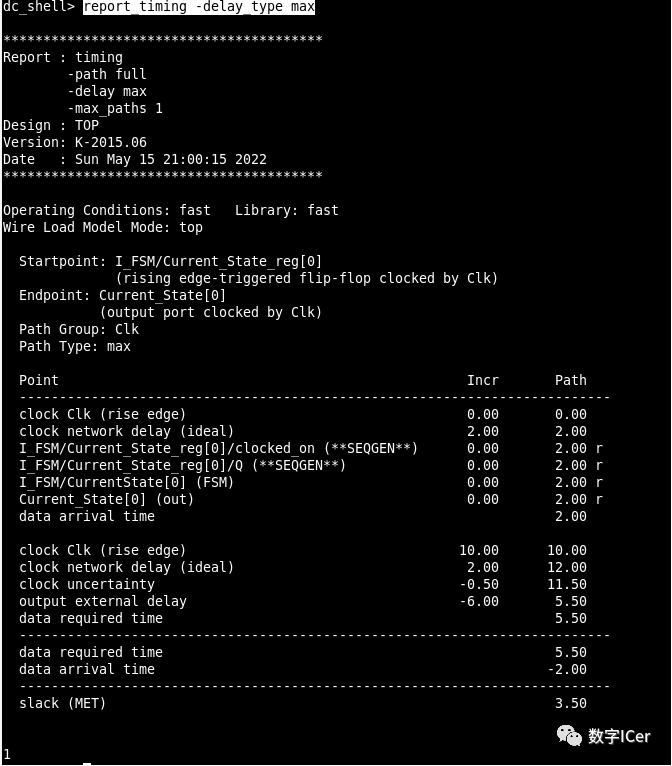

查看最差路徑時(shí)序

?

?

report_timing?-delay_type?max

?

?

保存綜合后的設(shè)計(jì)

保存網(wǎng)表:

?

?

write?-format?verilog?-output?../mapped/TOP_netlist.v

?

?

以ddc的格式保存綜合后的設(shè)計(jì):

?

?

write?-hierarchy?-format?ddc?-output?../mapped/TOP.ddc

?

?

DC腳本運(yùn)行

?

?

dc_shell?-f?../scripts/run_1.tcl?|?tee?-i?run.log

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論