串口是串行接口(serial port)的簡(jiǎn)稱(chēng),也稱(chēng)為串行通信接口或COM接口。

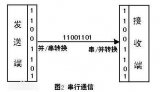

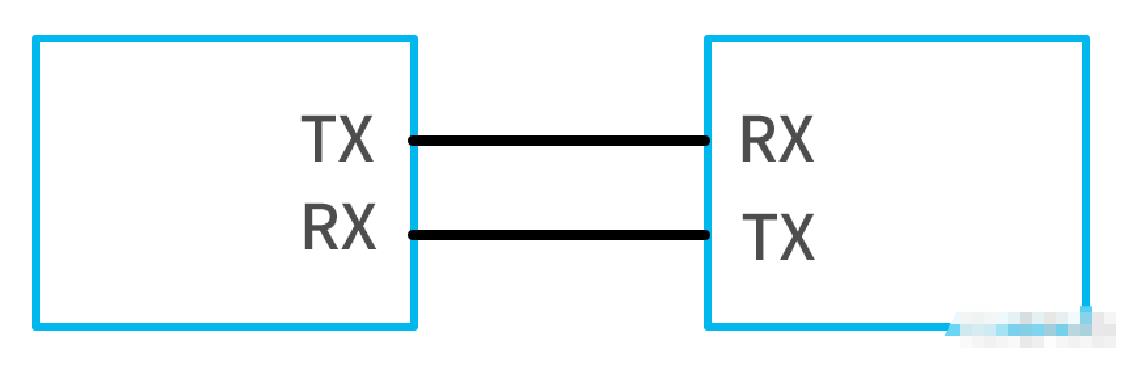

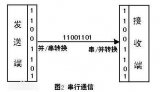

串口通信是指采用串行通信協(xié)議(serial communication)在一條信號(hào)線上將數(shù)據(jù)一個(gè)比特一個(gè)比特地逐位進(jìn)行傳輸?shù)耐ㄐ拍J健?/div>

2023-08-12 11:04:19 1177

1177

【入坑】MT7628/7688有3個(gè)串口, UART0,UART1和UART2, 但使用UART2 時(shí)碰到一些問(wèn)題, MT7628/7688的UART2對(duì)應(yīng)的IO口 默認(rèn)是做網(wǎng)口功能,但未配置

2023-10-30 09:37:06 2881

2881

串口作為常用的三大低速總線(UART、SPI、IIC)之一,在設(shè)計(jì)眾多通信接口和調(diào)試時(shí)占有重要地位。

2024-01-03 11:43:52 754

754

特權(quán)同學(xué)的《FPGA/CPLD邊學(xué)邊練---快速入門(mén)Verilog/VHDL》中的UART串口收發(fā)實(shí)驗(yàn)發(fā)送數(shù)據(jù)和接收的數(shù)據(jù)不一致。在每個(gè)有效數(shù)據(jù)的后面都會(huì)多兩個(gè)數(shù)據(jù)。比如發(fā)送的有效數(shù)據(jù)是:FF。則

2017-11-30 09:25:44

小實(shí)驗(yàn),簡(jiǎn)單講解UART串口通信的應(yīng)用方法。

系統(tǒng)環(huán)境

Windows 10-64bit

軟件平臺(tái)

[size=14.6667px]NucleiStudio IDE 202102版或

2023-08-16 08:24:43

串口代碼,分享給大家。。

2016-01-19 13:25:01

FPGA串口——verilog

2013-06-11 14:11:14

2.取消調(diào)試串口就是不加載編譯這個(gè)代碼,這樣uart2就是默認(rèn)的普通串口來(lái)使用。因此,sed -i “s/CONFIG_FIQ_DEBUGGER=y/# CONFIG_FIQ_DEBUGGER

2022-10-08 16:19:29

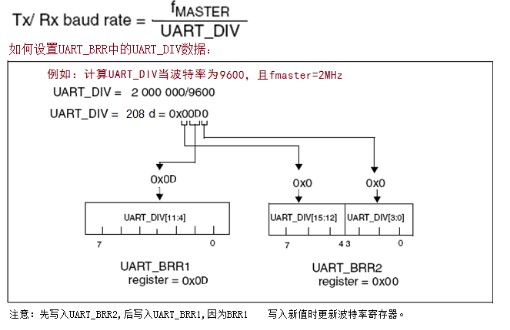

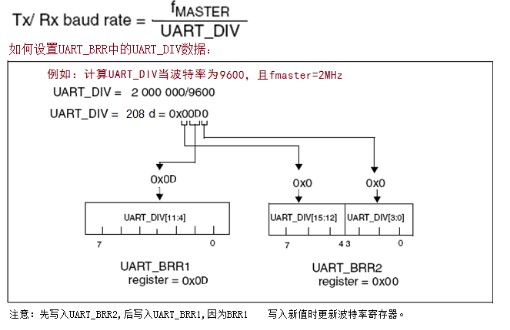

什么是串口?串口的高電平周期是多長(zhǎng)?UART數(shù)據(jù)是如何傳輸?shù)模縎TM32F4xx串口代碼的流程是怎樣的?

2021-11-26 06:40:01

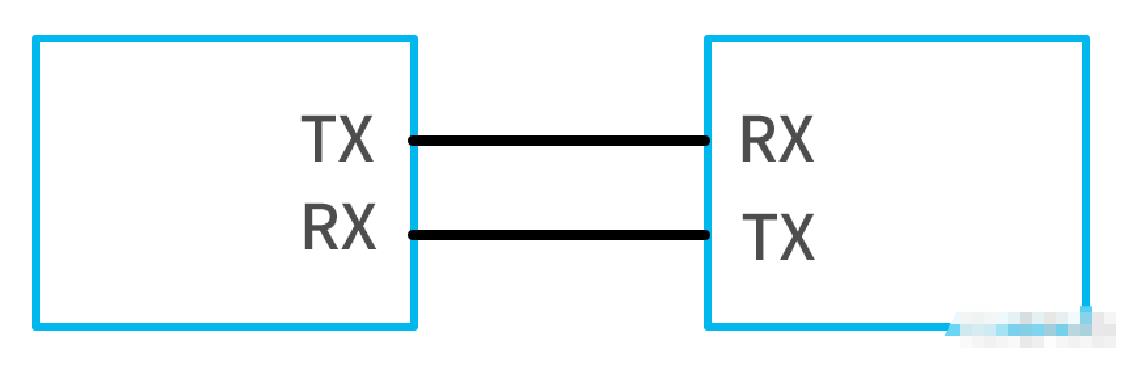

單片機(jī)UART串口通信單片機(jī)的串口通信,一般指的就是UART串口通信(TXD,RXD)。本文實(shí)現(xiàn)的是單片機(jī)和電腦之間的串口通信,需要用到51單片機(jī)開(kāi)發(fā)板,電腦,STC-ISP軟件,代碼已調(diào)試

2021-07-06 07:00:43

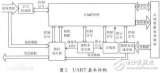

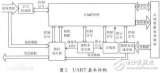

本次實(shí)驗(yàn)是通過(guò)UART進(jìn)行串口通信目錄一、什么是UART二、UART基本結(jié)構(gòu)三、UART基本原理四、在STM32CumeMX配置自動(dòng)生成代碼五、燒入代碼并進(jìn)行觀察結(jié)果四、總結(jié)參考文獻(xiàn)一

2021-12-09 07:47:50

發(fā)燒友們好,我正在開(kāi)始學(xué)習(xí)fpga的知識(shí),現(xiàn)在尋求一個(gè)基于verilog的uart程序,要求是初始位一位,終止位一位,數(shù)據(jù)位8位,實(shí)現(xiàn)回環(huán)功能。大家能幫助一下我嗎?

2020-05-10 22:53:19

誰(shuí)有用verilog實(shí)現(xiàn)一路SPI轉(zhuǎn)4路串口的代碼沒(méi)

2019-04-09 21:28:00

新手,真心求助,求基于verilog的uart程序

2016-03-01 15:32:01

串口精靈源代碼

2006-04-18 22:10:55 87

87 CAN總線控制器Verilog代碼

2008-05-20 10:32:12 167

167 UART 4 UART參考設(shè)計(jì),Xilinx提供Verilog代碼 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 UART 4 UART參考設(shè)計(jì),Xilinx提供VHDL代碼 uart_vhdl

This zip file contains the following folders

2009-06-14 08:57:14 113

113 xapp354 verilog代碼

THIS DESIGN IS PROVIDED TO YOU 揂S IS? XILINX MAKES AND YOU RECEIVE NO WARRANTIES

2009-06-14 09:17:35 34

34 IO模擬串口UART

本文介紹GPIO模擬UART的算法和實(shí)現(xiàn)

2010-04-03 14:11:38 86

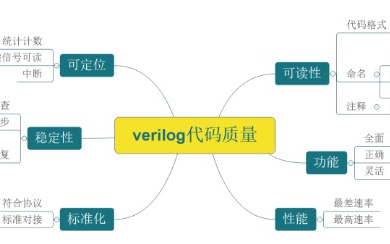

86 Verilog代碼書(shū)寫(xiě)規(guī)范

本規(guī)范的目的是提高書(shū)寫(xiě)代碼的可讀性、可修改性、可重用性,優(yōu)化代碼綜合和仿真的結(jié)果,指導(dǎo)設(shè)計(jì)工程師使用

2010-04-15 09:47:00 106

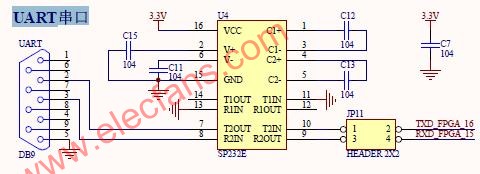

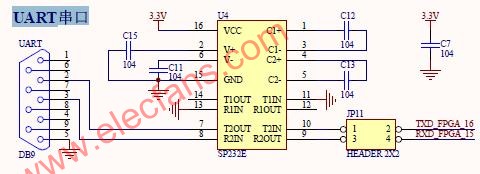

106 UART串口接口電路(采用SP232E)

2010-03-17 09:23:28 8584

8584

Name : uart // File Name?? : uart.v// Function??? : Simp

2010-06-05 12:12:03 6236

6236 本站提供的fpga實(shí)現(xiàn)jpeg Verilog源代碼資料,希望能夠幫你的學(xué)習(xí)。

2011-05-27 15:09:53 200

200 本文介紹的基于Wishbone總線的UART IP核的設(shè)計(jì)方法,通過(guò)驗(yàn)證表明了各項(xiàng)功能達(dá)到預(yù)期要求,為IP核接口的標(biāo)準(zhǔn)化設(shè)計(jì)提供了依據(jù)。此外,該IP核代碼全部采用模塊化的Verilog-HDL語(yǔ)言編寫(xiě),

2011-06-10 11:47:37 3479

3479

在xo640上實(shí)現(xiàn)一個(gè)簡(jiǎn)單的Uart,能夠解析串口數(shù)據(jù),并在寄存器中存儲(chǔ),用FIFO實(shí)現(xiàn)數(shù)據(jù)的傳遞。那么后期可以通過(guò)開(kāi)發(fā)板上的串口經(jīng)CPLD訪問(wèn)各種數(shù)據(jù)。比如PC=CPLD=EEPROM等等,極大方便后期

2011-08-05 16:54:46 1741

1741 Verilog代碼覆蓋率檢查是檢查驗(yàn)證工作是否完全的重要方法,代碼覆蓋率(codecoverge)可以指示Verilog代碼描述的功能有多少在仿真過(guò)程中被驗(yàn)證過(guò)了,代碼覆蓋率分析包括以下分析內(nèi)容。

2012-04-29 12:35:03 7899

7899 《手把手教你學(xué)單片機(jī)》單片機(jī)視頻教程11:異步串口通信UART 單片機(jī)視頻教程11:異步串口通信UART 1、關(guān)于按鍵去抖的問(wèn)題 2、計(jì)算器程序 3、仿真芯片使用說(shuō)明

2012-08-21 09:43:34 13821

13821

電子發(fā)燒友網(wǎng)核心提示: 本例程是Verilog HDL源代碼:關(guān)于基本組合邏輯功能中雙向管腳的功能實(shí)現(xiàn)源代碼。 Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL.

2012-10-15 11:28:26 1525

1525 verilog語(yǔ)言開(kāi)發(fā)的串口模塊程序,測(cè)試可用。

2015-12-25 10:25:19 5

5 verilog_代碼資料,非常實(shí)用的代碼示例。

2016-02-18 15:00:10 36

36 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:43:38 24

24 八選一多路選擇器 Verilog代碼 附仿真結(jié)果(modelsim仿真)

2016-03-28 15:27:42 32

32 niosii的UART串口通信niosii的UART串口通信。

2016-04-06 17:03:27 0

0 8乘8乘法器verilog源代碼,有需要的下來(lái)看看

2016-05-23 18:21:16 24

24 8051 verilog 版代碼分享,有需要的下來(lái)看看。

2016-05-24 09:45:40 0

0 cpu16_verilog源代碼分享,下來(lái)看看。

2016-05-24 09:45:40 26

26 Verilog 入門(mén)的實(shí)例代碼,有需要的下來(lái)看看

2016-05-24 10:03:05 19

19 verilog_代碼分享,有需要的朋友下來(lái)看看。

2016-05-24 10:03:05 11

11 精品verilog實(shí)例程序代碼,下來(lái)看看。

2016-05-24 10:03:05 46

46 1768_UART_Test源代碼,下來(lái)看看

2016-06-07 10:41:41 13

13 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 LPC2368_UART源代碼,又需要的下來(lái)看看

2016-08-15 17:55:06 19

19 UART串口在SIM卡讀寫(xiě)中的應(yīng)用,下來(lái)看看

2016-08-19 16:51:11 0

0 UART串口通訊

2017-01-22 20:51:03 8

8 基于FPGA Verilog-HDL語(yǔ)言的串口設(shè)計(jì)

2017-02-16 00:08:59 35

35 Verilog是描述復(fù)雜的硬件電路,設(shè)計(jì)人員總是將復(fù)雜的功能劃分為簡(jiǎn)單的功能,模塊是提供每個(gè)簡(jiǎn)單功能的基本結(jié)構(gòu)。

2017-11-20 16:49:36 5370

5370

Uart這里指的是TTL電平的串口;RS232指的是RS232電平的串口。TTL電平串口是一般芯片的串口的輸入和輸出端,可以接不通的芯片完成不通的外設(shè)功能。我們來(lái)看看TTL電平和RS232的定義是什么,然后在來(lái)看他們的串口到底有和區(qū)別。

2017-11-20 17:48:08 58571

58571 基于51單片機(jī)的UART串口通信詳解。

2017-11-21 10:14:45 62217

62217

設(shè)備沒(méi)有顯示屏,無(wú)法獲得嵌入式設(shè)備實(shí)時(shí)數(shù)據(jù)信息,通過(guò)UART串口和超級(jí)終端相連,打印嵌入式設(shè)備輸出信息。并且在對(duì)嵌入式系統(tǒng)進(jìn)行跟蹤和調(diào)試時(shí),UART串口了是必要的通信手段。比如:網(wǎng)絡(luò)路由器,交換機(jī)

2017-12-06 14:51:59 106718

106718

描述了浮點(diǎn)型算法的加、減、乘、除的verilog代碼,編寫(xiě)了6位指數(shù)位,20位小數(shù)位的功能實(shí)現(xiàn)并且通過(guò)仿真驗(yàn)證

2018-01-16 14:15:54 1

1 UART串口波特率,常用的值是300、600、1200、2400、4800、9600、14400、19200、28800、38400、57600、115200等速率。IO口模擬UART串行通信程序是一個(gè)簡(jiǎn)單的演示程序,我們使用串口調(diào)試助手下發(fā)一個(gè)數(shù)據(jù),數(shù)據(jù)加1后,再自動(dòng)返回。

2018-05-04 15:26:16 20961

20961

1寄存器的定義說(shuō)明。所以我認(rèn)為只有UART1。既然有這個(gè)功能,那就用吧,我以為直接可以連接到電腦的串口(COM1),就可以使用了,其實(shí)不可以。

2018-10-26 15:43:08 6130

6130

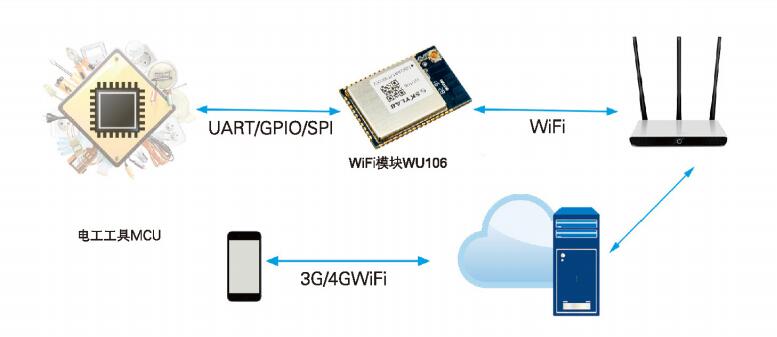

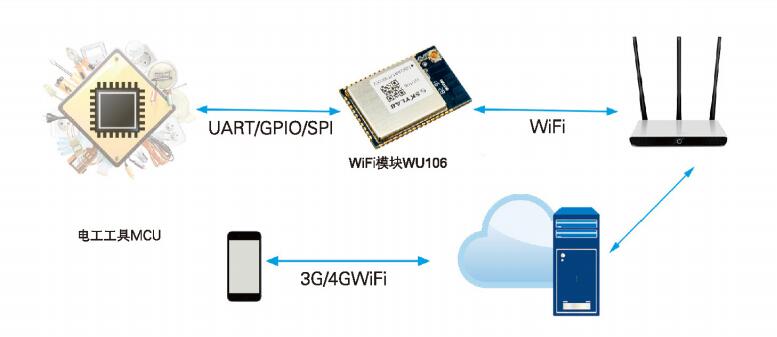

隨著物聯(lián)網(wǎng)智能家居應(yīng)用的日漸豐富,越來(lái)越多的WiFi工程師開(kāi)始更多的關(guān)注UART串口WiFi模塊,為讓新手工程師更快的將UART串口WiFi模塊應(yīng)用于各類(lèi)智能家居應(yīng)用中,本篇SKYLAB君簡(jiǎn)單為大家

2019-01-14 09:27:02 9728

9728

隨著物聯(lián)網(wǎng)智能家居應(yīng)用的日漸豐富,越來(lái)越多的 WiFi 工程師開(kāi)始更多的關(guān)注 UART 串口 WiFi 模塊,為讓新手工程師更快的將 UART 串口 WiFi 模塊應(yīng)用于各類(lèi)智能家居應(yīng)用中,本篇 SKYLAB 君簡(jiǎn)單為大家介紹 UART 串口 WiFi 模塊的工作原理及應(yīng)用。

2019-01-08 08:00:00 23

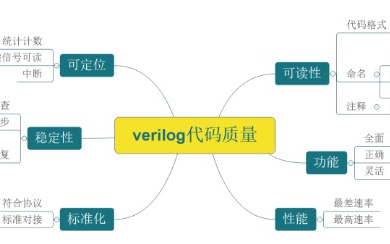

23 高質(zhì)量的verilog代碼主要包含以下幾個(gè)要素:可讀性、功能、性能、標(biāo)準(zhǔn)化、穩(wěn)定性、可定位。

2019-03-30 10:12:53 1780

1780

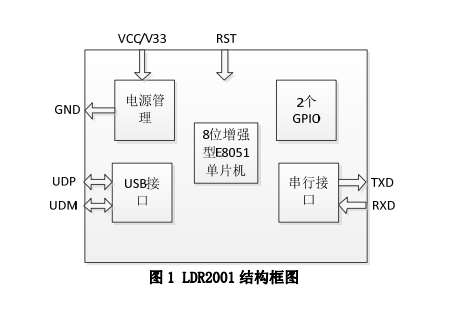

Face-RK3399 外置3個(gè)增強(qiáng)功能串口(UART)的功能,分別為UART1,UART2,RS485。

2019-12-04 09:04:47 8003

8003 AIO-3288C 開(kāi)發(fā)板支持SPI橋接/擴(kuò)展4個(gè)增強(qiáng)功能串口(UART)的功能,分別為RS232,RS485和1個(gè)調(diào)試串口UART2。

2019-12-16 14:18:55 1242

1242 本文檔的主要內(nèi)容詳細(xì)介紹的是使用verilog語(yǔ)言配合sopc和nios實(shí)現(xiàn)串口調(diào)試的代碼和工程文件免費(fèi)下載。

2021-01-22 16:58:00 9

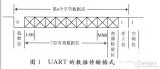

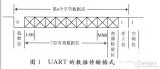

9 代碼注釋有些匆忙,如有錯(cuò)誤注釋還請(qǐng)批評(píng),僅作參考 UART Uart比較簡(jiǎn)單,所以?xún)H對(duì)tx作比較詳細(xì)的注釋?zhuān)锩嬉恍﹥?nèi)容還是值得新手學(xué)習(xí)的 1開(kāi)始位(低電平)+8位數(shù)據(jù)+1停止位(高電平,這里

2021-05-27 18:05:00 2173

2173 通過(guò)Verilog在SRAM讀寫(xiě)程序源代碼

2021-06-29 09:26:15 7

7 8位串轉(zhuǎn)并并轉(zhuǎn)串verilog代碼代碼+testbeach文件(新星普德電源技術(shù)有限)-8位串轉(zhuǎn)并,并轉(zhuǎn)串verilog代碼,代碼+testbeach文件,適合感興趣的學(xué)習(xí)者學(xué)習(xí),可以提高自己的能力,大家可以多交流哈

2021-09-16 14:55:13 11

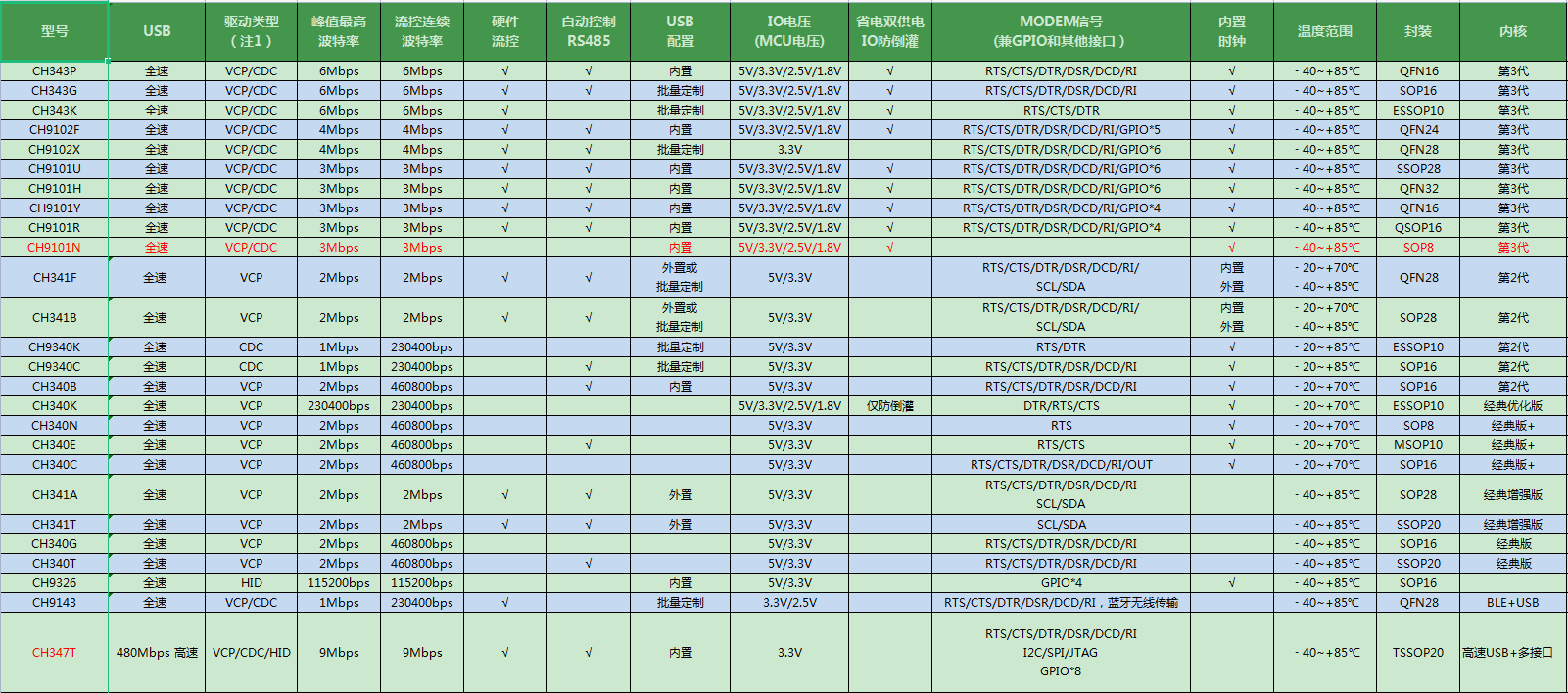

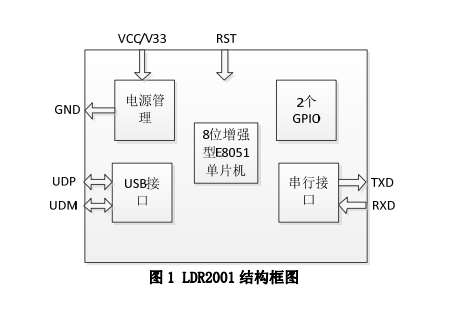

11 市面上的USB轉(zhuǎn)UART串口芯片,都是需要通過(guò)安裝驅(qū)動(dòng),比較繁瑣,樂(lè)得瑞新推出USB轉(zhuǎn)UART串口芯片,電腦免裝驅(qū)動(dòng),即接即用,非常簡(jiǎn)單。

2021-10-13 17:18:35 4443

4443

近來(lái)在一個(gè)項(xiàng)目開(kāi)發(fā)中,在一個(gè)新的硬件平臺(tái)下的linux系統(tǒng),使用uart串口進(jìn)行通訊,結(jié)果通訊不暢。代碼是以前在其他硬件平臺(tái)下驗(yàn)證完全沒(méi)問(wèn)題的代碼,為什么會(huì)出問(wèn)題呢?經(jīng)過(guò)各方面查資料,最終定位

2021-11-01 17:37:21 14

14 UART串口通信 串行通信是將數(shù)據(jù)按位發(fā)送的通信機(jī)制。比如:101010100,用0-0-1-0-1-0-1-0-1來(lái)發(fā)送,每次只發(fā)一位,所以速度是比較慢的。而UART串口通信則是串行通信的一種

2021-11-10 21:06:03 19

19 【MSP430單片機(jī)】UART串口篇

2021-11-19 16:21:22 14

14 藍(lán)橋杯STC基礎(chǔ)代碼上一章-藍(lán)橋杯STC基礎(chǔ)代碼-基礎(chǔ)外設(shè)串口原理圖串口的代碼配置下一章-時(shí)鐘芯片-DS1302上一章-藍(lán)橋杯STC基礎(chǔ)代碼-基礎(chǔ)外設(shè)上一章講了開(kāi)發(fā)板上面最基礎(chǔ)的外設(shè),led 數(shù)碼管

2021-11-22 19:21:03 18

18 單片機(jī)UART串口通信單片機(jī)的串口通信,一般指的就是UART串口通信(TXD,RXD)。本文實(shí)現(xiàn)的是單片機(jī)和電腦之間的串口通信,需要用到51單片機(jī)開(kāi)發(fā)板,電腦,STC-ISP軟件,代碼已調(diào)試

2021-11-23 17:36:25 18

18 ESP32 之 ESP-IDF 教學(xué)(九)—— 串口通信(UART)文章目錄ESP32 之 ESP-IDF 教學(xué)(九)—— 串口通信(UART)一、ESP32 的 UART 概覽1、簡(jiǎn)介2、UART

2021-11-26 13:21:03 42

42 C51的UART 串口通信

2021-11-29 12:21:04 9

9 STM32F407的串口UART 基礎(chǔ)配置STM32CubeMX

2021-11-29 16:06:07 51

51 一、常見(jiàn)串口? 常見(jiàn)的串口有UART口(Universal Asynchronous Receiver Transmitter:通用異步收發(fā)器, 一對(duì)一,以位為單位發(fā)送)和COM( cluster

2021-12-20 19:26:05 2

2 多少伏為邏輯“1”)和接口機(jī)械特性(形狀,針腳定義)等內(nèi)容。COM口多見(jiàn)于舊式電腦,用于連接鼠標(biāo),調(diào)制調(diào)解器等設(shè)備,現(xiàn)在已被USB取代。UART與USART(TTL串口) UART,全稱(chēng)Universal Asynchronous Receiver/Transmitter,通用異步...

2021-12-20 19:27:18 15

15 UART串口通訊總結(jié)前言串口的基本概念串口配置的基本屬性串口(Serial port)和RS-232串口通訊流控制前言此篇文章為轉(zhuǎn)載,轉(zhuǎn)載地址為uart串口通訊總結(jié)串口的基本概念UART全稱(chēng)

2021-12-20 19:31:34 23

23 藍(lán)橋杯單片機(jī)學(xué)習(xí)過(guò)程記錄(二十)UART串口通信今天學(xué)習(xí)了串口通信UART部分,理解得還不夠深刻,總體來(lái)說(shuō)感覺(jué)比IIC等簡(jiǎn)單一些,通用異步收發(fā),實(shí)現(xiàn)發(fā)送接收指令控制的基礎(chǔ)內(nèi)容。實(shí)現(xiàn)代碼如下

2021-12-23 19:10:59 14

14 STM32L0 HAL庫(kù) UART 串口讀寫(xiě)功能串口發(fā)送功能:uint8_t TxData[10]= “01234abcde”;HAL_UART_Transmit(&huart2

2021-12-27 19:11:54 13

13 實(shí)驗(yàn)?zāi)繕?biāo)配置TM4C123G的板載UART串口,使其能用類(lèi)似printf的函數(shù)與輸出字符到電腦端。配置過(guò)程1、TM4C123G的串口結(jié)構(gòu)圖2、引腳映射表3、開(kāi)發(fā)板原理圖4、配置流程和相關(guān)函數(shù)從上

2021-12-28 19:02:26 22

22 STM32串口通信HAL庫(kù)配置中 UART_IT_xx與UART_FLAG_xx 的區(qū)別:(最后有個(gè)疑問(wèn)希望路過(guò)的大佬幫忙解答一下。)UART_IT_xx剛開(kāi)始疑惑的時(shí)候,發(fā)現(xiàn)網(wǎng)上都沒(méi)有

2021-12-28 19:05:50 2

2 UART串口通信軟件推薦在我們調(diào)試單片機(jī)的時(shí)候,經(jīng)常用到UART串口通信(沒(méi)有足夠的資金購(gòu)入LCD屏、OLED屏等顯示器件)。市面上這么多的串口調(diào)試軟件實(shí)在是讓人無(wú)從下手,下面安利3款串口調(diào)試軟件

2021-12-29 19:34:56 1

1 UART串口一、I.MUX6ULL串口UART1、串口原理2、I.MUX6U的UART時(shí)鐘源設(shè)置3、I.MUX6U的UART波特率設(shè)置4、其他UART的寄存器的主要功能介紹二、部分例程代碼

2022-01-12 20:14:59 0

0 一、UART簡(jiǎn)介1、UART(Universal Asynchronous Receiver Transmitter)總線是異步串口,故一般比I2C、SPI兩種同步串口的結(jié)構(gòu)要復(fù)雜很多,一般由波特率

2022-01-17 13:00:58 3

3 為了讓大家充分理解 UART 串口通信的原理,我們先把 P3.0 和 P3.1 當(dāng)做 IO 口來(lái)進(jìn)行模擬實(shí)際串口通信的過(guò)程,原理搞懂后,我們?cè)偈褂眉拇嫫髋渲脤?shí)現(xiàn)串口通信過(guò)程。

2022-02-09 10:25:06 23

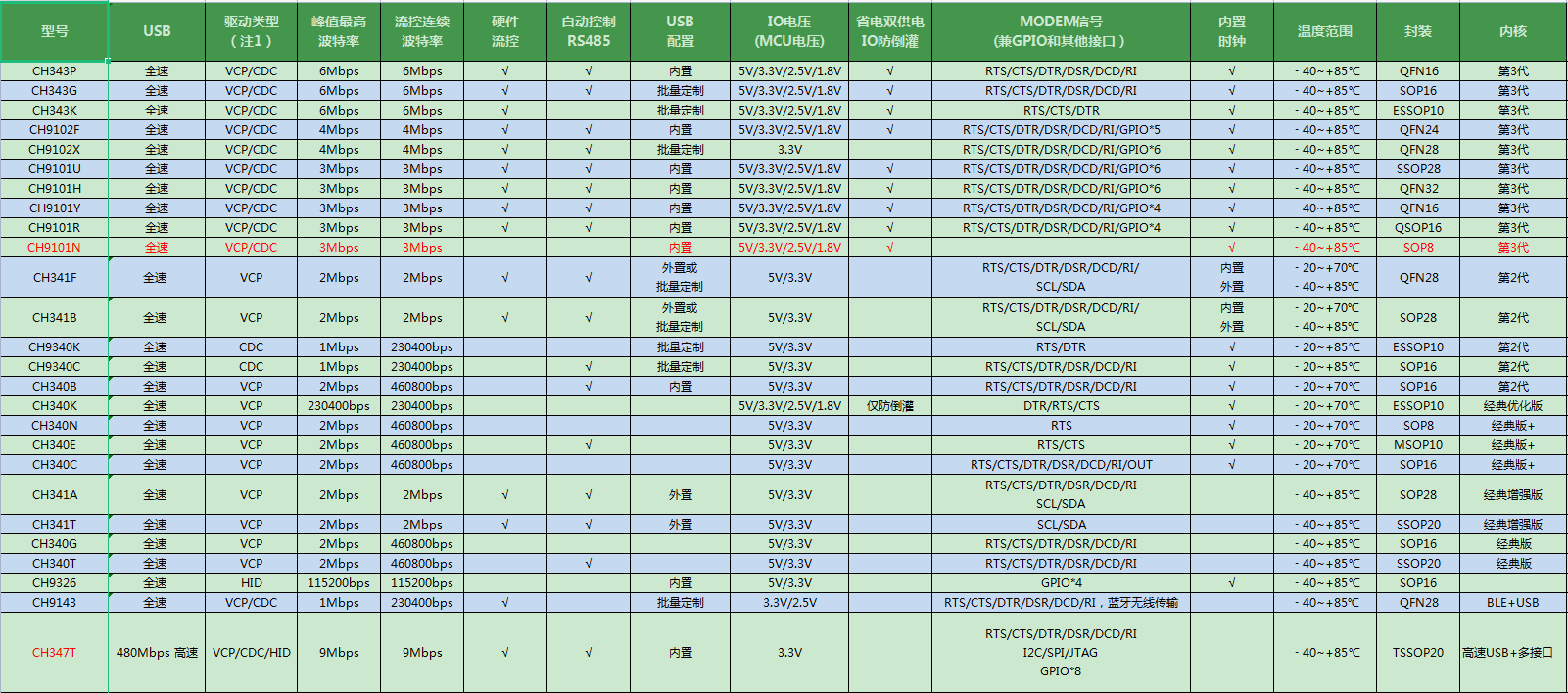

23 沁恒微USB轉(zhuǎn)單串口及多串口芯片選型表,和PIN TO PIN 型號(hào)表, 和串口、COM口、UART口, TTL、RS-232、RS-485的區(qū)別講解

2022-09-07 10:09:37 4592

4592

寫(xiě)代碼是給別人和多年后的自己看的。 關(guān)于Verilog代碼設(shè)計(jì)的一些風(fēng)格和方法之前也寫(xiě)過(guò)一些Verilog有什么奇技淫巧?

2022-10-24 15:23:54 1011

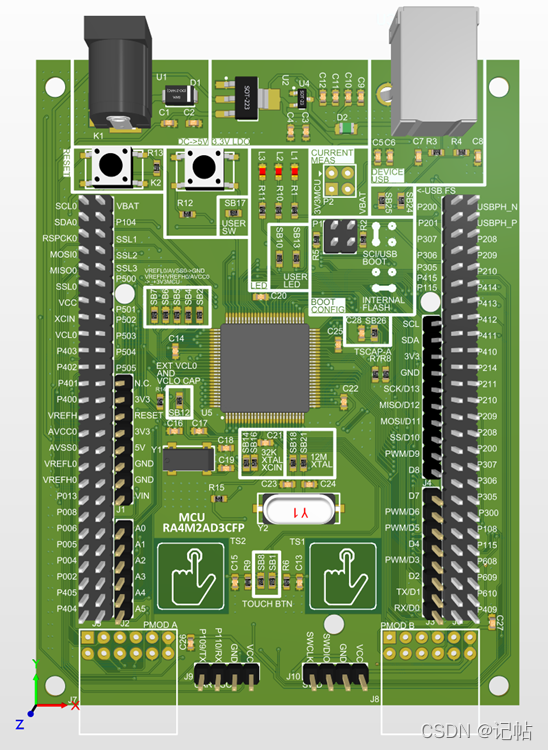

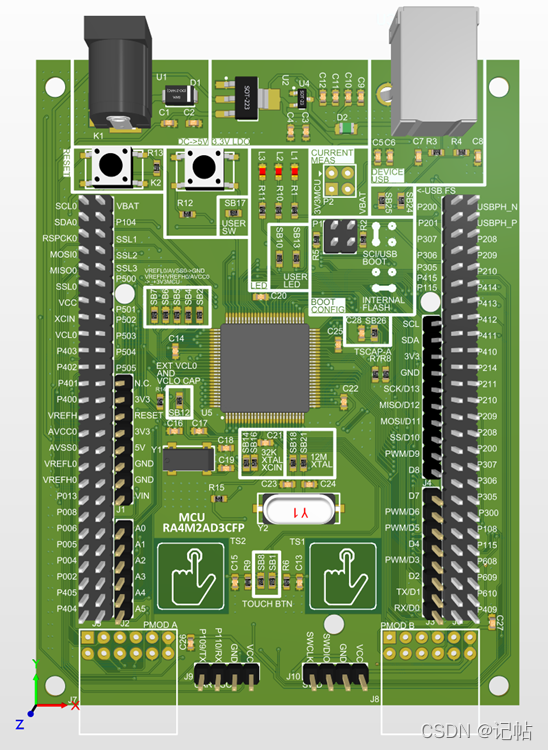

1011 本篇文章主要介紹如何使用UART串口燒寫(xiě)程序到瑞薩芯片,并以實(shí)際項(xiàng)目進(jìn)行演示。

2022-11-15 09:14:45 2071

2071

相對(duì)于verilog1995的端口定義,這種定義方式將端口方向,reg或wire類(lèi)型,端口位寬等信息都整合到了一起,減少了不必要的重復(fù)打字和出錯(cuò)幾率,也使得代碼長(zhǎng)度大大縮短,非常緊湊。

2022-12-22 14:33:23 561

561 串口通訊源代碼

2023-02-22 18:17:30 3

3 首先我們先添加相應(yīng)的頭文件。既然我們要進(jìn)行對(duì)串口的模擬,因此我們要先了解uart相關(guān)的通信協(xié)議。由于UART的通信方式是由1個(gè)起始位,8個(gè)數(shù)據(jù)位,包含一個(gè)奇偶校驗(yàn)位,和結(jié)束位構(gòu)成因此我們將使用單片機(jī)中的兩個(gè)普通的IO口電平的高低進(jìn)行對(duì)相應(yīng)時(shí)序的模擬。

2023-03-22 15:56:40 3605

3605 在做UART串口通信的電路中,比較常見(jiàn)的是在串口的TX/RX端,串聯(lián)一個(gè)1k的電阻。

2023-03-23 10:44:56 9178

9178

我們將介紹如何使用verilog參數(shù)和generate語(yǔ)句來(lái)編寫(xiě)可重用的verilog 代碼。

與大多數(shù)編程語(yǔ)言一樣,我們應(yīng)該嘗試使盡可能多的代碼可重用。這使我們能夠減少未來(lái)項(xiàng)目的開(kāi)發(fā)時(shí)間

2023-05-11 15:59:21 647

647 本文將從Verilog和邊沿檢測(cè)的基本概念入手,介紹Verilog邊沿檢測(cè)的原理和應(yīng)用代碼示例。

2023-05-12 17:05:56 2183

2183

本文主要介紹ROM和RAM實(shí)現(xiàn)的verilog代碼版本,可以借鑒參考下。

2023-05-16 16:57:42 799

799 電子發(fā)燒友網(wǎng)站提供《Verilog中Pmod ALS的SPI接口代碼.zip》資料免費(fèi)下載

2023-06-15 09:32:52 0

0 本篇文章主要介紹如何使用UART串口燒寫(xiě)程序到瑞薩芯片,并以實(shí)際項(xiàng)目進(jìn)行演示。

2021-11-03 17:36:12 1622

1622

關(guān)于仿真里的后門(mén)訪問(wèn),之前的文章《三分鐘教會(huì)你SpinalHDL仿真中的后門(mén)讀寫(xiě)》中有做過(guò)介紹,其針對(duì)的都是針對(duì)以SpinalHDL中的代碼進(jìn)行的后門(mén)訪問(wèn)。今天來(lái)看看當(dāng)封裝了Verilog BlackBox時(shí),在SpinalHDL仿真中如何進(jìn)行后門(mén)訪問(wèn)Verilog代碼。

2023-07-15 10:22:02 460

460

注:以R起頭的是對(duì)編寫(xiě)Verilog代碼的IP設(shè)計(jì)者所做的強(qiáng)制性規(guī)定,以G起頭的條款是建議采用的規(guī)范。每個(gè)設(shè)計(jì)者遵守本規(guī)范可鍛煉命名規(guī)范性。

2023-08-15 16:23:41 1089

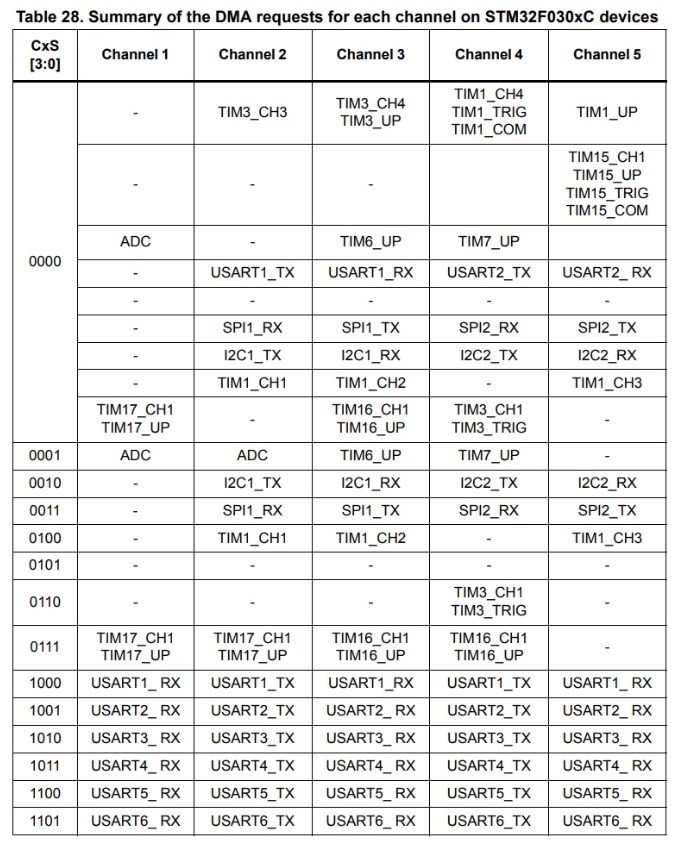

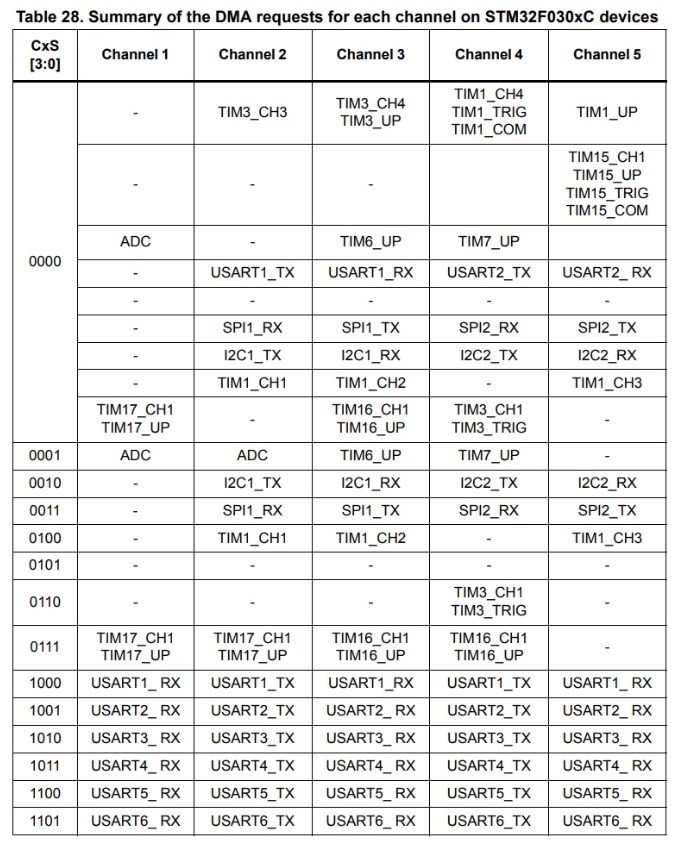

1089 看了大家對(duì)F030復(fù)用串口的疑惑,這里繼續(xù)給出“當(dāng)同時(shí)使用UART3~UART6中的多個(gè)串口時(shí),由于其中斷響應(yīng)函數(shù)都是同一個(gè),需要自己在中斷函數(shù)USART3_6_IRQHandler() 中判斷是來(lái)自哪個(gè)串口的中斷。”這個(gè)問(wèn)題的解決辦法。

2023-10-13 14:14:03 556

556

UART (Universal Asynchronous Receiver/Transmitter) 是一種通信接口協(xié)議,用于實(shí)現(xiàn)串口通信。它是一種簡(jiǎn)單的、可靠的、廣泛應(yīng)用的串口通信協(xié)議。它是由美國(guó)

2024-03-19 17:26:10 48

48

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論