隨著現代軍事通信技術的進步,數字化短波電臺逐步往嵌入式、模塊化的方向發展。CPCI總線作為一種新興的總線技術,在短波電臺的模塊化設計上具有重要的應用價值,可以較大程度地提高數字化短波電臺的可靠性和保障性。

CPCI總線架構

CPCI規范是由PICMG(PCI Industrial Computer Manufacturer’s Group,PCI工業計算機制造商聯盟)制定的一種新的開放工業計算機標準,用于工業和嵌入式應用。它定義了更加堅固耐用的PCI版本,在電氣、邏輯和軟件功能等方面,與PCI標準完全兼容。

CPCI全稱Compact PCI,簡單的說就是PCI specification(PCI電氣規范)加上rugged Eurocard packaging(歐式卡)結構。CPCI模塊以插卡的方式安裝在機箱內的支架上,并采用垂直方向通風散熱,具有更好的散熱性和抗震動性。這樣,在CPCI系統中就可采用在臺式機中廣泛使用的高性能PCI技術,降低了新技術的使用成本,系統的整體性能得以提升。而且,基于PCI技術的豐富軟件工具,也使得用戶在使用中更加便捷。同時,歐式卡結構使得系統的可靠性進一步提高。另外采用IEEE 1101.11后端輸出方式,使得對系統的維護更加方便快捷,大大縮短了系統的平均維護時間。

CPCI系統背板和CPCI板卡采用的是標準2mm高密度氣密性針孔連接器,板卡的尺寸分3U(100mm×160mm)和6U(160mm×233mm)兩種,3U的系統只提供32位/64位的PCI系統總線,6U的系統除了提供32位/64位的PCI系統總線外,還有多達315線的用戶定義輸入/輸出線,非常適用于數字化短波電臺的模塊化設計應用。CPCI總線具有極高的性能,其主要特點是:

(1)具有地址數據多路復用的高性能32位或64位的同步總線。總線引腳數目和部件數量少(對于總線目標設備只有47根信號線,對于主設備最多只有49根信號線),降低了成本及布線復雜度。

(2)CPCI局部總線在33MHz總線時鐘、32位數據通路時,可達到峰值132Mb/s的帶寬;在33MHz總線時鐘,64位數據通路時可達到峰值264Mb/s的帶寬;在66MHz主頻時,對于32位數據通路和64位數據通路帶寬的峰值,可分別達到264Mb/s或528Mb/s的帶寬;CPCI總線還有線性突發傳輸功能,保證了滿載的高速傳輸。

(3)隱蔽的總線仲裁,減小了仲裁開銷。

(4)極小的存取延時,采用總線多主控和異步數據轉移操作。

(5)CPCI提供的數據和地址奇偶校驗功能,保證數據完整性和準確性。

(6)CPCI總線與CPU和時鐘頻率無關,它能支持多個外設,設備間通過局部總線可以完成數據快速傳遞,從而很好地解決數據傳輸的瓶頸問題。

(7)對CPCI擴展卡及元件,能夠自動配置,實現設備的即插即用。

從結構上看,CPCI總線的特點表明它是一種理想的系統交換平臺的載體,能提供高傳輸帶寬,同時能夠保證數據完整性和準確性;能夠支持多外設,很好地適應了系統可擴展性的要求;采用的是PCI總線操作規程,很好地適應了一般的PCI擴展元件,降低了開發難度;獨特的引腳及外圍電路設計集連接緊密牢固、抗干擾、易更換、熱插拔等優點于一身。背板是CPCI總線架構的基礎,它為CPCI總線交換提供物理連接、電路保證。CPCI背板有8個插槽,其中一個為系統板插槽(system slot),其他7個為外設板插槽(peripheral slot),像這樣一個系統插槽外帶7個外設插槽的單元稱為一個CPCI段(CPCI segment)。系統插槽提供總線仲裁、時鐘分配和整個CPCI段的重新啟動等功能,系統插槽要通過管理每塊外設插槽上板卡的IDSEL信號來完成整個系統的初始化;外設插槽上可以安放簡單的接口板、智能從屬裝置(intelligence slave)或PCI總線控制裝置(PCI master)。

CPCI總線接口設計

為了提高數字化短波電臺的數據處理能力,可以為其配置ETX嵌入式計算機模塊。雖然ETX嵌入式計算機模塊定義了符合PCI規范的CPCI總線,但由于如上所述的電氣負載的原因,對于PCI/CPCI總線而言,如果總線上連接過多的電氣負載或設備,總線將不能正常工作。在不擴充總線的情況下,標準PCI總線的驅動能力是驅動4個PCI插槽,而CPCI控制器模塊要求驅動7個儀器模塊。因此,即使采用PCI插卡到CPCI插座的物理結構轉換后,嵌入式計算機模塊的PCI總線主橋路仍然不能直接驅動CPCI總線。所以在設計數字化短波電臺的CPCI總線時,需要在ETX嵌入式計算機的CPCI總線和CPCI機箱底板的CPCI總線之間引入了PCI-PCI橋接設備。

1 橋接芯片的選擇

PCI橋接芯片盡管可以使用FPGA通過硬件編程語言來實現,但由于PCI總線規范自身的復雜性,要想在短期內做到性能優化和操作穩定,難度很大。而現在市場上有許多廠家提供了很多成熟的產品,根據系統集成的特性,我們選擇TI公司的PCI-to-PCI橋接芯片PCI2050。

PCI2050屬于透明PCI-to-PCI橋,提供了兩條PCI總線間的高性能連接,實現一條PCI總線的主設備和另外一條PCI總線的從設備間的傳輸,兼容Intel 21150。PCI2050橋符合PCI局部總線規范2.2,并可用于PCI總線的擴展,提供支持9個設備的可編程2優先級總線仲裁器;一次側和二次側都支持33MHz時鐘、32位擴展信號。PCI2050提供CPCI熱插拔能力,可完美解決多功能CPCI卡和單功能CPCI的熱插拔問題。PCI2050橋符合PCI-to-PCI Bridge Specification1.1,符合PCI電源管理規范1.0/1.1。

2 電源和地的連接

PCI2050使用的核心工作電壓為+3.3V,CPCI標準機箱的底板上通過J1連接器提供滿足要求的+3.3V電壓,在使用時無須DC/DC轉換。但根據標準設計規范,在PCI2050的電源引腳附近需要設置旁路電容。所以在印制電路板布線時,在PCI2050的所有電源引腳附近需要設置一個0.1μF的陶瓷電容器作為旁路電容。

PCI2050在兩側總線方向都支持+5V和+3.3V信號環境,它們的選擇是通過對P_VCC和S_VCC引腳施加不同的電壓來實現的,詳細的選擇方式如表1所示。

由于PCI總線為高速總線,為了避免電源和地的干擾,在印制板布線時采取單獨的電源層和地層布線。但因為在設計過程中使用了+5V和+3.3V兩種電源,所以在同一電源層上又為+5V和+3.3V兩部分分開鋪銅。

3 PCI總線一次側的連接

數字化短波電臺的嵌入式計算機模塊提供了符合PCI總線規范的標準PCI信號接口,這些信號與PCI2050的第一級總線側的信號定義完全兼容,在設計時可以將嵌入式計算機的PCI信號輸出直接連接到PCI2050一次側的相應引腳。在初始化配置空間讀寫時,PCI2050作為上一級PCI總線的操作對象,提供了IDSEL引腳進行器件選擇,按照PCI2050使用手冊,該引腳可以連接到高24位PCI總線中的任意一根。同時,為了減低地址線的容性負載,需要在該信號連線上串接一個1kΩ的電阻。

在CPCI總線設計中,將PCI2050的IDSEL引腳通過1kΩ電阻連接到了AD19引腳。同樣,PCI2050在二級總線側可以支持9個PCI器件,對于每個二級總線側的PCI器件的IDSEL引腳,也可以經過1kΩ電阻連接到PCI2050的S_AD31-S_AD16引腳中的任意一根。

4 PCI總線二次側的連接

PCI總線信號經過橋接,在PCI2050的二級總線側提供了標準的次級PCI總線接口信號,它們符合PCI總線規范的定義,同CPCI底板上的相應信號的定義也是相同的。但根據CPCI規范和PCI2050手冊的要求,這些信號線需要經過適當的調理后才能與相應的CPCI J1、J2連接器的對應信號連接。

① 根據CPCI規范的要求,為了減小單板上的CPCI總線的信號線分支(stub)對總線的影響,必須對總線信號進行串聯電阻匹配。PCB的布線特征阻抗應設計為65Ω±10%,匹配電阻阻值為10Ω。需要加串聯匹配電阻的信號包括:AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#以及INTA#、INTB#、INTC#、INTD#。而且,從接插件J1或J2到PCI2050相應管腳,總的信號線長度要小于63.5mm(2.5英寸)。其中,從接插件插針到串聯電阻的PCB連線長度小于15.2mm(0.6英寸)。所以,對上述信號在實際中使用10Ω排阻作為端接終端電阻進行串聯的匹配。

② 在CPCI總線的設計中,對于GNT#0~GNT#6、REQ#0~REQ#6和二級時鐘輸出SCLKOUT0~SCLKOUT6等引腳根據CPCI規范對系統卡的要求,也需要加上相應的10Ω端接終端電阻。

③ 根據規范要求,對CPCI總線接口來說,對系統卡的一些PCI信號輸出需要進行上拉,且上拉電阻必須被放置在端接終端電阻靠近CPCI J1、J2連接器的一側上。可以在設計時對PCI2050的二級總線側的相應信號通過8.2kΩ電阻上拉。需要上拉的電阻包括:FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#、INTA#、INTB#、INTC#、INTD#、GNT#0~GNT#9、REQ#0~REQ#9等。

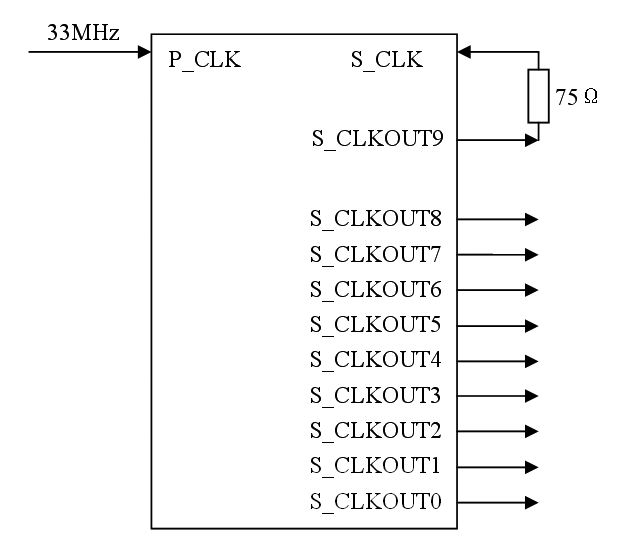

④ 對于二級時鐘輸出,PCI2050的二次側有10個時鐘輸出S_CLKOUT[0..9],這些時鐘輸出可以通過相關寄存器分別使能。同時,為了保證PCI2050的二級PCI總線時鐘和其他時鐘輸出同步,應將S_CLK引腳經一個75Ω電阻反饋到S_CLKOUT9引腳,如圖1所示。

圖1? PCI2050的時鐘連接

⑤ PCI2050提供的JTAG邊界掃描接口TDI、TDO、TMS、TCLK、TRST#,這些引腳可以與CPCI規范定義的J1連接器上的相應引腳直接連接。

⑥ 對于二級總線的仲裁,PCI2050提供兩種方式:外部總線仲裁和內部總線仲裁。S_CFN#引腳為選擇引腳,當S_CFN#引腳為高時,使用外部總線仲裁器。這時,S_REQ#1~S_REQ#8和S_GNT#1~S_GNT#8引腳被置為高阻狀態,外部仲裁器與PCI2050的連接方式如圖2所示。

圖2 PCI2050與外部仲裁器的連接

在PCI2050的內部總線仲裁模式中,S_CFN#引腳為低,PCI2050對外圍卡通過S_REQ#0~S_REQ#8引腳提出的請求進行仲裁,然后通過S_GNT#0~S_GNT#8引腳和進行響應。PCI2050的S_REQ#0~S_REQ#8和S_GNT#0~S_GNT#8引腳分別與CPCI規范定義的CPCI J1、J2的相應引腳經過串接端接電阻和上拉后連接。

5 芯片工作模式的選擇

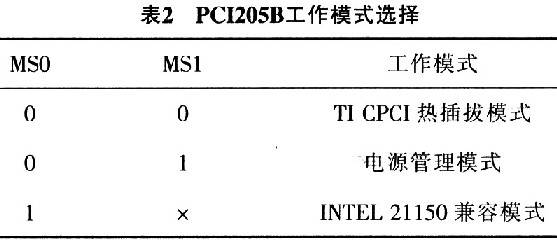

PCI2050可以選擇工作在三種不同的工作模式下:TI CPCI熱插拔模式、TI電源管理模式和與Intel 21150兼容模式。選擇引腳分別為:MS0、MS1,模式選擇定義如表2所示。

TI CPCI熱插拔模式支持CPCI熱插拔,滿足CPCI電源管理接口規范1.1版本;TI電源管理模式不支持CPCI熱插拔,只滿足CPCI電源管理接口規范1.1版本;與Intel 21150兼容模式也不支持CPCI熱插拔,且只滿足CPCI電源管理接口規范1.0版本。根據CPCI總線應用設計的需要,可以選擇TI CPCI熱插拔工作模式。

當PCI2050選擇工作在TI CPCI工作模式下時,為了確保熱插拔邏輯的正常工作,要求必須將PCI2050的HS_SWITCH/GPIO3和HSENUM#引腳上拉。同時,由于沒有使用PCI2050的關于GPIO的引腳,且因為這些引腳在缺省條件下定義為輸入腳,為了避免誤觸發,應該將這些引腳全部上拉。

6 芯片內部寄存器設置

PCI2050橋接芯片作為一個獨立功能的PCI器件,具有和所有PCI設備一樣的配置空間,并且作為PCI橋,它遵守PCI-to-PCI橋規范1.1所定義的PCI配置空間。PCI2050除了具有標準的PCI-to-PCI橋規范定義的配置空間外,還具有TI特有的寄存器組(40h-FFh)。這些寄存器組包含PCI2050某些特有功能的控制位,在PCI2050的應用中起特殊控制作用。但在本設計中,根據系統實際應用需求,對PCI2050的內部寄存器不需要進行特別操作,可以使用其缺省值。

結論

基于PCI2050橋接芯片的CPCI總線設計在數字化短波電臺中的應用比較穩定可靠,為數字化短波電臺提供了豐富的可插拔插槽。CPCI總線的標準化規范也為數字化短波電臺的模塊化設計和功能擴展提供了便利,并且還極大地提高了電臺的可操作性、維修性和保障性,使數字化短波電臺能更好地適應各種復雜的應用環境。

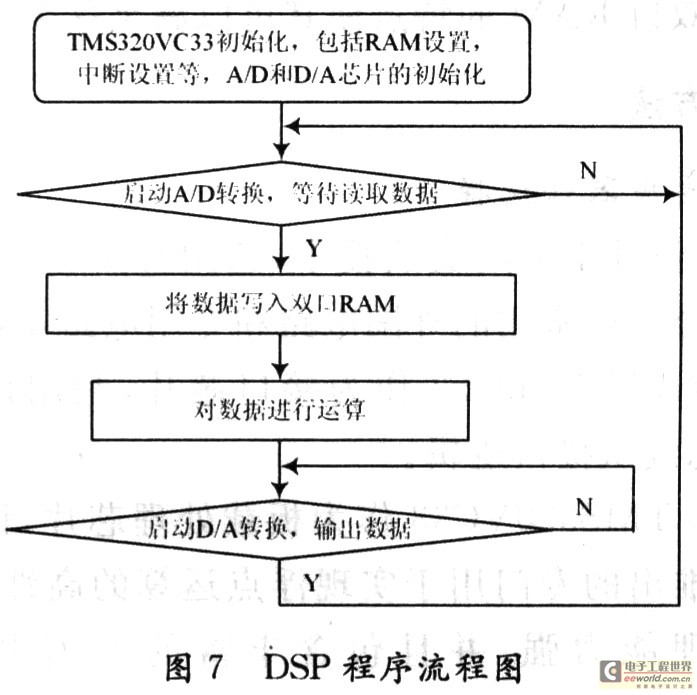

電子發燒友App

電子發燒友App

評論