AD9054 高速A/D采集技術已在許多領域得到愈來愈廣泛的應用,本文將詳細論述采用CPLD技術來實現120MHz高速A/D采集卡的設計方法,該采集卡具有包括負延遲觸發在內的多種觸發方式,采用

2019-01-07 08:44:00 5713

5713

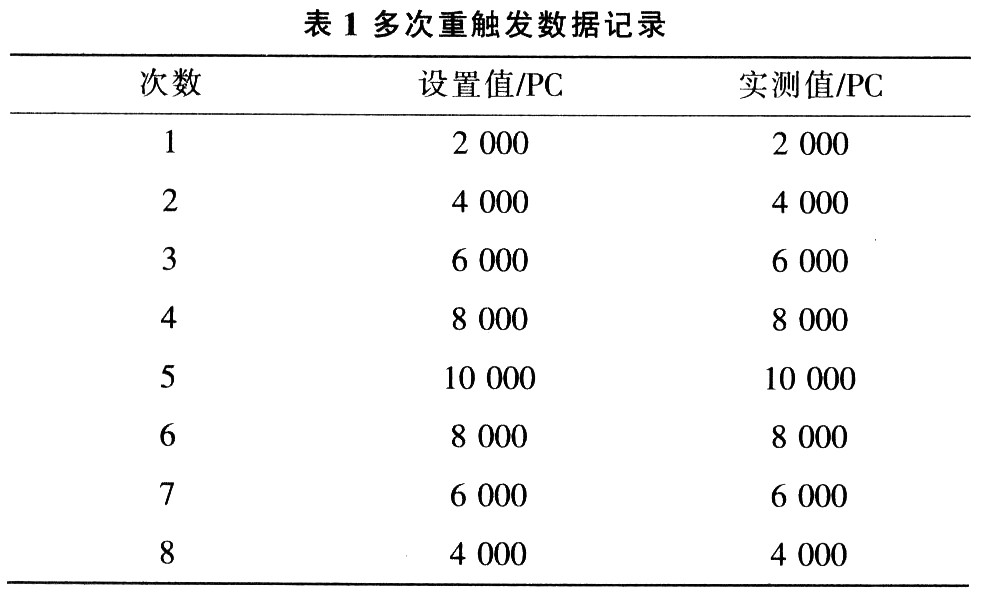

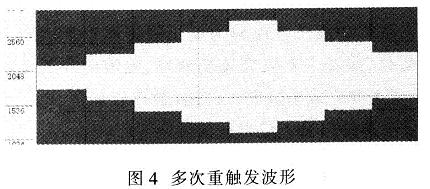

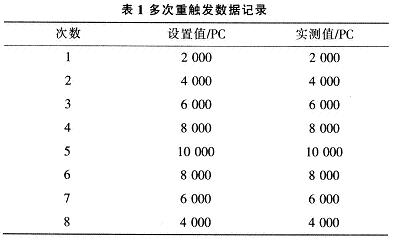

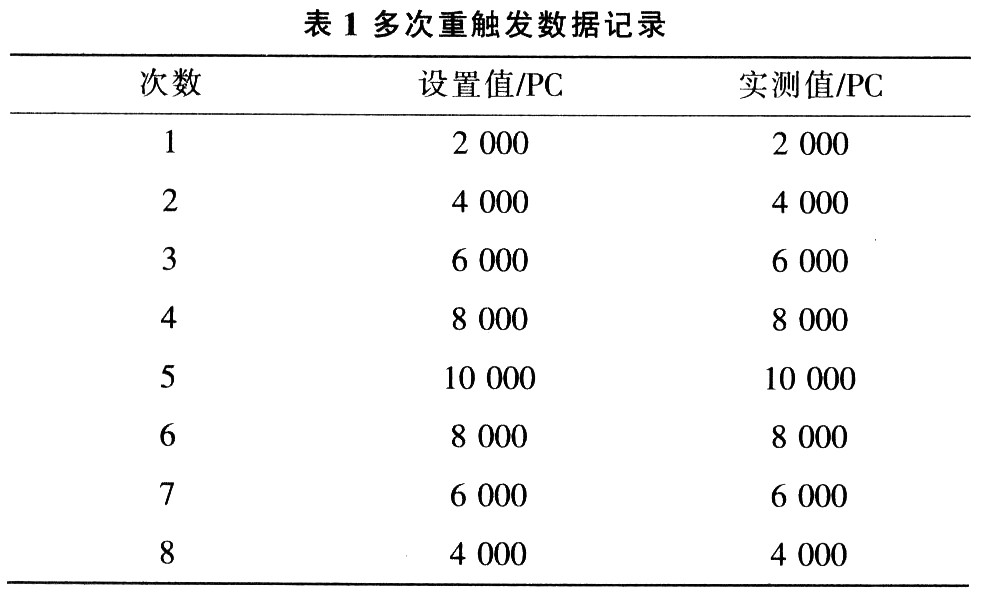

態記錄無意義。為此開發多次重觸發技術,以齒應力作為內觸發信號,只記錄每次觸發后的有用信號,并具有負延遲,而不記錄空閑狀態.直到占滿記錄裝置存儲空間,這樣可有效利用存儲空間,記錄更多的有用信號。

2020-08-14 15:39:18 520

520

抗干擾能力是系統設計的關鍵。根據汽車制動力測量精度的要求和整個系統的控制邏輯提出了采用單片機和CPLD 雙控制器的總體方案,并根據所要實現的功能設計了軟件。而濾波和抗干擾是任何智能儀器系統都必須考慮

2009-04-16 13:56:57

我做了觸發采集,運行程序可以每次進行采集,但是現在有個想法,就是想進行多次采集,如10次。假設我輸入10,程序可以進行10次的采集,而不是我點擊了10次程序運行而進行10次的采集。不知道,大俠們有沒有什么好的建議。非常感謝!

2015-06-07 09:04:31

充分利用了邏輯資源,還能使系統設計顯得更加緊湊。文中主要介紹了采用CPLD實現32 bit 33MHzPCI從設備接口的設計方法,該從設備接口模塊遵從PCI規范2.2版,實現了資源的自動配置,支持突發傳輸

2019-06-20 05:00:03

,該模塊的工作過程如下:在系統啟動信號CtrlBegin有效之后,啟動AD轉換信號(/CONVST置低);在轉換過程中,將數據緩沖區(由CPLD內部實現的一個16Bit的存儲器)中的前一次轉換結果寫入

2019-05-23 05:01:08

的數據存儲器,這是他相對于標準51內核的最大優點。目前的單片系統越來越復雜,擴展的外部設備也更多,如果能充分利用P89C669的豐富的線性地址資源,將能大大增強系統能力。在一個嵌入式系統開發中,筆者采用

2008-07-29 09:18:18

、布線繁雜。盡管用的是表貼器件,但仍占相當大PCB面積,由引腳松動、虛焊等原因引發的故障率較高。采用CPLD器件后,接口電路全部集成在一片中,系統的可靠性、靈活性大大提高。復雜可編程邏輯器件因其使用方便、具有很高的性價比,必將擁有廣闊的應用前景。

2019-05-31 05:00:03

的是表貼器件,但仍占相當大PCB面積,由引腳松動、虛焊等原因引發的故障率較高。采用CPLD器件后,接口電路全部集成在一片中,系統的可靠性、靈活性大大提高。復雜可編程邏輯器件因其使用方便、具有很高的性價比,必將擁有廣闊的應用前景。

2019-06-05 05:00:14

針對基于SRAM工藝的器件的下載配置問題,本文介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行(PS)模式的下載配置。

2021-04-13 06:25:40

基于magnum II測試系統的測試技術研究,提出了采用magnum II測試系統的APG及其他模塊實現對MRAM VDMR8M32進行電性測試及功能測試。其中功能測試包括全空間讀寫數據0測試,全空間讀寫

2019-07-23 07:25:23

的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續處理的要求。系統中采用 DSP+CPLD的硬件設計方案,采用現場可編程芯片 CPLD及兩片 SRAM構成的圖像采集和存儲系統,可以根據

2019-06-20 07:31:29

是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續處理的要求。系統中采用 DSP+CPLD的硬件設計方案,采用現場可編程芯片 CPLD及兩片 SRAM構成的圖像采集和存儲系統,可以根據

2019-07-26 07:16:41

是在邏輯塊下編程。④FPGA的集成度比CPLD高,具有更復雜的布線結構和邏輯實現。⑤CPLD比FPGA使用起來更方便。CPLD的編程采用E2PROM或FASTFLASH技術,無需外部存儲器芯片,使用簡單

2012-10-26 08:10:36

用CPLD實現。 (2)數據密集型,需要大量的數據處理能力,但邏輯相對簡單,對輸入要求少,適合FPGA實現。7、配置不同 CPLD:采用EPROM,E2PROM工藝,直接寫入,保密性好。 FPGA:采用SRAM工藝,故需外加ROM芯片,用于存儲配置信息。其保密性較差。可實現動態重構。高端FPGA具備加密功能

2020-08-28 15:41:47

M051 GPIO中斷采用邊沿觸發使能去防抖功能 修改了采樣周期依然出現多次中斷觸發有什么好辦法解決

2023-06-14 09:12:46

M051 GPIO中斷 采用邊沿觸發使能去防抖功能 修改了采樣周期依然出現多次中斷觸發有什么好辦法解決

2023-08-22 07:01:58

基于CPLD的數字存儲示波器摘 要:與傳統的模擬老婆婆以器相比,數字存儲示波器具有能夠顯示非周期波形、存儲波形、攜帶方便等優勢,其應用日益廣泛。本文詳細介紹了一種以單片機和可編程邏輯器件為控制...

2021-08-09 08:38:11

成本,而且還給系統軟件設計增加不必要的負擔。為此,提出了一種基于CPLD的雷達仿真信號的實現方案,它能為機載雷達測試系統提供所需的多種典型的重頻脈沖及制導信號。

2020-12-08 06:09:34

的測試系統應運而生。本文提出了一種多功能存儲器芯片的測試系統硬件設計與實現,對各種數據位寬的多種存儲器芯片(SRAM、MRAM、NOR FALSH、NAND FLASH、EEPROM等)進行了詳細的結口

2019-07-26 06:53:39

電子時鐘只能定一次鬧鈴,有沒有人知道如何實現多次鬧鈴啊,急急急。是只要在代碼上改,還是要擴展存儲器

2016-01-06 09:48:54

直流電動機的PWM控制原理是什么?如何采用CPLD實現數字控制PWM信號?如何利用CPLD技術實現了邏輯和時序的控制?

2021-05-07 06:03:34

采用CPLD實現信號濾波及抗干擾的方法,看完你就懂了

2021-04-13 06:40:47

請問如何采用CPLD和單片機實現任意波形發生器的設計?

2021-04-22 06:29:10

本文采用單片CPLD完成了以往需要大量外圍器件來完成的雷達并口數據收發及存儲功能。

2021-05-07 06:06:18

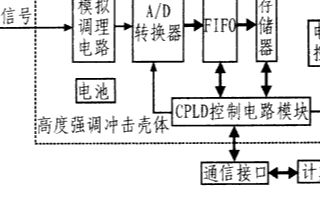

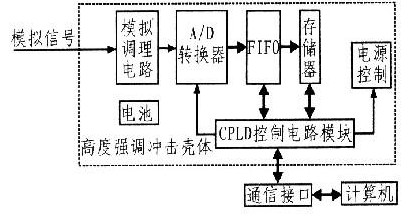

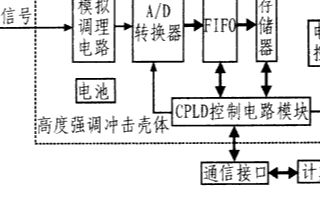

本文將詳細論述采用CPLD技術來實現120MHz高速A/D采集卡的設計方法,該采集卡具有包括負延遲觸發在內的多種觸發方式,采用CPLD復雜可編程邏輯器件(又稱FPGA)EPM7128SQC100-7和AD公司的高速模數轉換器(A/D)AD9054BST-135來實現。

2021-04-30 06:27:01

本文采用視頻解碼芯片與復雜可編程邏輯器件CPLD(Complex Programmable Logic Device)設計了一套實時圖像采集系統。

2021-06-15 07:47:20

如何采用Altera的CPLD器件實現時間統一系統的B碼源設計?

2021-05-07 06:21:24

求助各位大神如何使用ATE對CPLD進行測試???對CPLD進行測試的思路與流程是怎樣的?

2013-02-17 16:14:53

如何利用CPLD來實現對聲發射信號的采集,來有效解決數據的實時傳輸和存儲問題?

2021-04-13 06:28:32

本文根據國內外線纜測試技術的發展及生產企業的實際要求,設計了一種新型便攜式線纜組快速測試系統。該測試系統采用兩塊CPLD 用于接口電路,從而實現多組線纜(內有多條導線)同時測試,檢測線纜的通斷、短路和錯接情況,進而達到快速檢測線纜連通性能的目的。

2021-05-08 06:04:28

嗨, 我正在尋找具有內部存儲器的CPLD。我想將程序存儲在CPLD中,這樣每次打開電源時,我都不必重新編程IC。有沒有這樣的CPLD?謝謝,阿文德古普塔。

2019-08-06 08:27:34

應用cpld的光端機的實現,介紹了原理和系統框架,資料是河南恒茂的朋友提供的,給大家分享一下。

2014-06-10 09:00:41

本文在硬件電路設計上采用DSP 芯片和外圍電路構成速度捕獲電路,電機驅動控制器采用微控制芯片和外圍電路構成了電流采樣、過流保護、壓力調節等電路,利用CPLD實現無刷直流電機的轉子位置信號的邏輯換相

2021-05-12 06:44:08

本文選用FPGA實現數據處理、邏輯控制,充分利用PC機,結合Labwindows圖形化上層應用軟件界面生成的虛擬測試系統具有較強的競爭力。本系統在FPGA單板單片主控器件控制下,實現兩路獨立、幅值可控的信號發生器,一路虛擬存儲示波器,具有外部觸發信號和采樣時鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

基于MCU+CPLD變壓器測試系統的設計與實現,不看肯定后悔

2021-04-08 06:21:15

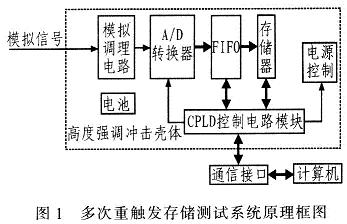

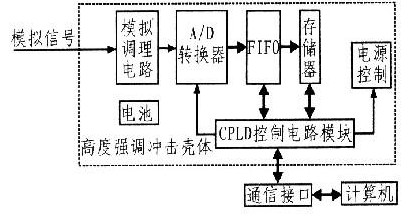

動態測試技術是以捕捉和處理各種動態信息為目的的一門綜合技術,它在當代科學技術中地位十分重要,在航天航空、儀器儀表、交通運輸、軍事、醫療等研究中均應用廣泛。常用的測試方法有遙測與存儲測試,與無線電遙測

2019-08-26 06:44:45

存儲在同一個存儲器的奇、偶地址位。雙蹤顯示時,先掃描奇地址數據位,再掃描偶地址數據位。采用模擬開關代替一個模數轉換器,避免兩片高速A/D轉換器相互干擾,降低系統調試難度,并且實現系統功能。3.3 觸發

2020-02-24 13:52:07

本文提出了一種基于CPLD的雷達仿真信號的實現方案,它能為機載雷達測試系統提供所需的多種典型的重頻脈沖及制導信號。

2021-05-06 06:19:25

如何實現CPLD的在系統編程?

2021-04-25 07:05:12

為了獲得一定的靈活性,嵌入式系統大都設計有可編程邏輯器件CPLD。利用單片機對CPLD進行編程,可以方便地升級、修改和測試已完成的設計。文中給出了它的實現過程。

2009-04-03 10:49:49 22

22 在單片機系統中使用CPLD,可使系統構成靈活,提高可靠性,縮短開發周期。介紹在MCS-51 應用系統中的CPLD 應用設計實例, 詳細分析CPLD 的應用和實現方法,提出設計中選用和使用CPLD

2009-05-14 13:49:49 39

39 介紹了采用CPLD 實現DSP 芯片TMS320C6713 和背板VME 總線之間高速數據傳輸的系統設計方法。設計中采用VHDL 語言對CPLD 進行編程。同時由于CPLD 的現場可編程特性,增強了整個系統

2009-08-15 08:39:23 51

51 介紹了基于CPLD 和EDA 技術的BIT(機內測試)系統的實現。本系統以CPLD 為控制核心,在MAX+PLUSII 環境下采用VHDL 語言實現了系統接口及測頻電路。該系統具有集成度高、靈活性強、易于開

2009-09-03 09:30:51 9

9 文章介紹了一個能夠輸出用于觸發發射機調制器的單次和多次受控脈沖觸發器的電路原理。多次脈沖的數目可以靈活控制。觸發器的使用可靠,工作性能穩定。敘詞:調制器,

2009-10-14 12:29:02 30

30 基于單片機的CPLD/FPGA被動串行下載配置的實現:介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設計。 &nb

2009-10-29 21:57:22 19

19 摘要:利用大規模可編程控制器(Complex Programmable Logic Device)CPLD.針對靜止補償器(STATCOM)對觸發脈沖信號的要求.設計一種基于CPLD的正弦脈寬調制(SPwM)數字觸發電路。正弦調制波的產

2010-05-14 09:33:55 21

21 在單片機系統中使用CPLD,可使系統構成靈活,提高可靠性,縮短開發周期。介紹在MCS-51應用系統中的CPLD應用設計實例,詳細分析CPLD的應用和實現方法,提出設計中選用和使用CPLD的

2010-07-14 14:04:25 39

39 介紹了基于CPLD的刷卡式電腦聯網集控型自動存包系統的設計,并對系統的軟硬件構成、CPLD內部邏輯設計、工作原理等進行了詳細說明。該系統速度快、安全性好、可靠性高,而且具

2010-07-16 15:11:12 20

20 GPIB 控制器芯片是組建自動測試系統的核心,在測試領域應用廣泛。本文擬討論用ALTERA公司的低成本CPLD 來實現 GPIB 控制器的功能。GPIB 控制器芯片的硬件設計主要分為狀態機的實現

2010-07-28 17:16:12 22

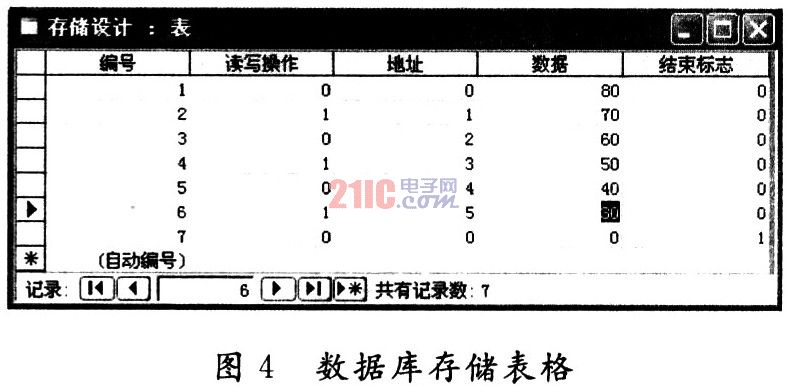

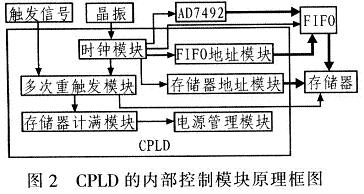

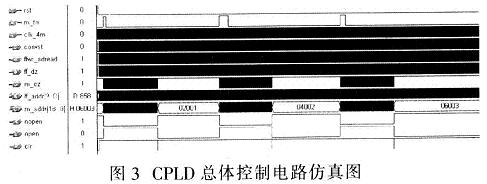

22 提出一種基于CPLD的多次重觸發存儲測試系統設計方案,詳細介紹系統硬件設計以及CPLD內部控制原理,并對CPLD控制電路仿真。該系統體積小、功耗低,能夠實時記錄多次重觸發信號

2010-12-30 16:05:11 22

22 采用圖像傳感器的CPLD視覺系統設計方法

搭建一種低成本的嵌入式視覺系統,系統由CMOS圖像傳感器、CPLD、ARM7微處理器以及SRAM構成。其中,CPLD識別

2009-03-29 15:07:51 400

400

基于CPLD和嵌入式系統的高速數據采集系統的設計與實現

介紹一種基于CPLD和嵌入式系統的高速數據采集系統,并詳細闡述了系統的結構和軟硬件的實

2009-10-15 23:46:59 616

616

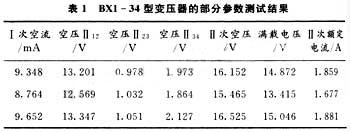

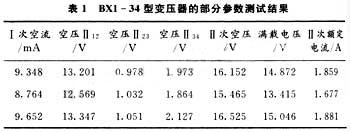

基于MCU CPLD變壓器測試系統的設計與實現

1 引言

???? BX型信號變壓器,BG型軌道變壓器和ZG型硅整流器作為鐵路信號電器設備的前端,其工作的穩定性

2010-01-07 10:50:50 1199

1199

采用CPLD的多次重觸發存儲測試系統解決方案

概述:提出一種基于CPLD的多次重觸發存儲測試系統設計方案,詳細介紹系統硬件設計以及CPLD內部控制

2010-03-17 11:37:51 531

531

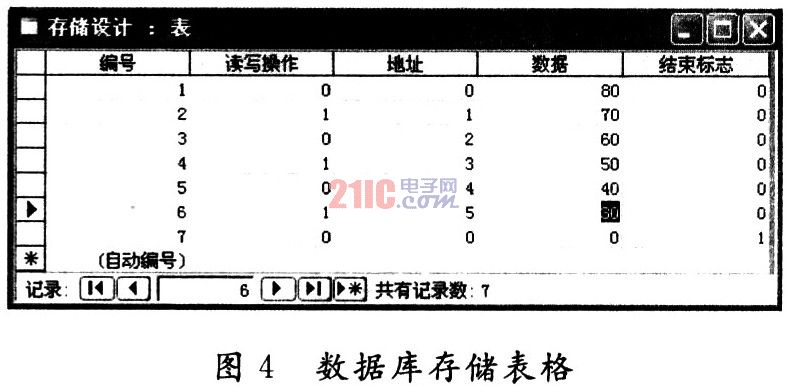

采用LabVIEW的存儲器檢測系統設計方案

概述:文中分析了存儲器的故障類型,研究March算法并進行了擴展。系統以LabVIEW作為軟件工具,實現了對存儲器的自動測試,用數

2010-03-22 14:47:05 1279

1279

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1309

1309

摘要:通信電源技術的發展,對其生產測試設備提出了更高的要求。本文在實踐的基礎上,利用CPLD設計工業電源系統插框生產測試系統,簡化了電路設計,縮短了開發周期,提高了系統的可靠性。利用該系統可以實現被測系統的故障定位。 關鍵詞:通信電源;生產測試

2011-02-24 12:32:12 31

31 在xo640上實現一個簡單的Uart,能夠解析串口數據,并在寄存器中存儲,用FIFO實現數據的傳遞。那么后期可以通過開發板上的串口經CPLD訪問各種數據。比如PC=CPLD=EEPROM等等,極大方便后期

2011-08-05 16:54:46 1741

1741 設計了基于CPLD的低功耗溫度存儲式測試系統;運用鎢錸熱電偶溫度傳感器匹配先進的電源管理模塊,并結合動態存儲測試技術,能夠應用于環境條件比較差的惡劣環境中,在可靠可信、

2012-02-16 16:55:41 27

27 摘要:本系統采用cPLD和AvR單片機作為邏輯控制核心,設計了姿態存儲測試系統,以實現姿態信息的采集、編幀和存儲。詳細介紹了姿態測試系統的工作原理和硬件設計。利用AVR單片機,

2013-03-06 16:00:38 22

22 1、掌握觸發器功能的測試方法。

2、掌握基本RS觸發器的組成及工作原理。

3、掌握集成JK觸發器和D觸發器的邏輯功能及觸發方式。

4、掌握幾種主要觸發器之間相互轉換的方法。

5、通過實驗、體會CPLD芯片的高集成度和多I\O口。

2022-07-10 14:39:58 18

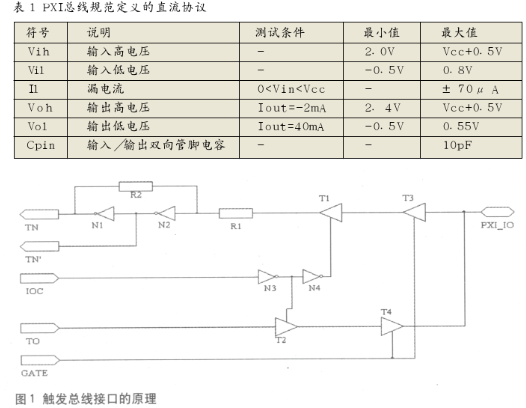

18 CPLD內部施密特觸發器電器特性見表1。目前大部分使用的CPLD都需要兩個電源VCC和VCCIO,VCC就是CPLD內部的核電壓,VCCIO是CPLD所有I/O 引腳電壓。

2018-05-11 08:22:00 1256

1256

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2018-04-26 11:53:00 1121

1121

實驗內容 將基本RS觸發器,同步RS觸發器,集成J-K觸發器,D觸發器同時集成一個CPLD芯片中模擬其功能,并研究其相互轉換的方法。 實驗的具體實現要連線測試。 原理圖 如圖6-1

2017-12-05 09:33:41 13

13 態記錄無意義。為此開發多次重觸發技術,以齒應力作為內觸發信號,只記錄每次觸發后的有用信號,并具有負延遲,而不記錄空閑狀態.直到占滿記錄裝置存儲空間,這樣可有效利用存儲空間,記錄更多的有用信號。

2019-01-15 09:20:00 2021

2021

介紹了一種用CPLD(復雜可編程邏輯器件)作為核心控制電路的測試系統接口,通過時cPLD和竹L電路的比較及cPLD在系統中實現的強大功能,論述了CPLD在測試系統接口中應用的可行性和優越性,簡單介紹

2019-01-01 16:18:00 1472

1472

多次脈沖電纜故障測試儀采用目前國際上先進的“多次脈沖法”測試技術,自主知識產權的測試技術和具有中國特色的多次脈沖發生器,使其具有好的電纜故障波形判斷能力和簡單方便的操作系統。多次脈沖電纜故障測試儀具有獨立的知識產權,國內率先研制成功、國內獨一的“多次脈沖法”電纜故障測試儀。

2020-03-05 15:23:53 826

826 也增加了電路板面積。采用Complex Programmable Logic Device(CPLD)實現突出的優點就在于其靈活的可編程性,這使得硬件電路的升級只需改進軟件就可實現,大大提高了硬件平臺

2020-03-20 09:54:04 1268

1268

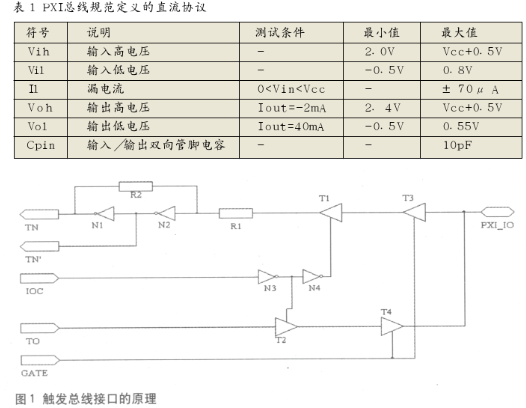

pxi是pci extensiON for inSTrumentation的縮寫,是為了將pci總線擴展到測試儀器領域而推出的以pci計算機局部總線為基礎的模塊儀器結構。pxi相對于cpci系統的一個重要特點是定義了8根觸發總線,這可以實現系統中各模塊間的同步和通信。

2020-04-04 10:36:00 1557

1557

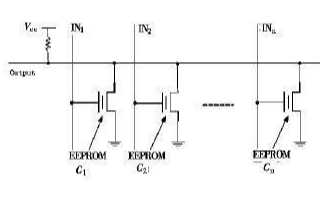

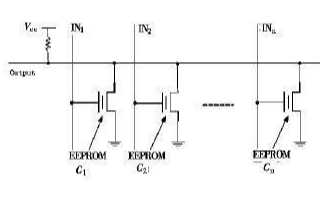

顯然,設計基于SRAM編程技術的CPLD可以很好解決上述應用問題。CPLD的設計和實現的關鍵問題是核心可編程電路結構的實現。因此,本文主要探討針對CPLD的核心可編程結構,如何設計具有相似功能且基于SRAM編程技術的電路結構,從而更好滿足動態重構系統中實現復雜狀態機和譯碼電路的應用。

2020-04-25 10:21:00 1686

1686

電子發燒友網站提供《基于CPLD的相序自適應晶閘管數字觸發器設計.pdf》資料免費下載

2023-10-18 10:08:32 0

0 電子發燒友網站提供《帶CPLD新型通用數字觸發器的設計.pdf》資料免費下載

2023-11-17 16:24:36 0

0 電子發燒友網站提供《帶CPLD新型通用數字觸發器設計.pdf》資料免費下載

2023-11-18 10:59:08 0

0

?

?

電子發燒友App

電子發燒友App

評論