電路功能與優勢

在電力線路測量和保護系統中,需要對多相輸配電網絡的大量電流和電壓通道進行同步采樣。這些應用中,通道數量從6個到64個以上不等。AD76068通道數據采集系統(DAS)集成16位雙極性同步采樣SAR ADC和片內過壓保護功能,可大大簡化信號調理電路,并減少器件數量、電路板面積和測量保護板的成本。高集成度使得每個AD7606只需9個低值陶瓷去耦電容就能工作。

在測量和保護系統中,為了保持多相電力線網絡的電流和電壓通道之間的相位信息,必須具備同步采樣能力。AD7606具有寬動態范圍,是捕獲欠壓/欠流和過壓/過流狀況的理想器件。輸入電壓范圍可以通過引腳編程設置為±5 V或±10 V。

此電路筆記詳細介紹針對采用多個AD7606器件應用而推薦的印刷電路板(PCB)布局。該布局在通道間匹配和器件間匹配方面進行了優化,有助于簡化高通道數系統的校準程序。當通道間匹配非常重要時,此電路可以使用2.5 V內部基準電壓源AD7606;而對于要求出色絕對精度的高通道數應用,此電路可以使用外部精密基準電壓源ADR421,它具有高精度(B級:最大值±1 mV)、低漂移(B級:最大值3 ppm/°C)、低噪聲(典型值1.75 μV p-p,0.1 Hz至10 Hz)等特性。低噪聲及出色的穩定性和精度特性使得ADR421非常適合高精度轉換應用。這兩個器件相結合,能夠實現業界前所未有的集成度、通道密度和精度。

電路描述

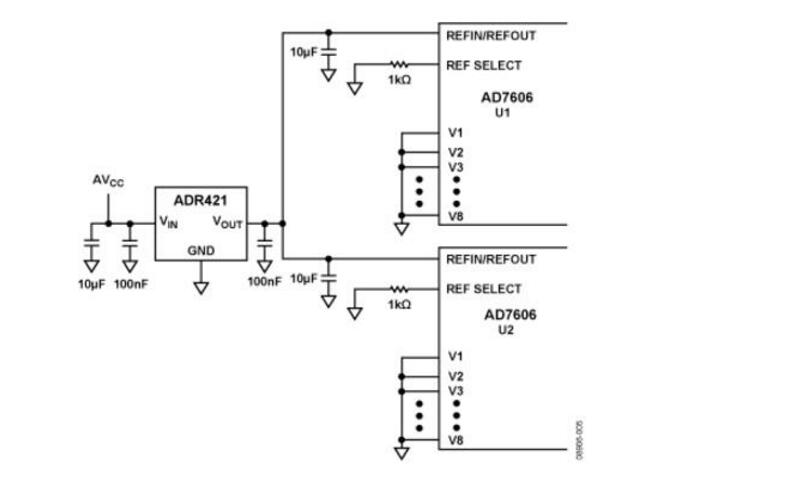

AD7606是一款集成式8通道數據采集系統,片內集成輸入放大器、過壓保護電路、二階模擬抗混疊濾波器、模擬多路復用器、16位200 kSPS SAR ADC和一個數字濾波器。圖1所示電路包括兩個AD7606器件,可以配置為使用2.5 V內部基準電壓源或2.5 V外部基準電壓源ADR421。如果REF SELECT引腳接邏輯高電平,則選擇內部基準電壓源。如果REF SELECT引腳接邏輯低電平,則選擇外部基準電壓源。

電源要求如下:AVCC = 5 V, VDRIVE = 2.3 V至5 V(取決于外部邏輯接口要求)。

本電路筆記描述一個評估板的布局和性能,其中內置兩個AD7606,構成一個16通道數據采集系統。為實現良好的通道間匹配和器件間匹配,模擬輸入通道和器件去耦的對稱布局非常重要。所示數據支持利用圖1所示16通道ADC實現的匹配性能。

圖1. 采用兩個AD7606 8通道DAS的16通道、16位數據采集系統

?

16通道DAS的雙路AD7606板布局

在內置多個AD7606器件的系統中,為確保器件之間的性能匹配良好,這些器件必須采用對稱布局。圖2顯示采用兩個AD7606器件的布局。

圖2. 采用兩個AD7606的16通道DAS的PCB布局

AVCC電壓平面沿兩個器件的右側布設,VDRIVE 電源走線沿兩個AD7606器件的左側布設。基準電壓芯片ADR421位于兩個AD7606器件之間,基準電壓走線向上布設到U2的引腳42,向下布設到U1的引腳42。使用實心接地層。這些對稱布局原則適用于含有兩個以上AD7606器件的系統。AD7606器件可以沿南北方向放置,基準電壓位于器件的中間,基準電壓走線則沿南北方向布設,類似于圖2。

良好的去耦也很重要,以便降低AD7606的電源阻抗,及其電源尖峰幅度。去耦電容應靠近(理想情況是緊靠)這些引腳及其對應接地引腳放置。

REFIN/REFOUT引腳和REFCAPA、REFCAPB引腳的去耦電容是攸關性能的重要電容,應盡可能靠近相應的AD7606引腳。可能的話,應將這些電容放在電路板上與AD7606器件相同的一側。圖3顯示AD7606電路板頂層的建議去耦配置。所示的四個陶瓷電容是REFIN/REFOUT引腳、REGCAP引腳、REFCAPA引腳和REFCAPB引腳的去耦電容。這些電容沿南北方向放置,以便盡可能靠近相應的引腳。

圖3. 頂層去耦,顯示了兩個REFCAPA引腳、REFIN/REFOUT引腳和REFCAPA/B引腳的去耦電容

圖4顯示底層去耦配置,它用于四個AVCC引腳和VDRIVE引腳的去耦。使用多個過孔將引腳與其相應的去耦電容相連。AD7606器件周圍去耦電容的對稱布局有利于器件間的性能匹配。多個過孔用來將電容焊盤和引腳焊盤接地及接到電壓平面和基準電壓走線。

圖4. 底層去耦,顯示了四個AVCC引腳和VDRIVE引腳的去耦電容

16通道系統的通道間匹配

在高通道數系統中,良好的通道間和器件間性能匹配可以大大簡化校準程序。AD7606器件、模擬輸入通道和去耦電容的對稱布局有助于多個器件之間的性能匹配。使用公共系統基準電壓將能進一步增強系統的匹配性能。圖5顯示所有輸入接地時,用于測量板上16個通道之間性能匹配的電路配置。還有最多7個碼的分布直方圖,各通道直方圖的中心為碼0,如圖6所示。

圖5. 用于測試16通道系統通道間匹配的電路示意圖,該系統采用兩個AD7606和外部基準電壓源ADR421,所有輸入接地

圖6. 圖5所示電路的直方圖,顯示了使用外部基準電壓源ADR421的16通道系統的通道間匹配性能

AD7606內部基準電壓源用作系統基準電壓源

AD7606內置一個2.5 V基準電壓源,經過內部放大,它可以為AD7606 ADC提供約4.5 V的緩沖基準電壓。在通道間和器件間匹配性能至關重要的高通道數應用中,可以用一個AD7606的內部基準電壓源為另一個AD7606器件提供基準電壓。在此配置中,U1配置為在內部基準電壓下工作,如圖7所示。

圖7. 用于測試一個AD7606通道間匹配的電路示意圖,使用U1內部基準電壓源

AD7606 U2器件可配置為在外部基準電壓源模式下工作。U1 REFIN/RFOUT引腳提供的2.5 V基準電壓路由至U2的REFIN/REFOUT引腳。一個10 μF去耦電容位于AD7606器件的REFIN/REFOUT引腳。在AD7606 U1和U2上,REFCAPA和REFCAPB引腳短接在一起,并通過一個10 μF陶瓷電容去耦至GND。

兩個AD7606器件均以200 kSPS的采樣速率工作,一個7.5 V直流信號施加于U1的V1和V2,如圖7所示。碼的直方圖如圖8所示。在同一器件的通道之間,平均輸出碼相差1.2個碼。板上的所有16個通道以200 kSPS速率進行轉換。

圖8. 圖7所示電路的直方圖

7.5 V信號施加于U1的V1和U2的V1,板上的所有16個通道以200 kSPS速率工作,如圖9的配置電路示意圖所示。碼的直方圖如圖10所示。在不同器件的V1通道之間,平均輸出碼相差1.4個碼。

?

?

圖9. 用于測試兩個AD7606之間器件間匹配的電路示意圖,U1內部基準電壓源用作系統基準電壓源

圖10. 圖9所示電路的直方圖

將一個AD7606的內部基準電壓源用作系統基準電壓源時,以上直方圖顯示,一個AD7606器件的通道之間以及多個器件的通道之間都具有非常好的匹配性能。

絕對精度

除了通道間匹配和器件間匹配外,如果ADC轉換結果的絕對精度也非常重要,則應使用外部小容差、低漂移基準電壓源作為系統基準電壓源。在該電路中,ADR421 2.5 V基準電壓源用作系統基準電壓源。

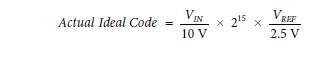

施加于AD7606器件的基準電壓會影響ADC輸出碼:

實際理想碼的值會因溫度而不同,具體取決于系統基準電壓源的溫度系數特性。在絕對精度非常重要的應用中,或者在希望避免通過復雜的溫度校準程序實現絕對精度和通道匹配的應用中,應當使用ADR421等小容差、低漂移2.5 V基準電壓源作為AD7606器件的系統基準電壓源。

7.5 V直流電壓施加于U1的輸入(V1和V2),如圖11的電路所示,并使用外部基準電壓源。U1的兩個通道的碼直方圖如圖12所示。兩個通道的碼直方圖平均值相差0.9 LSB。

圖11. 用于測試一個AD7607通道間匹配的電路示意圖,使用外部基準電壓源

圖12. 圖11所示電路的直方圖

在用于測試器件間匹配的圖13所示電路中,7.5 V直流信號施加于U1和U2 AD7606器件的V1通道,并使用外部基準電壓源。兩個AD7606器件的兩個V1通道的碼直方圖如圖14所示。板上的所有16個通道以200 kSPS吞吐速率工作。U1和U2的V1通道之間的碼直方圖平均值相差0.6 LSB。

圖13. 用于測試兩個AD7606器件間匹配的電路示意圖,使用外部基準電壓源

圖14. 圖13所示電路的直方圖

以上直方圖顯示,采用ADR421外部系統基準電壓源時,一個AD7606器件的直方圖平均值間匹配和多個AD7606器件的直方圖平均值間匹配均小于1 LSB。

結論

本布局能夠確保通過一個AD7606實現通道間良好匹配性能,并且同一PC板上的多個AD7606之間也具有良好的器件間匹配性能。AD7606器件的對稱布局,特別是去耦電容將有助于實現良好的通道間匹配和器件間匹配。在高通道數系統中,良好的通道間和器件間性能匹配意味著校準程序得以簡化。

電子發燒友App

電子發燒友App

評論