闡述了采用EP9312來構造銀行稅務類嵌入式系統的理由,將EP9312與其它嵌入式處理器進行了比較。根據EP9312的特點和系統需求,提出了一種基于EP9312的嵌入式系統硬件設計方案。介紹了系統的技術指標及其所使用的Super I/O、PHY、接口電平轉換器、Flash、SDRAM、Boot-loader等各組成部分。該系統主要應用于高端打印機、計算機終端和高端收款機等產品。

1 嵌入式系統的概念與特點

嵌入式系統結合微處理器或微控制器的系統電路與其專屬軟件,其特性可歸納為下列四項:

(1)通常執行特定功能;

(2)以微電腦與外圍構成核心;

(3)嚴格的時序與穩定性要求;

(4)全自動操作循環。

嵌入式系統具有目的性或針對性,其開發是圍繞著產品和產品的特定功能來進行的。它必須最大限度地在硬件和軟件上“量身定做”以提高效率。本文設計的嵌入式系統主要用于金融和稅務類產品。

2 總體設計

2.1 CPU的選擇

本文采用的是Cirrus Logic公司的嵌入式處理器EP9312。

EP9312是一款ARM9系列的處理器,ARM9系列是高性能和低功耗特性方面最佳的硬宏單元。它具有五級流水線,并提供1.1 MI/s/MHz的哈佛結構。而其前代產品ARM7系列處理器則具有嵌入式ICE-RT邏輯,功耗非常低,并提供0.9MI/s/MHz的三級流水線和馮·諾依曼結構。因為本系統主要用于開發先進的計算機終端、機頂盒、高端打印機等產品,所以需要較快的運算速度,而ARM7主要用于對價位和功耗敏感的消費類產品,并且其運算速度相對較慢,所以本設計系統選擇ARM9系列。在ARM9系列CPU中還有EP9307和EP9315。EP9307與EP9312的功能構造基本相同,只少了1個IDE接口,但多了圖形加速的功能。由于金融稅務類產品大多需要較多的GPIO,而與EP9307相比,EP9312可以很容易地設計出較多的GPIO。EP9315在EP9312擁有的功能上再增加了PCMCIA接口和圖形加速功能,但這并不是金融稅務類產品所必需的功能。綜合考慮之后,本系統選擇了EP9312。

2.2 技術指標

經過系統調研并基于產品成本考慮,嵌入式系統的技術指標如下所述:

●Cirrus Logic公司的EP9312作為主處理器;

●32MB Flash使用NOR Flash;

●64 MB SDRAM;

●顯示格式:西文:24x12點陣,中文:24x24點陣,26行,80列。或者西文:16x8點陣,中文:16x16點陣,26行,80列;

●800x600x16bpp、1024x768x16bpp多種TFT顯示模式,支持單掃描或雙掃描;

●1個并口;

●5個串口;

●2個PS/2端口;

●1個1/10/100 Mb/s的以太網接口。支持TCP/IP協議;

●1個USB Host和1個USB Slave接口。

2.3 系統組成

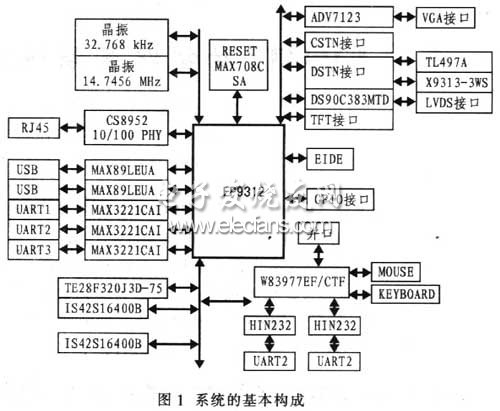

EP9312已經集成了嵌入式系統所需的許多功能,為了使本設計滿足金融稅務類產品的要求,還增加了如下硬件:SuperI/0器件(包含2個UART、1個并口、2個PS/2接口控制器)、網絡PHY接口器件、接口電平轉換器、Flash、SDRAM等。PCB板采用4層板,表層為信號層,其中的電源線路層和地線層深埋在主板的內層,不易受到電源雜波的干擾,尤其是高頻電路,可以獲得較好的抗干擾能力。系統的基本結構如圖l所示。

?

3 模塊功能描述

3.1 CPU

EP9312的內核是ARM920T,其主頻為200MHz,100 MHz內部總線。有16 KB的指令Cache和16 KB的數據Cache,內部集成了很多功能模塊,其中主要包括:LCD控制器、3個USB Host控制器、3個串口控制器、Ethernet MAC、EIDE、AC’97接口等。EP9312內含MMU,支持TCP/IP協議,也為開發各種字符圖形功能提供了快捷的方法。本設計充分利用了這些內部集成的功能,減少了外圍元件。

3.2 RESET模塊

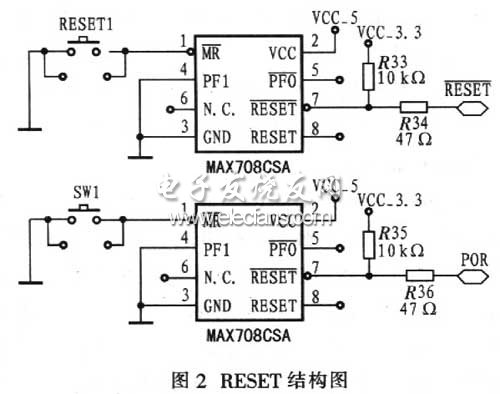

系統的RESET模塊為系統提供啟動及復位信號,是系統運行的開端。

本系統采用MAX708CSA作為復位器件,設計成用戶重啟的按鈕控制。發出RESET信號送給CPU的RSTOn引腳、Flash模塊、JATG模塊等。另采用一片MAX708CSA作為系統上電的按鈕控制。發出POR信號送給CPU的PRSTn引腳,如圖2所示。

?

3.3 系統時鐘模塊

系統時鐘模塊的作用是產生20個獨立的時鐘頻率來滿足EP9312不同獨立邏輯部分的要求,所有這些時鐘頻率都來源于外部的一個低頻晶體振蕩器。這樣處理器速率、總線速率、視頻速率就可以不同而且互不影響。 EP9312提供兩個接口接外部晶體振蕩器,其頻率分別為32 kHz(實時時鐘)和14.7456 MHz。

為了獲得足夠高的時鐘頻率,EP9312同時提供兩個PLL,將32 kHz和14.7456MHz頻率提升到足夠高(14.7456 MHz,最大頻率可為400 MHz)。

3.4 調試端口(JATG)模塊

EP9312提供了JTAG調試接口,它有6條測試掃描鏈。這個接口通過5個外部控制信號實現調試功能:

TDO--測試數據輸出;TDI--測試數據輸入;

TMS--測試模式選擇;TCK--測試時鐘;nTRST--測試復位。

由于EP9312集成了這些JTAG信號,因此引出這些信號線在板上擴展出JTAG口,即可與JTAG調試器進行通信。

3.5 存儲器

EP9312內含SDRAM控制器,它提供一個高速存儲接口給多種存儲裝置,包括SDRAM,Synchronous Flash和Synchronous ROM等。

CPU中已有SDRAM控制器,因此系統不需外加SDRAM控制器,只要采用合適的SDRAM存儲器,與EP9312的專用SDRAM信號線相連接即可。

本系統采用2片IS4216400B的16位數據總線SDRAM器件組合構成了一個32位數據總線的16 MB存儲系統。今后如有需要,只需用16 MB器件代替8 MB的器件,即可方便地擴容至32 MBSDRAM的系統。

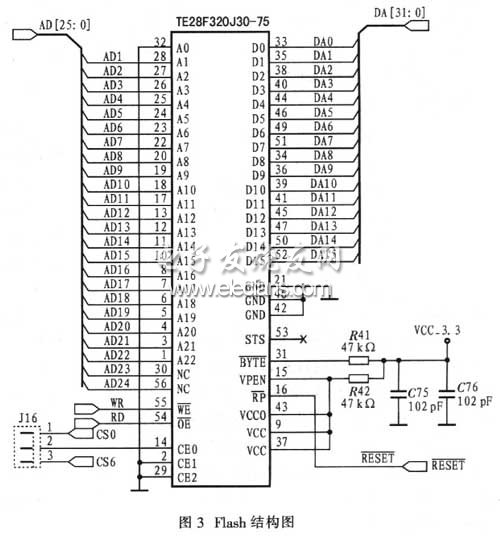

本系統所用的Flash器件是Intel公司的TE28F320J3D-75。該器件采用56引腳TSOP封裝,32 MB的存儲空間由32個128KB的擦除塊組成。該Flash采用25根地址線和16位數據線,可以通過BYTE信號來選擇是8位還是16位方式訪問。本系統采用16位方式訪問,因此該信號線接高電平,同時,AO地址線接地。OE/WE是讀寫信號,由EP9312的讀寫控制線直接控制。系統中將Flash的片選信號CE2、CEl信號接地,CEO由EP9312的兩根片選信號CSO和CS6通過跳線來控制,如圖3所示。

?

本系統的Flash需要設計成2 MB、4 MB、8 MB均支持的電路,只需要焊接不同容量的器件即可。這樣做可以滿足不同用戶的需求,如:使用CF卡的用戶只要2 MB Flash即可。此時,需要對Flash和SDRAM的型號進行細致的選擇,并對地址總線和數據總線進行相應的設計。

3.6 PS/2、串口和并口

通過Super-I/O進行擴展,如圖1所示。Super-I/O選擇Winbond公司的W83977ATF。該器件提供兩個串口、一個并口、PS/2鍵盤鼠標接口和23個GPIO,通過EP9312的WAITn延時等待信號來匹配ISA總線與存儲總線的速度問題。連同CPU提供的3個串口控制器,系統總共具有5個串口。

3.7 網絡

EP9312內部含有一個Ethernet的MAC,只需要一個PHY并通過VT6103L即可實現。

3.8 顯示電路

要根據不同的顯示屏來決定顯示電路設計,本系統設計成共支持五種屏幕,包括TFT、CSTN、DSTN、LVDS、VGA。EP9312輸出的是數字信號,分別為18位數據、場頻、行頻、時鐘、亮度控制幾類信號。對于TFT、CSTN,可以直接與EP9312的內置接口相連,但要注意CSTN在初始化彩色查找表時,將R,B色碼互換。接TFT屏要加電平轉換器。對于DSTN來說,本系統選用的屏幕為夏普公司的LMl21VBlT02,該屏為單色屏,上下每時鐘周期4個像素,每個信號對應一個像素點。查閱EP9312的輸出像素轉換表后發現,雙掃描每時鐘周期4個像素的模式并不適用于該屏,所以本系統在設計中選用了雙掃描每時鐘周期8個像素的模式,并從中挑選出合適的信號來驅動該屏,同時也要加電平轉換器。在目前的市場上.TFT接口的屏并不是主流,相對來說LVDS接口的屏使用更廣,對LNDS接口的設計,本系統采用DS90C383MTD轉換器來構建。對于彩色CRT要加三個D/A轉換器和電平轉換器,單色CRT只要一個D/A轉換器和電平轉換器,接VGA屏要加專用器件,如ADV7123。顯示電路模塊圖如圖4所示。

?

3.9 電源

EP9312需要4個不同的電源:RVDD(3.3 V)、CVDD(1.8 V)、VDD_PLL(1.8 V)和VDD_ADC(3.3V)。板上其他元件除了3.3 V供電的以外,還有5V供電的,整個系統的輸入電壓為12 V,通過變壓器件變成5 V,再通過LTl76ET-3.3轉換器件把 5 V轉變為3.3 V的系統電壓,通過LT176ET-1.8轉換器件把 3.3V轉變為1.8V的EP9312內核電壓。

3.10 GPIO分配

EP9312有16個具有中斷能力的增強型通用I/0,由于金融稅務類嵌入式系統的產品通常不需要IDE接口,因此把IDE接口的I/O設計成GPIO,連同其他一些設計,總共增加了49個可選通用I/O。

3.11 Bootloader

Bootloader是系統加電啟動運行的第一段軟件代碼。整個系統的加載啟動任務就完全由Bootloader來完成。簡單地說,Bootloader就是在操作系統內核或用戶應用程序運行之前運行的一段小程序。通過這段小程序,可以初始化硬件設備、建立內存空間的映射圖,從而將系統的軟硬件環境帶到一個合適的狀態,以便為最終調用操作系統內核或用戶應用程序準備好正確的環境。EP9312提供了20種Boot-loader的方式,分別經過EECLK、EEDAT、LBOOTI、LBOOTO、ASDO、CSn[7:6]的跳線組合來選擇。

本系統在調試和生產時,采用16-bit serial boot的啟動方式。對應的EECLK、EEDAT、LBOOTI、LBOOTO、ASDO、CSn[7:6]選擇方式分別為:l、1、0、X、0、1。此時,CPU通過片內已經固化的4 KB程序進行啟動,初始化CPU和串口,并通過串口把用戶程序下載到Flash中。當系統正常工作時,則直接通過Flash啟動。直接在Flash中讀取程序代碼運行。

本設計利用前者把操作系統和應用程序寫入Flash中,用后者進行嵌入式系統的正常工作開啟。

4 結束語

本文介紹了一種基于EP9312的銀稅類嵌入式系統的硬件設計方案。經過測試,系統各部分都能正常工作,實現了預定的功能。

電子發燒友App

電子發燒友App

評論