?

集成在virtex-iipro器件中的powerpc405,是一個32位risc硬核,它支持coreconnect總線的標準外設(shè)集合。使用coreconnect總線,可以方便地控制多個外設(shè)。在edk集成開發(fā)環(huán)境下,對于多個外設(shè),每個外設(shè)都有對應(yīng)的任務(wù)。powerpc405默認的嵌入式內(nèi)核是standalone,在其上開發(fā)的多個任務(wù)是宏觀串行執(zhí)行的,只有利用參數(shù)傳遞或全局參變量來建立各任務(wù)間的關(guān)系。在很多情況下,系統(tǒng)需要多個任務(wù)系統(tǒng)宏觀并行執(zhí)行,使用standalone顯然是不合適的。而通過把嵌入的standalone內(nèi)核改變?yōu)閑dk自帶的xilkernel內(nèi)核,適當(dāng)?shù)馗淖冘浖脚_設(shè)置的內(nèi)容,就可以實現(xiàn)多個任務(wù)的并行執(zhí)行。xilkernel也支持多任務(wù)間通訊和中斷。根據(jù)各種通訊方式,也可以建立各個任務(wù)之間的聯(lián)系;通過中斷,處理器可以及時響應(yīng)外設(shè)產(chǎn)生的事件。

硬件系統(tǒng)結(jié)構(gòu)

如圖1所示,powerpc405使用fpga外部的存儲單元,使用coreconnect總線和外圍接口。coreconnect總線的標準外設(shè)集合可以重復(fù)使用,使系統(tǒng)整合變的更加容易。

?

圖1powerpc405硬件系統(tǒng)結(jié)構(gòu)

coreconnect總線結(jié)構(gòu)

plb總線接口:用于powerpc405內(nèi)核與高性能設(shè)備的連接。plb接口包括isplb接口和dsplb接口兩種。其中,isplb接口用于外設(shè)與powerpc405指令緩沖的連接,dsplb接口用于外設(shè)與powerpc405數(shù)據(jù)緩沖的連接。

opb總線接口:片上外設(shè)總線,內(nèi)核通過opb來訪問低速和低性能的系統(tǒng)資源。它不是直接連接到處理器內(nèi)核。處理器內(nèi)核借助于“plbtoopb”橋,通過opb訪問從外設(shè);opb總線控制器的外設(shè)可以借助“opbtoplb”橋,通過plb訪問存儲器。

硬件平臺構(gòu)件

在edk集成開發(fā)環(huán)境中,由用戶向?qū)蒻hs文件,用戶也可以根據(jù)mhs文件的語法添加自定義的外設(shè)。mhs文件用于描述硬件體系結(jié)構(gòu),其主要包括平臺的處理器類型、總線結(jié)構(gòu)、外圍接口、中斷處理和地址空間。

edk工具platgen使用mhs文件作為輸入來創(chuàng)建硬件平臺,它創(chuàng)建不同形式的網(wǎng)表文件(ngc,edif),下游工具的支持文件和頂級hdl包裝以允許用戶添加其他的組件到硬件平臺。

軟件系統(tǒng)結(jié)構(gòu)

在edk集成開發(fā)環(huán)境中,mss文件用于描述軟件體系結(jié)構(gòu),其主要定義了平臺的內(nèi)核、軟件庫、驅(qū)動程序和文件系統(tǒng)的參數(shù)。

edk工具libgen使用mss文件作為輸入,定制驅(qū)動、庫、文件系統(tǒng)和中斷處理程序。

xilkernel模塊結(jié)構(gòu)

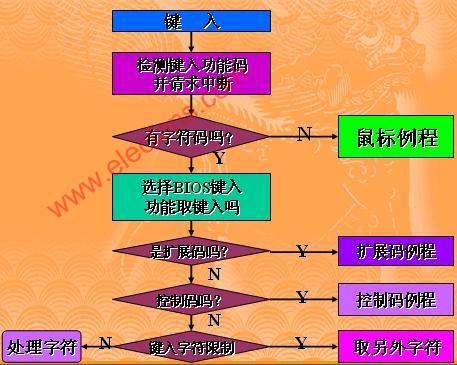

xilkernel模塊結(jié)構(gòu)如圖2所示,xilkernel提供與內(nèi)核的posix接口。但并不是每一個通過posix定義的概念和接口都是可用的。取而代之的是一個精細選擇的子集,幾乎覆蓋了所有有用的接口和概念。其支持posix線程、posix無名信號量、xsi消息隊列、posix互斥鎖、中斷處理等。

xilkernel的軟件平臺配置

xilkernel已經(jīng)被設(shè)計為可以和edk軟件和硬件流緊密共同工作,完全被整合在軟件平臺配置和自動的庫、板級支持包產(chǎn)生機制之中。在軟件配置平臺,可以對xilkernel支持的功能進行配置,下面介紹一些主要的配置:

a、指定系統(tǒng)定時器的頻率值和時間片間隔。

b、指定系統(tǒng)可以運行的線程數(shù)量、任務(wù)調(diào)度方式(這里我們設(shè)置為優(yōu)先級搶占方式,以保證重要的突發(fā)事件及時得到處理)和系統(tǒng)中斷控制器。

c、配置系統(tǒng)的通訊方式,可以通過這些開關(guān)來確定系統(tǒng)需要的通訊方式,并可以確定各個通訊方式的參數(shù)。包括消息隊列、信號量等。

d、指定系統(tǒng)的靜態(tài)任務(wù),也就是完全進入內(nèi)核后執(zhí)行的第一個任務(wù),可以在這個任務(wù)里產(chǎn)生和設(shè)置系統(tǒng)需要的其它任務(wù)。

e、一些增強系統(tǒng)功能的設(shè)置等等。

主要任務(wù)間的通訊方式和中斷

必需的配置

首先要生成連接腳本,是通過硬件需要生成的,此腳本反映了xilkernel需要的不同的段存儲器。比如.vectors段被分配于一個有64kb地址邊界的存儲器的開始,而.boot段在0xfffffffc處。其余的代碼和數(shù)據(jù)存儲器可以放在任何地方。

?

圖2xilkernel模塊結(jié)構(gòu)

其次,xilkernel是作為一個庫來架構(gòu)的。這意味著應(yīng)用程序源文件僅需要連接xilkernel,就能夠訪問xilkernel的功能。這些需要設(shè)置編譯器的庫連接選項為xilkernel,并在用戶代碼中包含“xmk.h”文件。應(yīng)用程序提供main()入口,然后通過調(diào)用xilkernel_main()作為內(nèi)核的入口點。產(chǎn)生庫、bsp并編譯程序后,xilkernel將自動作為系統(tǒng)啟動、初始化硬件核、中斷和軟件處理程序的一部分。下面是一個簡單的內(nèi)核入口代碼:

#include"xmk.h"

/*定義和聲明*/

intmain()

{

/*用戶完成預(yù)處理,不允許調(diào)用內(nèi)核接口*/

xilkernel_main();/*開始內(nèi)核*/

/*程序不會執(zhí)行到這里*/

}

/*系統(tǒng)的靜態(tài)任務(wù)*/

{

/*產(chǎn)生一些線程來處理用戶需要*/

}

線程的創(chuàng)建

線程的創(chuàng)建及屬性的簡單設(shè)置可以由下面幾個函數(shù)實現(xiàn):

intpthread_attr_init(pthread_attr_t*attr)

intpthread_attr_setschedparam(pthread_attr_t*attr,structsched_param*schedpar)

intpthread_create(pthread_tthread,pthread_attr_t*attr,void*(*start_func)(void*),void*param)

pthread_attr_init()初始化線程的屬性。thread_attr_setschedparam()來設(shè)置線程的優(yōu)先級,attr是線程的屬性,schedpar是包含有線程優(yōu)先級的數(shù)據(jù)結(jié)構(gòu)。pthread_create()創(chuàng)建一個線程,thread表明線程id,attr指出線程屬性,start_func函數(shù)指針是線程創(chuàng)建成功后開始執(zhí)行的函數(shù),param是這個函數(shù)的一個唯一的參數(shù)。

在靜態(tài)任務(wù)中調(diào)用這些函數(shù)來產(chǎn)生一些有優(yōu)先級的任務(wù)。如下例:

staticpthread_attr_tattr;

staticstructsched_paramprio;

void*first_thread(){......

pthread_attr_init(&attr);

prio.sched_priority=4;

pthread_attr_setschedparam(&attr,&prio);

ret=pthread_create(&tid0,&attr,(void*)important_task,null);

pthread_attr_init(&attr);

prio.sched_priority=5;

pthread_attr_setschedparam(&attr,&prio);

ret=pthread_create(&tid1,&attr,(void*)second_important_task,null);

......

}

這樣,系統(tǒng)會發(fā)起important_task和second_important_task兩個任務(wù),important_task的優(yōu)先級比second_important_task高,會優(yōu)先運行。除非important_task任務(wù)阻塞或退出,second_important_task才可能得到運行。

電子發(fā)燒友App

電子發(fā)燒友App

評論