I/O約束(I/O Constraints)包括I/O標準(I/OStandard)約束和I/O位置(I/O location)約束。

2023-11-18 16:42:28 506

506

下載附件,解壓,運行k-mac.exe,選擇某個網卡將它的mac地址設置為28-D2-44-1B-72-1D,重啟機器,然后在QuartusII的tools->license setup將license文件設置為28D2441B721D_20161120.dat

2015-10-29 09:31:32

QuartusII基本使用方法

2012-08-06 13:53:18

QuartusII教程官方中文版. 目錄: 第1章: 設計流程 ......................................... 1 第2章: 設計輸入

2019-05-07 13:05:17

QuartusII新建一個工程進行編譯并燒寫的方法

2012-04-03 08:10:37

近期做了一個數據采集傳輸模塊,用QuartusII編程設計的,采用FT245RL芯片進行USB通信。最近遇到一個問題,程序下載進PCB板以后多次出現無法識別USB口的問題。而且對同一個程序,哪怕修改

2019-06-29 14:46:38

設定就行了。主要是指你的某些管腳在電路當中起到了時鐘管腳的 作用,比如flip-flop的clk管腳,而此管腳沒有時鐘約束,因此QuartusII把“clk”作為未定義的時鐘。 措施:如果clk不是時鐘

2018-07-03 01:34:46

希望從一個輸入引腳到多個寄存器的輸入端(D)的延時盡可能保持一致,可以設置這樣的約束嗎?器件是Cyclone4.

2012-04-11 15:32:53

求助:大哥們有沒有Quartusii的詳細資料啊,就說明怎樣建立project,然后定義管腳仿真之類的東東。感激不盡。

2012-11-05 09:24:10

TCO2-532+

2023-04-06 23:32:40

這里主要是指對生態環境的保護,TCO認證在這方面限制了這些有害因素在顯示器產品中的含有量,以達到保護生態環境的效果。

2020-03-20 09:00:35

EVAL MODULE FOR TSU3721

2023-03-29 22:52:02

TSU8111 SINGLE CELL USB CHARGER

2023-03-23 08:11:32

在quartusII中,應用fft ip核時,variable streaming 模式下的bit-reverse(位翻轉)是什么意思?煩勞詳細幫助新手解釋一下,不甚感激

2017-01-09 10:55:59

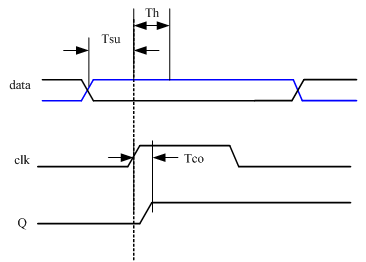

FPGA中幾個基本的重要的時序分析參數介紹(fmax\tsu\th\tco\tpd)今天無聊,翻開書偶看到介紹時序部分的東西,覺得其中幾個參數縮寫所代表的含義應該記住,故寫如下文章……FPGA中

2012-04-09 09:41:41

的計算模型 由圖(1)可以看出,在影響Fmax 的四個參數中,由于針對某一個器件Tsu 和Tco 是固定的,因此我們在設計中需要考慮的參數只有兩個Tlogic 和Troute.通過良好的設計以及一些如

2018-08-21 09:46:15

時鐘路徑。在本實例中,以上的約束將會覆蓋如圖8.27所示的時鐘。(特權同學,版權所有)圖8.27 時鐘約束可覆蓋路徑接著,對lcd_clk這個時鐘進行約束,它需要約束為虛擬(virtul)時鐘,將會被用于

2015-07-30 22:07:42

關系需要滿足,其公式如下:Launch edge + Tc2t + Tco + Tr2p+Tdpcb < latch edge + Tc2r - Tsu對于保持時間,有基本的時序關系需要滿足,其

2015-08-02 19:26:19

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

控。從最近一段時間工作和學習的成果中,我總結了如下幾種進行時序約束的方法。按照從易到難的順序排列如下:0. 核心頻率約束 這是最基本的,所以標號為0。1. 核心頻率約束+時序例外約束 時序例外約束包括

2016-06-02 15:54:04

過于繁多,在qsf文件中保存不下,得到保留的網表可以以Partial Netlist的形式輸出到一個單獨的文件qxp中,配和qsf文件中的粗略配置信息一起完成增量編譯。 4. 核心頻率約束+時序例外約束

2017-12-27 09:15:17

源端口出發到達源寄存器時鐘端口的延遲Tclk2:時鐘從時鐘端口出發到達目的寄存器時鐘端口的延遲Tco:時鐘上升沿到達寄存器到數據從D端輸出到Q端的延遲Tdata:數據從源寄存器Q端到目的寄存器D端的延遲Tclk:時鐘周期Tsu:建立時間,時鐘上升沿到達寄存器前,數據必須提前n納秒穩定下來,這個...

2021-07-26 08:00:03

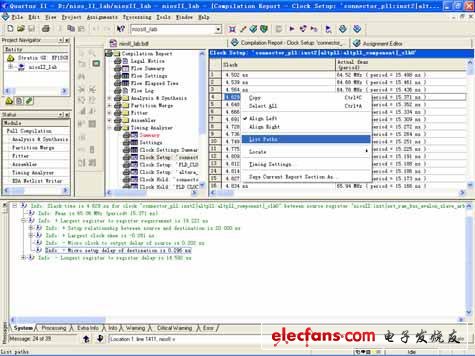

+ 組合邏輯延時Tlogic + FPGA內部的網絡延時Tnet + 寄存器時鐘建立時間Tsu –時鐘偏斜TclkskewFmax = 1 / Tclk在QuartusII時序分析后很容易看到Fmax

2018-07-03 02:11:23

+ 組合邏輯延時Tlogic + FPGA內部的網絡延時Tnet + 寄存器時鐘建立時間Tsu –時鐘偏斜TclkskewFmax = 1 / Tclk在QuartusII時序分析后很容易看到Fmax

2018-07-09 09:16:13

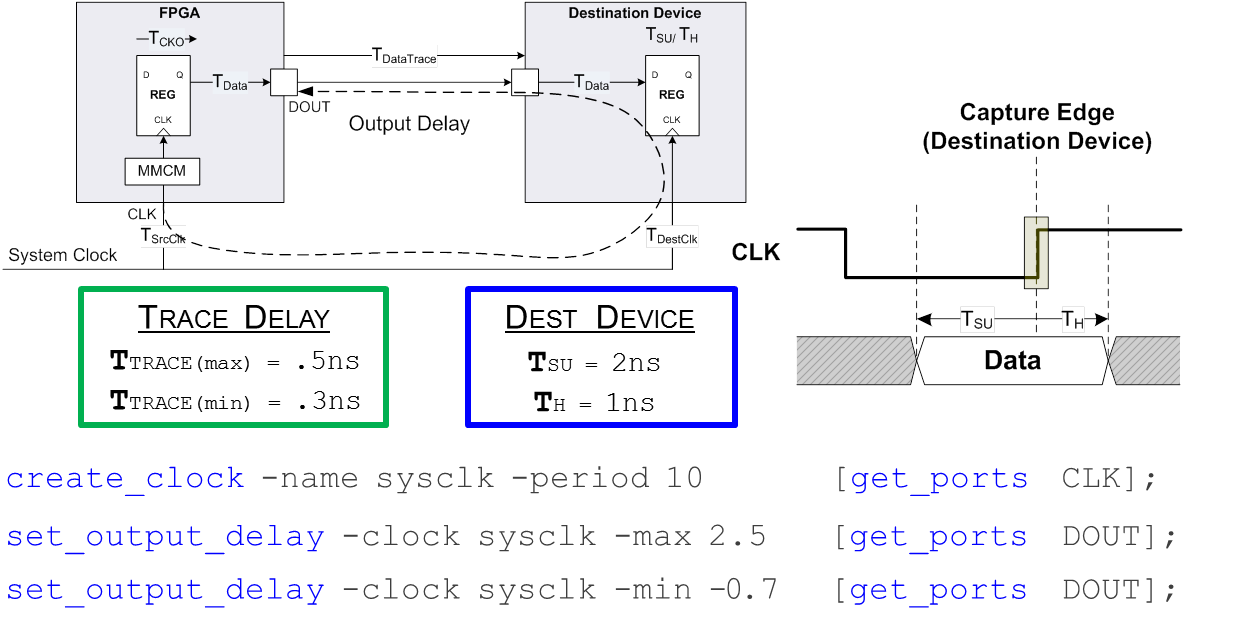

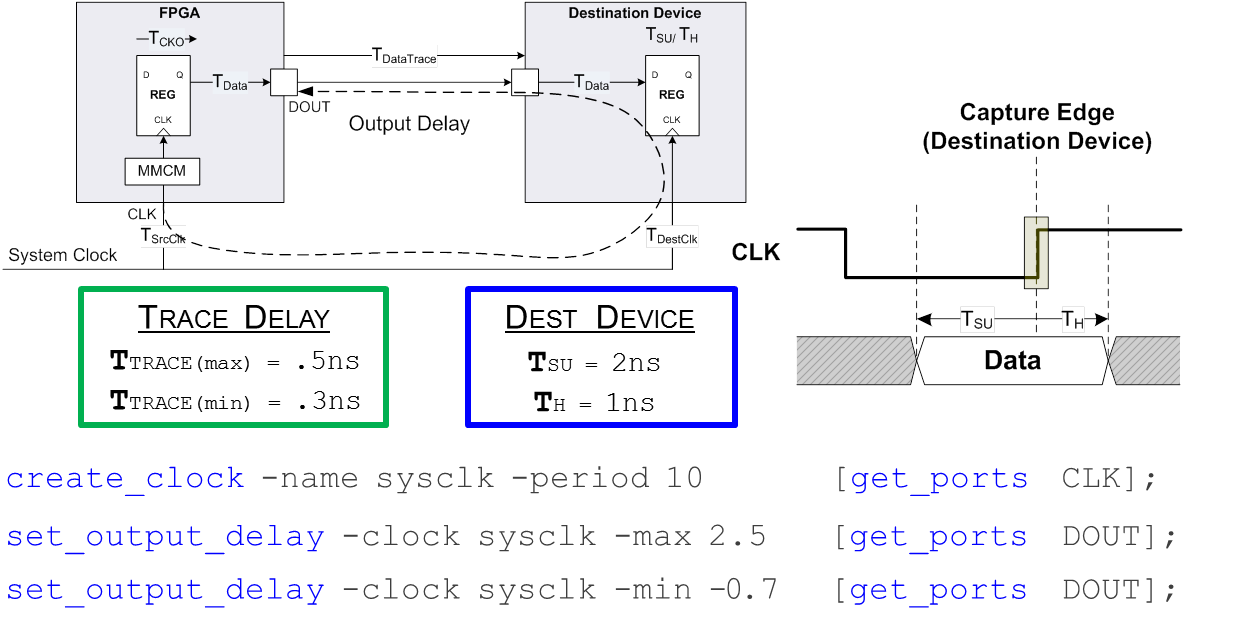

FPGA靜態時序分析——IO口時序(Input Delay /output Delay)1.1概述 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能

2012-04-25 15:42:03

: Tmin = Tco + Tdata + Tsu - Tskew (公式3-8)4. 應用分析4.1設置時鐘主頻約束 所有的靜態時序分析

2012-01-11 11:43:06

affect the logic placement but only can apply to I/O pin–Tsu?? NO! NO! Tsucan affect the logic

2008-09-11 09:20:30

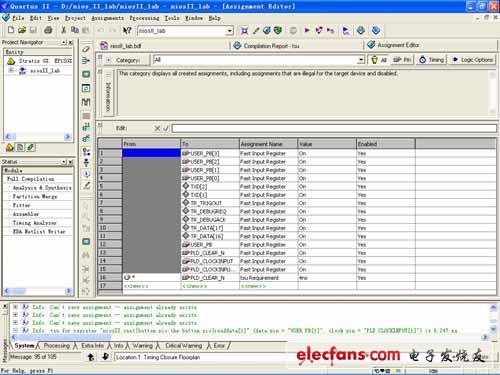

Quartus II中Tsu/Tco的約束方法是什么

2021-04-29 06:36:32

關系需要滿足,其公式如下:Launch edge + Tc2t + Tco + Tr2p+Tdpcb < latch edge + Tc2r - Tsu對于保持時間,有基本的時序關系需要滿足,其

2019-04-10 06:33:34

的設定。這兩個約束比較簡單,容易設定,但是非常關鍵。如果設定的不好,系統性能會大打折扣。false path 是指在時序分析中不考慮其延遲計算的路徑。例如有些跨越時鐘域的電路等。設定的方法

2012-03-05 15:02:22

一個好的習慣就是,寫代碼一定要記得寫注釋。怎么碰到了這么個怪問題:Quartusii 9.0中

2009-11-08 17:06:49

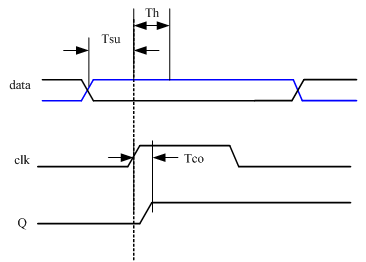

edge、Tsu、Th、Tco:發射沿、鎖存沿、建立、保持、數據輸出延時(Tco):這個時間指的是當時鐘有效沿變化后,數據從輸入端到輸出端的最小時間間隔。 四、時序約束(1)周期約束TIMESPEC

2017-03-09 14:43:24

時間,使(Tclk + clk skew)-(Tco+Tdelay) > Tsu,set min delay 約束Tco和clk skew滿足外設的保持時間,(Tco

2023-05-06 16:24:12

??時序工具??關于時序工具的一些FAE解答:??問:你們的工具是否只提供所有輸入輸出管腳完全一致的時序約束?如tsu,th,tco,tpd的約束?如果不同管腳可以有不 同約束值,如何設置

2021-10-12 09:22:08

此版只討論時序約束約束理論約束方法約束結果時鐘約束(Clock Specification): 約束所有時鐘(包括你的設計中特有的時鐘)對準確的時序分析結果而言是必不可少的。Quartus II

2013-05-16 18:51:50

好的時序是設計出來的,不是約束出來的時序就是一種關系,這種關系的基本概念有哪些?這種關系需要約束嗎?各自的詳細情況有哪些?約束的方法有哪些?這些約束可分為幾大類?這種關系僅僅通過約束來維持嗎?1

2018-08-01 16:45:40

求16.5安裝方法和約束設置

2012-05-24 22:32:46

本文在開環時序仿真的基礎上提出一種基于QuartusII、DSP Builder和Modelsim的閉環時序仿真測試方法,并借助于某一特定智能控制器的設計對該閉環測試方法進行了較為深入的研究。

2021-05-06 09:36:44

# ** Error: E:/QuartusII13/test2/fir2_ast.vhd(32): Library auk_dspip_lib not found.# ** Error: E

2018-04-23 12:33:00

1.quartusii 9.1 生成的testbench 后用VHDL 編寫后續程序的格式, 方法2如何用modelsim 關聯quartusii仿真3是不是testbench 沒有問題了在quartusii 執行 RTL simulation 就可以從modelsim得到 波形

2013-05-17 21:36:56

喜我對我的設計中的關鍵路徑以及如何約束它們有疑問。我正在使用ISE 14.1進行實施。我有一個設計,其中關鍵路徑(從源FD到目的地FD)給出-3.3ns的松弛(周期約束為10ns)。現在有沒有其他方法

2019-04-08 08:58:57

我正在設計一個雙向ddr i / o電路,但遇到時序約束失敗。器件為A7-100-FGG484-2,開發環境為vivado 2016.2。當電路作為輸入(t_rn = 1)運行時,ddr輸入引腳

2020-08-28 06:14:43

我是一個FPGA初學者,關于時序約束一直不是很明白,時序約束有什么用呢?我只會全局時鐘的時序約束,如何進行其他時序約束呢?時序約束分為哪幾類呢?不同時序約束的目的?

2012-07-04 09:45:37

,所以,Tco即我們的約束部分,Tsu即SDRAM的建立時間,又因為,altera官方提供的資料,不用時鐘偏斜這一概念,用的是時鐘網絡延時, 即時鐘網絡延時=- 時鐘偏斜,即Tc2s -Tc2d 所以

2015-03-31 10:20:00

現有的半監督聚類方法較少利用數據集空間結構信息,限制了聚類算法的性能。該文提出一種基于密度的約束擴展方法(DCE),將數據集以圖的形式表達,定義一種基于密度的圖形相似

2009-04-22 09:32:45 25

25 傳統序列模式挖掘算法往往忽略了序列模式本身的時間特性,所考查的序列項都是單一事件,無屬性約束。提出了一種挖掘多屬性約束事件序列關聯規則的方法。此方法基于傳統

2009-06-17 11:08:30 10

10 時序約束與時序分析 ppt教程

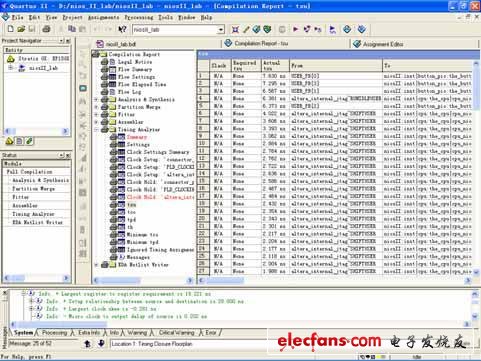

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 The TSU5511 is designed to interface the cell phone UART, USB, and audio chips with external

2010-09-10 00:09:59 24

24 時序約束用戶指南包含以下章節: ?第一章“時序約束用戶指南引言” ?第2章“時序約束的方法” ?第3章“時間約束原則” ?第4章“XST中指定的時序約束” ?第5章“Synplify中指定的時

2010-11-02 10:20:56 0

0 TCO在CRT方面的對比

隨著時間的發展,原有的TCO99標準已經難以適應新的LCD、PDP等采用新式顯示技術的顯示器。于是TCO聯盟開始制定最新的TCO03標準,

2009-12-26 17:06:32 768

768 TCO在LCD方面的對比

隨著時間的發展,原有的TCO99標準已經難以適應新的LCD、PDP等采用新式顯示技術的顯示器。于是TCO聯盟開始制定最新的TCO03標準,

2009-12-26 17:10:05 804

804 TCO的歷史

2009-12-26 17:11:29 703

703 服務器操作系統TCO概覽(1)

1. 服務器操作系統TCO構成 計世資訊(CCW Research)將全部企業不同操作系統、不同服務器應用的

2010-01-29 13:56:13 1267

1267 QuartusII免費下載入口

2012-07-01 17:12:25 547

547 QuartusII軟件安裝入口

2012-10-19 08:19:35 45

45 QuartusII_12.0下載入口

2014-02-24 11:36:44 31

31 QuartusII軟件免費安裝

2017-04-17 17:28:00 13

13 quartusII是一款非常棒的軟件,FPGA現在市面上應用越來越廣,有興趣的可以看看此教程

2015-11-16 11:35:42 9

9 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 QuartusII簡介(中文版),好東西,喜歡的朋友可以下載來學習。

2016-01-18 15:31:05 0

0 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 16:52:22 0

0 QuartusII_使用手冊,又需要的朋友下來看看

2016-05-19 15:16:15 0

0 基于TCO的計數器設計,快來下載學習啊

2016-07-04 14:01:58 5

5 基于TCO的時鐘設計,快來下載學習啊

2016-07-04 14:01:58 9

9 本章主要介紹 QuartusII自帶的信號分析工具 自帶的信號分析工具 —SignalTap II 的使用方法,感興趣的小伙伴們可以看一看。

2016-09-18 14:55:04 10

10 QuartusII使用教程

2017-08-26 17:58:57 5

5 The TSU101, TSU102, and TSU104 operational amplifiers offer an ultra low-power consumption of 580

2017-09-05 09:47:51 8

8 XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應用特性決定了其在接口上有多種構建和實現方式,所以從UCF到XDC的轉換過程中,最具挑戰的可以說便是本文將要

2017-11-17 19:01:00 6665

6665

的雙端和K端網絡可靠性研究基礎上,提出了基于截斷的路徑約束方法;并根據該方法構造二元決策圖BDD模型進行帶約束的是端網絡可靠性分析。該算法針對k端點對點信息流在一定時間延遲下完成傳輸問題,具有較強的實際意義。實例分析結果

2017-12-06 14:03:03 0

0 約束優化進化算法主要研究如何利用進化計算方法求解約束優化問題,是進化計算領城的一個重要研究課題.約束優化問題求解存在約束區域離散、等式約束、非線性約束等挑戰,其問題的本質是,如何處理可行解與不可行

2017-12-28 11:45:49 0

0 電子發燒友網為你提供TI(ti)TSU5511相關產品參數、數據手冊,更有TSU5511的引腳圖、接線圖、封裝手冊、中文資料、英文資料,TSU5511真值表,TSU5511管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-09-12 16:30:28

電子發燒友網為你提供TI(ti)TSU6721相關產品參數、數據手冊,更有TSU6721的引腳圖、接線圖、封裝手冊、中文資料、英文資料,TSU6721真值表,TSU6721管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-09-12 17:18:07

電子發燒友網為你提供TI(ti)TSU6111A相關產品參數、數據手冊,更有TSU6111A的引腳圖、接線圖、封裝手冊、中文資料、英文資料,TSU6111A真值表,TSU6111A管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-09-13 14:26:11

電子發燒友網為你提供TI(ti)TSU8111相關產品參數、數據手冊,更有TSU8111的引腳圖、接線圖、封裝手冊、中文資料、英文資料,TSU8111真值表,TSU8111管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:19:15

本文檔的主要內容詳細介紹的是QuartusII原理圖輸入法基本應用 實驗目的是1. 掌握輸入編輯原理圖文件的方法2. 掌握編譯原理圖文件的方法3. 掌握仿真原理圖文件的方法理解QuartusII器件編輯的方法

2018-10-17 08:00:00 0

0 本文檔的主要內容詳細介紹的是QuartusII原理圖輸入法層次化設計實驗

一、 實驗目的1. 掌握原理圖文件的設計方法2. 掌握調用模塊設計原理圖文件的方法3. 掌握原理圖文件層次化設計的方法

2018-10-17 08:00:00 0

0 了解時序約束向導如何用于“完全”約束您的設計。

該向導遵循UltraFast設計方法,定義您的時鐘,時鐘交互,最后是您的輸入和輸出約束。

2018-11-29 06:47:00 2698

2698

本文檔的主要內容詳細介紹的是QuartusII軟件操作示例資料免費下載。

2019-02-26 14:09:31 8

8 本文檔的主要內容詳細介紹的是QuartusII安裝教程之QuartusII安裝說明和硬件安裝資料免費下載。

2019-03-27 17:12:50 11

11 DDR接口的約束稍許復雜,需要將上升沿和下降沿分別考慮和約束,以下以源同步接口為例,分別就Setup/Hold Based 方法和Skew Based方法舉例。

2019-07-25 11:01:38 2457

2457

本文檔的主要內容詳細介紹的是Verilog HDL語言組合邏輯設計方法以及QuartusII軟件的一些高級技巧。

2019-07-03 17:36:12 19

19 組合邏輯延遲和走線延遲。Tsu表示捕獲寄存器建立時間要求。Th表示捕獲寄存器保持時間要求。其中Tco、Tsu和Th是由FPGA的芯片工藝決定的。所以,我們所謂的時序約束,實際上就是對時鐘延遲和Tdata做一定的要求或者干預,其中Tdata由組合邏輯(代碼)及布局布線決定,這也決

2021-01-12 17:31:36 9

9 1. 片內的Tsu/Tco 是指前級觸發器的Tco 和后級觸發器的Tsu, 一般來說都是幾百ps 級別的。 可以通過“List Paths”命令查看。這里的Tsu/Tco 主要由器件工藝決定, 工作時在受到溫度,電壓的影響略有變化。

2021-01-19 15:23:00 7

7 1. 片內的Tsu/Tco 是指前級觸發器的Tco 和后級觸發器的Tsu, 一般來說都是幾百ps 級別的。 可以通過“List Paths”命令查看。這里的Tsu/Tco 主要由器件工藝決定, 工作時在受到溫度,電壓的影響略有變化。

2021-01-29 16:27:07 11

11 基于成對約束的聚類分析是半監督學習的一個重要研究方向。成對約束的數量已成為影響該類算法有效性的重要因素。然而,在現實應用中,成對約束的獲取需要耗費大量的成本。因此,文中提出了一種基于安全性的成對約束

2021-05-10 16:05:42 2

2 上一篇文章介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-01-21 17:03:00 1519

1519 TCO Certified是當前針對信息技術產品的一項全方位的安全、環保和可持續性的認證方案。隨著IT 產品日益頻繁地更新換代,TCO 認證的規范也每三年進行一次更新。當前應用中的TCO認證規范

2023-03-03 16:34:30 3020

3020 示例中采用的是“硬約束”,因為定義在類中的約束與隨機時指定的內嵌約束“矛盾”,所以導致約束解析器解析隨機失敗,即“硬約束”要求所有相關的約束條件不能互相矛盾,否則將會隨機失敗。

2023-03-15 16:56:58 2539

2539 今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被穩定的打入觸發器,Tsu就是指這個最小的穩定時間。對應圖1的Tsu(Tsu:set up time)

2023-06-28 15:40:07 1534

1534

本文將詳細介紹輸出延時的概念、場景分類、約束參數獲取方法以及約束方法

2023-07-11 17:12:50 1288

1288

上一篇文章《暗藏玄機的SV隨機化》介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-09-24 12:15:30 396

396

電子發燒友App

電子發燒友App

評論