SAMC21(一款 Cortex-M0+ MCU)非常適合需要數學計算的應用。SAMC21 MCU 具有可進行乘法運算的快速單周期乘法器選項,還具有一個新的外設,稱為除法和平方根加速器

2018-07-19 09:25:25 5283

5283 除法運算。很多人覺得不就是除法嘛,直接打上/即可,但是,FPGA是不能正確綜合這個除法器的,綜合的結果只是一個固定數值,而不像其他微處理器。可以這么說,用FPGA實現除法運算是比較麻煩的。

2020-06-17 10:17:27 6533

6533

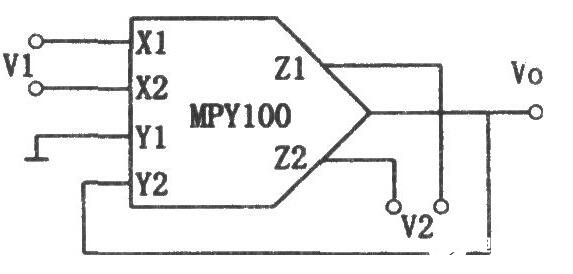

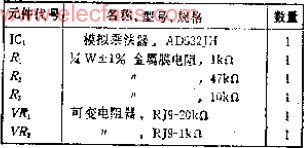

減法電路是基本集成運放電路的一種,算術運算電路主要包括數字**加法器電路、數字減法器電路、數字乘法器電路和數字除法器電路。

2024-02-19 10:00:17 310

310

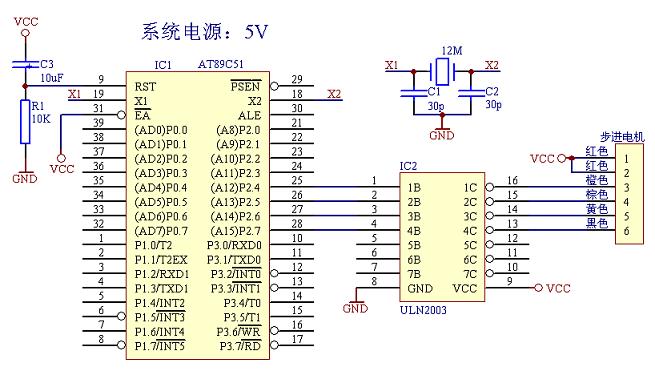

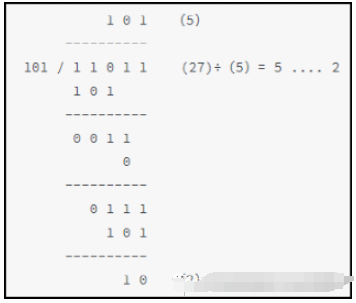

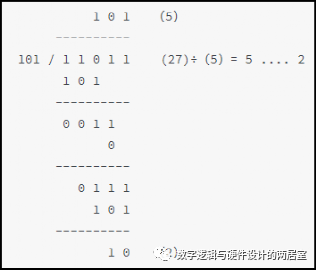

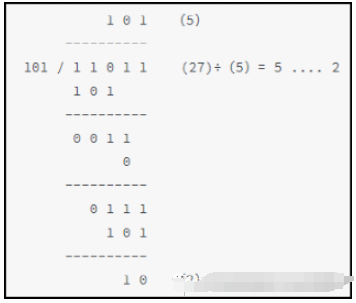

代替,比如可以先用除法運算獲得整數部分,然后用求余運算獲得余數,再對余數進行運算。2、本例實現一個除法運算,所得上的整數部分送P1口顯示,小數部分送P0口顯示。3、實現方法,本例計算101除以2的結果

2012-03-22 10:47:30

Verilog中用*實現乘法和用乘法器ip核實現乘法綜合結果有哪些不同?

2016-03-18 09:35:13

剛學習FPGA一個禮拜,從樹上抄了一段小程序,16位除法器,QUARTUS2調試出來波形總是不對(偶爾有幾段是對的),還望大神指教,本人菜鳥。程序: module DIV16(input CLK

2015-05-05 14:12:07

一個變量除以一個常數81,怎么寫啊 。想直接調用IP核,可是還沒法控制什么時候進行除法運算。又不想自己寫除法器求指點啊!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

2013-04-16 15:08:35

剛剛學習verilog,夏宇聞的《verilog數字系統設計教程(第三版)》中,P143中圖10.3,乘法器延時為1個與門和8個全加器的延時,為什么是 8 個?我覺得應該是 10 個全加器延時,請求大神幫忙解答一下,謝了。

2014-10-10 23:04:39

我在Verilog中遇到二進制除法問題。我想得到一個包含商的輸出。我稍后將處理decima的位置。以下代碼完美地運行,我可以顯示輸出,它與我正在尋找的完全匹配。分配股息= 48

2019-08-19 10:49:19

主頻在400Mhz,輸入端可配置,最大128位,整數無符號除法(四舍五入),重點是在10個周期內算完。

2016-07-25 08:04:46

- 例程2,ADC濾波算法04 - 總結1us的誤差,足矣改變這個世界 ————CSDN根號301 - 為什么整數位移比乘除法高效??首先,整數位運算要比乘除法要高效。如果學過計算機組成...

2021-12-24 07:33:48

4.3 實例九 除法器設計4.3.1. 本章導讀要求掌握除法器原理,并根據原理設計除法器模塊以及設計對應的測試模塊,最后在 Robei可視化仿真軟件經行功能實現和仿真驗證。設計原理這個除法器的設計為

2021-11-12 07:03:52

使用AD633與AD711按照官方提供的電路搭建了一個除法器,在使用中發(fā)現與實際不符,求解答 一. 這是輸入的兩個信號,最上面一個作為被除信號,下面一個作為除信號。 這是通過除法器后的信號,其中

2019-02-12 14:10:52

本帖最后由 gk320830 于 2015-3-5 13:40 編輯

手冊上說可以接成除法器,但沒有給出實際電路,望高手指點。。。

2012-03-25 14:20:07

請問由八位的輸入數據,怎么得到CRC編碼后的16位數據啊?verilog里面怎么做除法運算?

2014-10-25 20:05:44

請問一下大家,幾個疑問(可以肯定代碼是沒有問題的!):一,為什么可以在這里把小數直接強制轉換成無符號的整型?二,這樣強制轉換后的結果可能會是零?三,這樣轉換后,是如何保證計算精度的?四,這樣轉換背后的意義在哪里?

2022-02-15 14:24:54

請問一下大家有沒有用Xilinx的除法器IP核的,版本是V3.0的!我們在做有符號數除法的過程中運算結果經常出錯!原先做的產品,Divider的工作頻率是40M,后來工作頻率變?yōu)?2M時就經常出錯

2015-03-06 19:42:16

,占用的資源就越多。雖然有IP可以直接調用,但我們還是要了解FPGA中除法的原理,手動來寫一個除法器。FPGA中除法原理兩個32的無符號整數除法,被除數a除以除數b,他們的商和余數都不會超過32位

2020-12-24 16:06:22

;humi_ge=humi_dat%10;temp_bai=temp_dat/100;temp_shi=temp_dat/10%10;temp_ge=temp_dat%10;end這個程序大神們看一下,我在ISE中不能綜合但是在Quartus2中能綜合,請問用verilog 實現任意整數的除法和取模怎么辦?

2013-10-08 08:47:49

本帖最后由 第二道彩虹 于 2022-1-15 21:34 編輯

Labview自帶函數計算精度大多為二進制32位,對于一些高精度計算精度不夠。在網上沒有找到Labview更高的精度函數,因此

2021-12-27 16:35:15

有效, 可以分拍有效, 這時候除法器還會根據送入除法器的接口數據順序進行計算。 如下圖時序 除數和被除數數據來臨的時刻不相等, 而希望按照順序進行做運算, 這時候使用 blocking 模式最好

2021-01-08 17:00:55

和Cordic的互聯除法器的輸入可以由除法器的結果或Cordic的結果直接輸入,這樣構成了除法器和Cordic的級聯。比如計算tan(z),可以直接把Cordic的輸出sin(z)連接到DVD,cos(z)連接

2018-12-11 10:57:03

`Xilinx FPGA入門連載34:超聲波測距終極結果顯示之除法器IP解析特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1概述在本例

2015-12-09 12:22:00

本帖最后由 taiyangshenniao 于 2013-9-5 16:42 編輯

各鐘加法器,乘法器,除法器,的verilog 的實現,(位運算)

2013-09-05 16:41:14

`大蝦們,小女子最近調程序的時候用到了ise ip core的除法器,但是調用modelsim仿真的時候發(fā)現木有進行除法啊,單獨寫了個除法器也還是用不了,這是什么情況呢?(vhdl寫的程序哈)`

2013-06-15 11:52:45

小弟是初學者,剛把verilog基本語法看完,只會寫簡單的四位或者八位的加法器,但是兩個4位加法器級聯構成一個8位加法器不會寫啊,應該是頂層調用兩個四位的,但不知道具體怎么寫,求大神指點!不勝感激!

2013-12-03 11:51:06

請問關于乘法器的Verilog 程序中,移位累加具體每一步是怎么走的,自己琢磨了一番,感覺不是太懂,求高手解釋。(明白二進制乘法的計算過程)

2015-10-17 23:08:02

用Verilog設計五模除法電路。。。可是無知的我連五模除法電路是什么都不知道啊 !!求多模除法電路的資料啊!!

2014-03-30 10:16:00

請問下大家,,進位選擇加法器和進位跳躍加法器的區(qū)別是啥啊?我用Verilog實現16位他們的加法器有什么樣的不同啊?還請知道的大神告訴我一下。。

2016-10-20 20:23:54

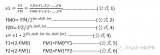

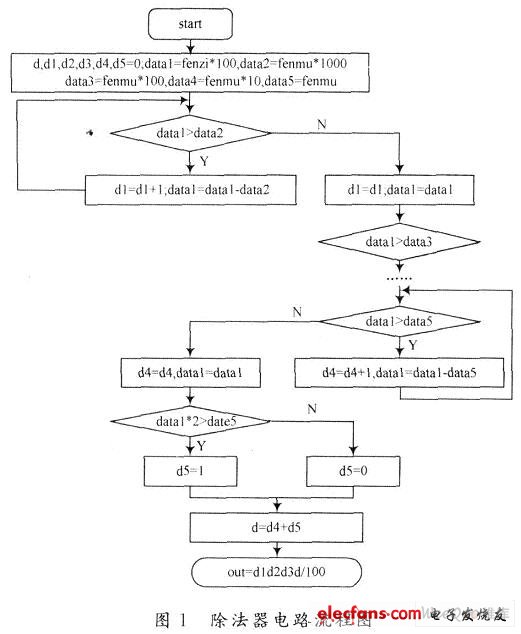

的工況就不太適用。筆者的工作室長期承接單片機、電路、機電液、工控、自動化、軟件EXE編程等項目,最近做了個單片機計算器的設計,在設計除法時利用長整形除法和取余運算,可以得到若干小數位的精度運算,與大家

2013-11-19 19:26:38

想問一下大家 單片機使用硬件除法器求出的商和余數數據怎么處理呢

2023-10-30 08:28:51

哪位有模擬除法器的電路仿真,我需要一個簡單的除法運算電路。MULTISIM10上面的除法器只是個代號沒有實際的型號,我用AD532來做結果不行。

2013-12-16 11:10:24

介紹了等精度測量頻率的原理,利用Verilog硬件描述語言設計實現了頻率計內部功能模塊,對傳統的等精度測量方法進行了改進,增加了測量脈沖寬度的功能;采用AT89S51單片機進行數據運算處理,利用

2011-03-07 12:44:31

定點除法器的輸出是商和余數的形式,但是我想讓他表示成小數的形式(因為最后要送到數碼管顯示),該怎么裝換?求大神,給點思路也可以!總共是8位顯示,而整數部分和小數部分的位數不定?怎么設計

2014-05-15 20:01:12

本文中介紹了如何在verilog編碼時使用自己想要的加法器和乘法器等

2021-06-21 07:45:56

在處理雙精度數時,經常會涉及到拆分雙精度數的整數和小數部分。有一下幾種解決方案:一、解決這個問題我們首先想到的可能是通過幾個取整函數,先求取整數部分,然后利用差值求取小數部分。取整函數包括最近取整

2014-10-17 14:01:05

有沒有人對如何用參數化加法器樹編寫Verilog有任何建議,輸入參數是操作數的數量?加布里埃爾以上來自于谷歌翻譯以下為原文Does anyone have any suggestions

2019-04-25 13:28:42

求助,有沒有大神用verilog寫過浮點矩陣乘法器的,我寫出浮點乘法器和加法器之后就進行不下去了,急求助!!!只有一個積分~~~

2017-09-18 09:22:03

求大神分享一種基于Verilog計算精度可調的整數除法器的設計

2021-04-29 06:30:43

有哪位親知道除法器選用哪種型號的比較好?是用作PSD位置傳感器的外圍電路,我在網上找到的最便宜的一種是一百多,不知道可不可靠。。另外,用運放實現電流到電壓的轉換 電阻和相位補償的電容取多少合適呢?我看到上面有寫電阻不宜過大 易產生自激,但所給原理圖上用了1M。。求各路大神指點

2014-08-18 23:35:53

簡單給大家分析一下嵌入式C語言編程時用到的除法與移位。 除法土豪 除法在嵌入式微處理器里可算是一個消耗大戶,復雜的實現方式不僅占用了大師寶貴的計算時間而且精度有限情況下占用了大片的RAM。因此

2019-04-30 00:31:32

除法器和32bit硬件乘法器,能自動執(zhí)行有符號或32位整數乘除法和開根號運算。硬件運算大大提升了應用程序的效率,減少了代碼運算量,相比軟件它們對于特定問題計算速度更快,位寬更大。 下面和大家一起配置

2018-11-30 09:23:40

請問在Verilog里可以直接用'/'來做除法嗎?如果不能要怎樣做除法呀??希望知道的人能夠指點一二。。。

2016-09-08 11:33:56

判斷。直到,B 完全移位后得出結果C 。 除法:首先,讓被除數(A)與除數(B) 進行比較,當被除數不小于除數時,才能進行整數除法。然后,讓C自加一,讓被除數(A)減除數(B)后賦值給被除數(A)。直到,被除數小于除數,得出最后結果C 。計算模塊的內容就是這些了。下面附上源代碼:

2016-09-01 09:03:33

這是一個高速硬件除法器,要求畫出此硬件的除法器的工作流程圖。說明其工作原理特別是高速原理。要求有仿真時序波形圖并說出說明在fpga上驗證器硬件功能。

2020-12-17 09:10:03

本文在設計實現乘法器時,采用了4-2 和5-2 混合壓縮器對部分積進行壓縮,減少了乘法器的延時和資源占用率;經Xilinx ISE 和Quartus II 兩種集成開發(fā)環(huán)境下的綜合仿真測試,與用Verilog

2009-09-17 11:13:21 27

27 TI推出的CDC706是目前市場上體積最小且功能強大的PLL合成器/乘法器/除法器之一。盡管其物理外形非常小巧,但卻極為靈活。該器件能夠在特定輸入頻率下生成幾乎獨立的輸出頻率。

2009-11-26 14:35:47 21

21 AD534是一款單芯片激光調整四象限乘法器/除法器,可提供以前只有昂貴的混合式或模塊式產品才具有的精度規(guī)格。無需外部調整便可保證±0.25%的最大乘法誤差。該器件具有出色的電源抑制、低溫度系數,結合

2023-06-28 11:13:29

AD534是一款單芯片激光調整四象限乘法器除法器,其精度規(guī)格以前只有昂貴的混合或模塊化產品才有。無需任何外部調整,AD534L的最大乘法誤差保證為0.25%。出色的電源抑制性能、低溫度系數以及片內

2023-08-09 16:52:53

在FPGA中實現高精度快速除法

2010-07-17 16:33:18 25

25 高精度的乘除法和開方等數學運算在FPGA實現中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應用中,以處理時間換取資源的串行運算方法具有廣泛的應

2010-07-28 18:05:14 37

37 描述AD534是一款單芯片激光調整四象限乘法器/除法器,可提供以前只有昂貴的混合式或模塊式產品才具有的精度規(guī)格。無需外部調整便可保證±0.25%的最大乘法誤差。該器件具有出色的電源抑制、低溫度系數

2024-01-11 15:27:16

AD532是首款預調整的單芯片乘法器/除法器;無需任何外部調整電阻或輸出運算放大器,即可保證±1.0%的最大乘法誤差和±10 V的輸出電壓范圍。AD532經過內部調整,易于使用,為設計

2010-10-02 09:37:50 132

132 AD534是一款單芯片激光調整四象限乘法器/除法器,可提供以前只有昂貴的混合式或模塊式產品才具有的精度規(guī)格。無需外部調整便可保證±0.25%的最大乘法誤差。該器件具有出色的

2010-10-02 09:39:56 133

133 51單片機的高精度除法程序及使用

開發(fā)人員在開發(fā)51單片機應用系統過程中,往往遇到多字節(jié)除法及倒數問題。但目前一些資料中所介紹的有關程序,復

2008-09-09 10:12:28 2044

2044

并行除法器 ,并行除法器結構原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運算部件,采用大規(guī)模集成

2010-04-13 10:46:30 14666

14666 除法器對數運算電路的應用

由對數電路實現除法運算的數學原理是:

2010-04-24 16:07:27 2520

2520

用于比率計算的除法運算電路

電路的功能

本電路是用X除輸入信號Z

2010-05-08 15:29:01 1618

1618

介紹一種在 8096 /96 系列單片機上實現的單精度 浮點數 快速除法。該算法采用了預估一修正的數值計算方法,并充分利用了16 位CPU 中的乘除法指令,計算速度快、精度高,有很強的實用

2011-06-03 16:47:06 93

93 輾轉相除法是整數和多項式理論中求最大公因數和最大公因式的一類重要方法,對于較大的兩個整數和次數較高的兩個多項式而言,利用輾轉相除法手動計算它們的最大公因數和最大公

2013-06-06 10:54:26 0

0 模擬除法器是一種能實現兩個模擬量相除的電子器件。目前不僅應用于模擬運算方面,而且已擴展到無線通訊、電視廣播、人工神經網路、機器人控制技術等領域。此外,模擬除法器在模糊控制和測量儀表中也是非常重要的器件。

2014-09-19 15:14:31 3096

3096 計算機如何來計算除法的?

第一步:分析除法

第二步,計算機中對第一步的模擬(真值)

2015-12-31 10:43:18 15

15 8乘8乘法器verilog源代碼,有需要的下來看看

2016-05-23 18:21:16 24

24 同相加法器輸入阻抗高,輸出阻抗低 反相加法器輸入阻抗低,輸出阻抗高.加法器是一種數位電路,其可進行數字的加法計算。當選用同相加法器時,如A輸入信號時,因為是同相加法器,輸入阻抗高,這樣信號不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 55183

55183

Verilog-A 將設計精度推向一個新的水平

2017-01-14 15:20:31 13

13 Verilog-A 將設計精度推向一個新的水平

2017-01-14 15:20:31 12

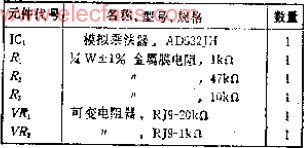

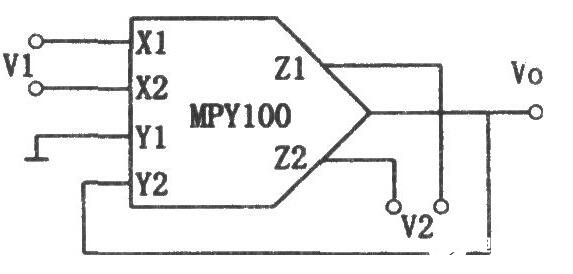

12 輸入信號為V1、V2,輸出Vo為Vo=10V2/V1。這種除法器是將乘法器接在運算放大器的反院回路組成的。V1的輸入范圍為-0.2V到10V,V2的輸入范圍為-10V到10V。

2019-12-31 14:12:44 17759

17759

在FPGA的開發(fā)應用中,大多數EDA軟件(后面以altera QuartursII為例)都提供乘除法、開方運算的設計向導,或提供LPM宏函數,但普遍占用資源量大。而在許多信號處理應用中,要求計算精度

2020-07-29 17:48:57 1155

1155

verilog實現加法器,從底層的門級電路級到行為級,本文對其做出了相應的闡述。

2021-02-18 14:53:52 5585

5585

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。乘法器不僅作為

2021-02-18 15:08:01 24392

24392

AD533:低成本乘法器、除法器、平方器、平方器、根過時數據表

2021-04-30 21:05:33 3

3 AD533:低成本乘法器、除法器、平方器、平方根過時數據表

2021-05-07 10:50:33 20

20 AD734:10 MHz四象限乘法器/除法器數據表

2021-05-15 10:18:05 12

12 簡化合成器的有源乘法器和除法器

2021-05-16 17:15:02 9

9 介紹各種加法器的Verilog代碼和testbench。

2021-05-31 09:23:42 19

19 4.3 實例九 除法器設計4.3.1. 本章導讀要求掌握除法器原理,并根據原理設計除法器模塊以及設計對應的測試模塊,最后在 Robei可視化仿真軟件經行功能實現和仿真驗證。設計原理這個除法器

2021-11-07 10:51:04 18

18 整數在 IEEE 的規(guī)定上有短整數 short integer , 中整數 integer 和 長整數 long integer

2023-02-13 15:00:13 1142

1142 14 級紋波進位二進制計數器/除法器和振蕩器-HEF4060B_Q100

2023-02-15 18:53:56 0

0 14 級紋波進位二進制計數器/除法器和振蕩器-HEF4060B

2023-02-15 18:54:07 1

1 取被除數的高幾位數據,位寬和除數相同(實例中是 3bit 數據)。

2023-03-27 11:32:13 502

502

本文是本系列的第四篇,本文主要介紹FPGA常用運算模塊-除法器,xilinx提供了相關的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:20:45 1840

1840

取被除數的高幾位數據,位寬和除數相同(實例中是 3bit 數據)。

2023-05-30 17:31:39 742

742

進行整數除法時,結果值略去小數部分,只取整數部分

2023-06-25 10:17:37 3472

3472

FPGA實現除法的方法有幾種,比如直接用/來進行除法運算,調用IP核進行除法運算,但這兩種方式都有個共同的問題——都是黑盒子,在進行時序違例處理時,往往不好操作,比如想打打拍改善下時序都不知從何下手。

2023-07-04 10:03:39 599

599

使用IAR IDE仿真RL78內置硬件乘法器和除法器注意事項

2023-10-30 17:04:14 468

468

電子發(fā)燒友App

電子發(fā)燒友App

評論