本應用筆記利用基于MAXQ1850的雙芯片架構的優勢,探討了高度安全的支付終端設計,分析了生產廠商在面臨PCI-PED PTS產品認證時的弱點。

新終端、新趨勢

金融終端已經成為支付產品公司提供的一種新型交付服務手段。金融終端不再限于簡單的讀卡機,而是逐步成為能夠處理交易、管理庫存、操作商業運營的復雜計算設備。這一角色轉變的顯著標志是針對終端定義的一個新術語:從銷售終端(POS)設備更改為交互終端(POI)系統。POI系統必須具備快速通信能力,使用更加便捷(例如,可以連接USB、以太網、WiFi?或Bluetooth?),支持多應用的相互協調并可處理復雜的卡交易(支付卡、忠誠卡等)。

另外,使用條件也發生了變化。有時,POI必須工作在潮濕環境、室外或室內。這些設備多數情況下要求采用人性化便攜式設計,并滿足經銷商對時尚外觀的需求。由于相關技術的融合與重復利用,使得終端產品隨處可見,例如:智能電話、筆記本電腦、游戲機控制臺等。現代POI設備引入了類似的美學設計,采用色彩豐富的顯示技術、復雜的觸摸屏接口并提供便利的連通性,可以方便地集成到信息系統內。硬件技術的深入開發也帶動了軟件設計的重復利用,從商用化操作系統到軟件棧,可以直接提取硬件電路。總而言之,軟件的重復利用有助于加快開發速度、降低產品失效風險,以更低的R&D成本將產品快速推向市場。

終端安全性

POI與消費類(CE)設備的主要差別在于安全性。EMV卡的全球化開發意味著系統所要面臨的威脅也是全球性的。如不采取適當對策,則有可能在瞬間遭受來自世界不同區域的攻擊。另一方面,由于高投資(開發工具、時間等花費)帶來的巨額回報,犯罪團伙會不惜代價地實施攻擊行為,由此可見,設備安全性的最大威脅來自于這些犯罪團伙。

當前金融終端的互操作性、通信接口以及高級服務都已成為攻擊者的“敲門磚”。由業內重要的支付產品公司聯手創立的支付卡產業安全標準委員會(PCI SSC)—包括美國的Express、JCB、MasterCard和Visa—旨在規范整個產業的安全標準。

PCI SSC開發的PCI PIN交易安全(PCI PTS)標準定義了金融終端安全性的要求。前期的PCI PIN輸入設備(PCI PED)標準(PCI PTS)主要關注應對物力和邏輯攻擊,這些攻擊行為試圖從POI提取PIN碼和加密密鑰。根據現場經驗和試驗室研究,PCI PTS歸納了針對各種攻擊(物力篡改、環境更改、軟件接口攻擊、密碼分析破解攻擊、政策威脅)的安全防護機制。PCI PTS旨在保護終端內部或智能卡連接通道普通格式的PIN碼。

物理機制要求在入侵者打開終端、插入PIN記錄裝置,防止數據在PIN輸入或發送端被捕獲,并可阻止對終端操作的修改。邏輯上需要防止入侵者修改讀卡器、控制終端的運行程序,從而達到他們恢復、記錄或發送PIN碼及其它敏感數據的目的。

其它要求包括磁條數據的有效保護。PCI PTS的每項要求對應于特定的攻擊類別,與對抗等級有關,通常用16至35范圍的數字表示。為了達到設計目標,支付終端必須能夠將遭受篡改的風險(所謂的篡改值)降至最低。

按照ITSEC聯合實驗室聲明(JIL)對智能卡的規定,攻擊值方案基于所了解的相關知識、攻擊持續時間、攻擊者的資源和專業技術。對每種抗攻擊能力劃分成幾個等級進行評測,每個等級有相應的額定值。考慮一種攻擊形式時,可以由衡量每種類型的攻擊強度值的加和表示。例如,文件類保護包括三個等級:公開、受限、加密。如果一個受限文件受到攻擊,該等級的攻擊值(受限文件)需要增加到攻擊求和中。

抗攻擊能力評估需要在具備資質的實驗室進行,最終是否獲得批準的決定權由PCI PTS成員掌控。由于攻擊者可以接觸到支付終端設備,PCI PTS特別規定了能夠抵抗各種威脅、保護卡持有人敏感數據的安全等級。PCI PTS并不提供相應的解決方案,需要制造商想方設法滿足這些條件的要求。PCI PTS 3.1已于2012年3月替代PCI PED 2.1標準,隨著安全等級不斷提升,終端廠商將面臨更加嚴峻的設計挑戰。

PCI PTS 3.x

PCI對支付終端的安全要求發生了重要改進,加強了對最新攻擊威脅的防御。另外,其新方案的提出也促進了模塊化開發,用于簡化生產。這一演變的標志是將PIN輸入裝置(PED)變更為POI裝置,反映出使用端的變化。終端裝置與之前一樣需要執行金融交易,但現在需要執行更多任務,新需求也說明生產廠商已經考慮了PCI SSC這種擴展能力。

從整個過程看,認證過程已經簡化為對包含所有類型裝置(POS、EPP、自動售貨機、售貨亭)的一次性評估,分為兩個強制評估模塊:設備的核心要求和集成要求。另外還有兩個新的評估模塊供廠商選擇。

為確保安全性,根據現場反饋對具體要求進行了少許修改和加強。一些關鍵要求已經使其攻擊值從1點增加到2點,尤其是與物理攻擊(鍵盤、磁條和卡槽)相關的攻擊。攻擊成本值介于16至35 (PCI PED 2.1標準下為14至35)。此外,現在通過指定請求的規則更嚴格。較早的標準只要求攻擊準備和攻擊開發值之和等于一個最小值;現在,攻擊開發值本身必須具有一個最小值(攻擊準備為識別階段,攻擊者在此期間研究問題、設計方法,以及測試設備。在開發階段,攻擊者進入公共場所,并實際進行數據盜取)。

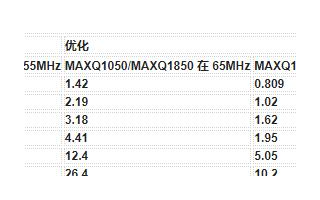

其它新要求明確針對新POI架構和服務。舉例說明,要求B17考慮在同一終端上運行多項應用的情況,這完全反應了現代終端的軟件架構。另一個例子是新可選評估模塊的創建:開發協議(Open Protocol)模塊處理開放/公共網絡上的安全問題,通常解決來自于通過IP連接的終端安全事項,類似于PC日常面臨的攻擊威脅。安全讀取與數據交換(SRED)模塊規定對終端內持卡人賬戶數據的保護要求。表1列出了大多數關鍵的安全要求,以及對設計高效率、高性價比終端的功能性要求。

控制安全方案的成本

終端廠商為了滿足嚴格的安全標準,在設計功能強大、外觀時尚的POI設備時面臨巨大挑戰。終端廠商自己開發并維護安全設備可能付出巨額代價,因為這將要求終端廠商專門建立一支專家團隊,從而占據相當大的R&D資源。這也成為新生力量進入安全市場的巨大障礙,但它并不代表現有廠商擁有多么明顯的競爭優勢,畢竟支付終端的所有安全認證條件都是強制性規定。

標準化為專業廠商的安全模塊創造了巨大商機。由于認證標準是統一的,終端廠商可以選擇商用化的安全方案以滿足安全認證標準的要求。與自主開發安全方案相比,這些模塊化設計具有幾項顯著優勢。

它們能夠減輕終端制造商的設計負擔,只需關注系統增值功能。安全性雖然不是設備的特殊功能,但卻是對終端產品最基本的標準化要求。通過與安全產品供應商合作,終端廠商能夠將主要精力放在金融終端市場的增值服務上。

高性價比設計允許開發更加復雜的安全機制。由于多個用戶共同分攤R&D成本,使得高科技開發資源不會形成一家獨占的局面。隨著對安全產品復雜性要求的提高,這些降低設計成本的因素也愈加重要。由此可見,金融終端市場也依賴于能夠提出有效應對措施、專業的安全產品供應商。

利用獲得批準的模塊降低風險、加速POI認證。對商用化方案進行安全評估并獲得PCI PTS批復,模塊供應商能夠降低終端設計人員的開發風險。從而簡化安全系統集成,加快通過終端認證的步伐。

MAXQ1850中文資料,pdf datasheet:http://www.nxhydt.com/soft/78/223/2009/2009061932097.html

安全架構綜述

目前,市場上的支付終端主要采用三種不同類型的架構,以不同形式提供安全接入服務,資產保護和其它功能集成在終端內,表1列出了相關需求。

安全管理器

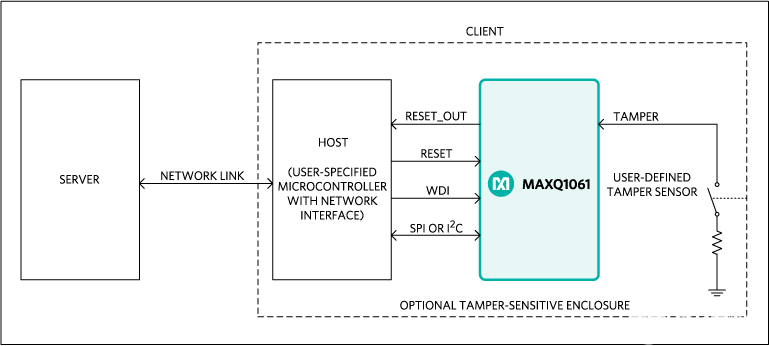

最通用的架構之一是采用安全管理器,為通用微控制器(μp;C)增添安全功能。安全管理器能夠有效保護敏感憑證、偵測物力或環境篡改事件(例如:改變溫度或電壓)。外部傳感器輸入允許連接安全防護罩、PCB防護網和篡改傳感器(圖1)。

?

圖1. 基于安全管理器IC的支付終端

Maxim的DS3600等安全管理器引入了受專利保護的無痕跡存儲器架構,利用片上NV SRAM存儲加密密鑰。電池備份存儲器能夠消除氧化應力在存儲器留下的痕跡,防止對受應力作用的存儲器單元的殘余數據進行無源偵測。一旦檢測到入侵操作,將立即、徹底地擦除NV SRAM的內容。這些安全管理器還提供隨機數發生器等其它安全服務,通過通用微控制器(μC)進行系統維護和運行控制,包括加密服務和敏感接口控制。

雙芯片架構(雙控制器)

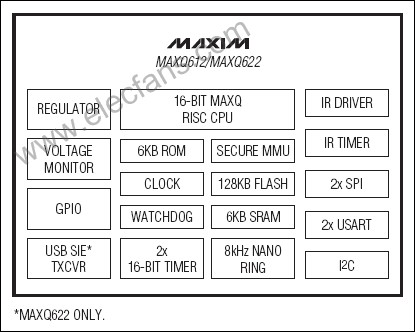

第二種方案是采用通用μC和安全配套芯片把計算與安全功能分隔開(圖2)。通用μC執行所有與安全性無關的任務,而安全協處理器包含了另一μC,作為報警系統執行加密計算、控制敏感接口。

?

圖2. 由通用μC和專用安全μC構成的雙芯片架構

通過專用的控制接口連接兩個μC,以避免敏感信息的泄漏。這種架構非常適合現代POI設計,這類產品大多在商用化方案的基礎上使設計滿足PCI PTS要求。終端設計人員可以選擇通用μC單獨完成系統的功能性、連通性任務以及計算功能;安全μC則用于處理所有安全保護操作,例如:PIN和密鑰管理、電池備份存儲器、篡改偵測、加密計算等。這款μC的選擇只需要單純考慮如何滿足PCI PTS安全性認證的要求,因此可以選擇預先通過認證的商用化解決方案。

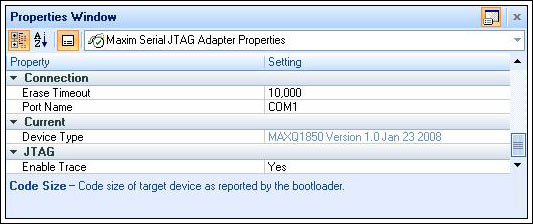

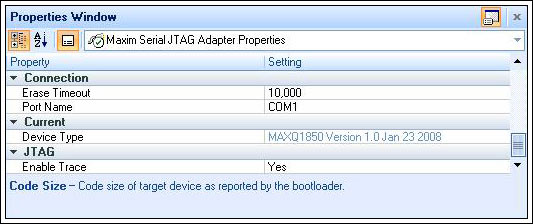

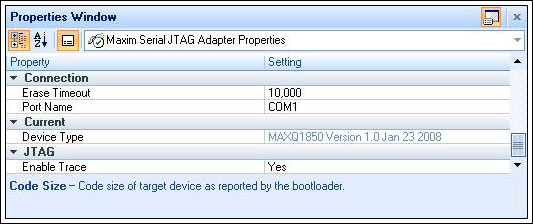

安全配套芯片

MAXQ1850即為該系列產品的代表器件,這款32位安全μC設計用作任何通用μC的配套芯片。按照芯片安全評估報告的陳述,MAXQ1850能夠滿足最嚴格的PCI PTS標準要求:

連接到電池備份存儲器的篡改響應傳感器提供物力篡改保護,一旦檢測到篡改事件立即執行擦除操作

強大的保護功能能夠在發生故障和環境干擾(脈沖干擾、極端溫度等)狀況下提供可靠保護

嵌入式存儲器用來保存敏感資源(例如:密鑰和固件)

裸片防護網用于保護嵌入式存儲器

安全加密功能支持所有算法(旁道攻擊對策)

高度安全的隨機數發生器用于產生密鑰

直接控制敏感外設(例如:智能卡、鍵盤和顯示器)

表1列出了MAXQ1850所滿足的關鍵安全特性和設計要求,其高性能RISC核、較少的引腳數量以及所集成的關鍵電路使其非常適合POI系統設計,其中包括超小尺寸的便攜設備。從圖2可以看出,采用雙芯片架構,MAXQ1850能夠有效簡化POI設計。

智能卡接口的I/O選擇機制允許通過一個接口管理雙卡,通過SPI?接口控制智能卡接口芯片(DS8024)。

利用GPIO作為片選,智能卡接口和LCD可以共用SPI端口。

級聯MAX7317 SPI至GPIO轉換器,簡化GPIO/SPI端口的配置管理,用于訪問并行外設。

USB鏈路連接安全μC和通用μC,通過安全應用編程接口API連接。

集成的安全μC#e#集成的安全μC

第三種方法,也是隨著PCI PED認證的普及而被廣泛用于安全金融終端的方法,即選擇融合高集成度、高性能μC的單芯片架構(圖3)。與通用微控制器一樣,這些μC采用了最新的半導體制造工藝;具有多種通信接口,例如USB、SPI和智能卡;并且支持功能豐富的操作系統,例如Linux? OS。這些微控制器嵌入了高速現代處理器,能夠管理大容量外部存儲器,例如NOR和NAND閃存,以及各種各樣的RAM。

?

圖3. 大多數小尺寸終端架構采用的單片μC包括了所有必要的安全功能。

與安全管理器一樣,這些器件嵌入了安全NV SRAM和篡改/監測傳感器。與配套芯片一樣,這些器件運行安全加密算法,例如3DES、AES和RSA,抵御功率差分析(DPA)和簡單的功率分析(SPA)。高集成度設計在安全保護能力和材料清單(BOM)均具備強大優勢。

安全機制集成在硅片內,能夠對其進行攻擊手段將非常復雜。集成保證了啟動的完整信任鏈,也適用于處理緊急事件和報警—報警信號不會被切斷。由于電路功能已經集成在一個芯片中,所以降低了鏈路缺陷造成的不良風險。使用集成的外部存儲器加密引擎時,無需額外的安全防護。

這種高集成度設計也有益于軟件的安全保護,因為安全機制依賴于強大的硬件功能和標準化機制,例如,存儲器管理單元(MMU)。注意,在單芯片方案中由軟件區分敏感數據和非敏感數據,雙芯片架構中則由硬件電路實現。軟件以三種形式劃分數據的安全等級,各有優缺點。第一種方法是采用“管理程序”,將敏感和非敏感數據分配到獨立的存儲單元;第二種方法則利用操作系統,例如Linux,直接進行劃分;第三種方法利用Java?軟件或Java類虛擬器處理獨立的安全程序。

多合一集成減少了所需的芯片數量,縮小PCB面積,允許使用更靈活的外形規格,從而簡化了終端設計。另外,由于只需要單個工具鏈、僅支持一個μC核,有助于加快開發進程。Maxim提供各種高集成度、16至32位安全μC,工作速率高達200MHz。

選擇安全μC時,應該選擇能提供PCI PTS實驗室出具的安全評估報告的微控制器。該報告證明經過了完整實驗室測試,測試結論表明了芯片廠家的專業水平,以及安全芯片所能達到的水平。第二項考慮是終端設計的難易程度。簡單程度既依賴于μC特性,又依賴于廠家支持團隊的力量。您應該尋求集成了關鍵功能的μC,例如存儲器、時間記錄和防篡改監測,因為這種高集成度簡化了PCB布線,以更小尺寸支持關鍵的安全特性。Maxim加入了PCI SSC組織,并堅持以最先進的安全μC服務于PCI SSC市場。

采用ARM926?內核的高性能、32位安全微控制器MAX32590 (“JIBE”)就是一款這樣的μC。器件的低功耗特性能夠在400MHz時提供卓越的性能。安全特性包括:具有瞬間擦除能力的2KB安全存儲器、安全實時時鐘(RTC)、以及檢測任何入侵的內部環境動態監測傳感器。易失和非易失外部存儲器(如:NAND、NOR和LPDDR)由新一代強大的AES-128加密/數據完整性驗證功能完全保護。所提供的配套軟件包括:預認證POI參考設計、安全Linux OS、加密庫、EMV L1庫和PCI PTS幫助工具。

通過PCI PTS 3.x認證的參考設計

Maxim的參考設計(USIPOS)能夠幫助構建高度可靠的終端產品,確保通過PCI評估。通過PCI PTS 3.x測試的參考設計為您的終端提供最便捷的渠道,使其順利通過認證。USIPOS參考設計的關鍵特性包括:無網格架構、獲得PCI PTS 3.x批準,提供經過優化的硬件BOM、安全的Linux OS和EMV L1及加密庫文件和硬件/軟件設計指南。從Maxim的設計方案、電路布局和BOM入手,定制設計并集成到您的設備中,從而以最低的風險和成本將您的產品快速推向市場。

安全島

除安全芯片及其管理的資產外,其它資產,例如PIN,也是攻擊目標。作為預防措施,利用安全芯片外部的傳感器提供保護,防止對終端設備的物理篡改。由此構建的安全機制既高效,又容易集成,并且任何報警都會立即觸發擦除安全存儲器。這些傳感器往往監測的是片外環境,監測電路可以很好地保證其它物理區域的安全—例如,PIN所處的區域。最后,終端制造商必須具備足夠的技能和知識,正確管理報警檢測機制。由安全芯片管理報警的傳播和相應的操作。

對于PIN和持卡人賬戶數據等文本數據可通過鍵盤、磁條和智能卡獲取。因此,除了安全芯片本身采取措施外,這三個區域都需要各自的安全保護措施。資產管理數據只能暴露在這些設施以內,這也是我們稱其為“安全島”的原因(圖4)。

?

圖4. 支付終端中,由安全μC控制的傳感器保護"安全島"

基于商用化安全芯片的設計思路,有些廠商建議此類安全區域也采用商用化設計方案。最完備的解決方案是集成安全智能卡槽,例如C&K安全智能卡槽和磁條加密頭,例如磁阻芯片組。這些產品與上述安全芯片具有相同優勢—集成化設計,安全性高,降低風險和成本。

商用化終極方案

將上述商用化安全措施完全集成到單個參考設計中將對該行業的發展做出重大貢獻—有助于簡化終端制造商的產品開發、認證和生產(圖5)。安全是制造商面臨的主要問題,所以評估參考設計會增強其信心,節省資源,并降低了開發風險。它還以高效、高性價比設計兼容大多數苛刻的安全要求(PCI PTS)。

?

圖5. JIBEPOS參考設計框圖,包括所提供的各種功能

軟件和應用

終端由硬件組成,但相關軟件(不僅限于PIN輸入操作)在近幾年已經擴展到各種應用服務。有些設備提供忠誠度測試及其它相關業務的應用,復雜的軟件架構也是圖形界面、多接口(以太網、USB、GPRS連接)、EMV支持以及非接觸卡不可缺少的工具。強大的安全防護措施使得軟件設計更加復雜:終端設計必須極具吸引力,而安全應用決不允許泄露敏感數據,操作系統必須支持應用之間的通信,加密服務不得泄露密匙。商用化軟件還能夠為終端帶來眾多利益,包括節省開發時間和幫助最終產品通過認證。

作為一個示例,Maxim提議的安全Linux操作系統可用于USIP和JIBE平臺,完全滿足PCI PTS安全軟件要求,簡化開發過程并降低制造商的認證風險。可以獲取完整的Linux版本,還有助于改善終端開發,包括圖形界面、外設驅動和通信棧。

結論

以上討論的三種架構都可以構建強大的支付終端,提供高度可靠的安全性。本文涉及的IC均為經過驗證的商用化器件,可提高安全性,方便集成,并降低功耗。

電子發燒友App

電子發燒友App

評論