實時時鐘芯片(RTC)允許一個系統能同步或記錄事件,給用戶一個易理解的時間參考,這里分享一些實時時鐘芯片的設計資料,以及工程師在應用設計時應為了避開設計時出現的問題。

2016-07-25 11:08:49 5224

5224

在進行具體工程的抗干擾設計時,我們可以選擇有較高抗干擾能力的產品,采取抑制干擾源、切斷或衰減電磁干擾的傳播途徑和利用軟件手段等措施,來提高裝置和系統的抗干擾能力。

2018-11-01 08:55:30 6762

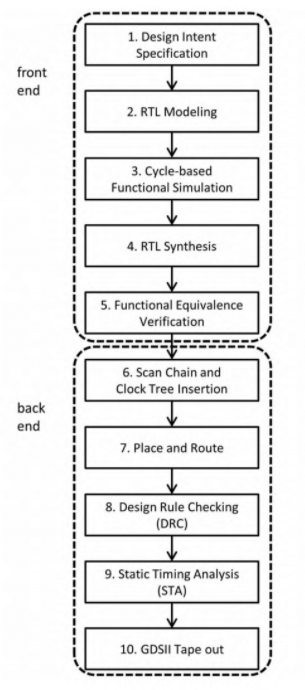

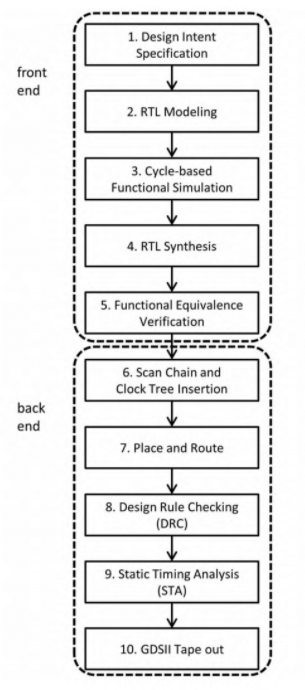

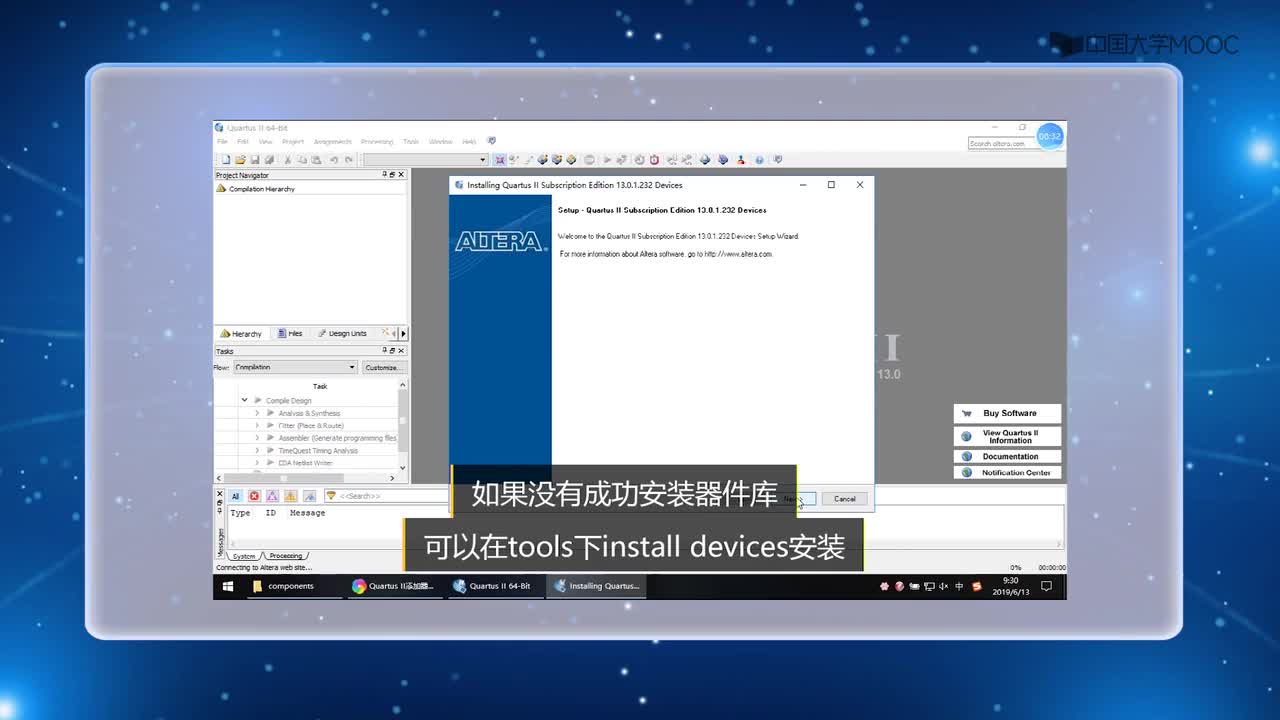

6762 FPGA的前端設計流程類似于ASIC,但后端不同。FPGA的后端部分與ASIC的主要區別在于FPGA的布局和布線。對于ASIC,place and route軟件決定IC的制造方式。

2022-06-20 16:24:12 4730

4730

ASIC1810 - ASIC1810 - List of Unclassifed Manufacturers

2022-11-04 17:22:44

1、概念區別: ASIC(專用集成電路)是一種在設計時就考慮了設計用途的IC。 FPGA(現場可編程門陣列)也是一種IC。顧名思義,只要有合適的工具和適當的專業基礎,工程師就可以對FPGA

2020-12-01 17:41:49

...................................493.2 設計工具 ISE 與 Vivado......................................493.3 ASIC 設計轉換

2015-09-18 15:26:25

`圖片上的這玩意叫做Astro Pi,Pi是什么意思我就不解釋了,Astro是天文的意思,那么這個樹莓派是干嘛用的,有什么功能大家應該不難猜到了吧。Astro Pi是增加了特殊定制外殼和配件的樹莓派

2016-01-11 10:49:58

我想生成8個相位時鐘。所以為此,我將不得不使用兩個PLL。我想確保所有生成的時鐘都沒有時鐘偏差。時鐘向導中是否有一個功能可以指導兩個PLL生成沒有偏斜的時鐘?或者有任何特定的方法來生成時鐘?提前致謝

2018-10-11 15:01:10

1.clock計時按鈕的計時時鐘是多少?和核時鐘一樣,還是核時鐘的幾分頻

2.顯示的計時周期也是按這個時鐘計算的吧???

2018-06-21 17:56:56

信號,就是這個道理。所以,連接排線一般也都在板子邊沿,且盡量短,盡量用扎帶固定。如果排線干擾,選用屏蔽線,效果可能會好一些。或者在線上套磁環,但這樣的缺點是不方便生產。4.時鐘信號導致的干擾及解決辦法

2022-10-22 08:00:00

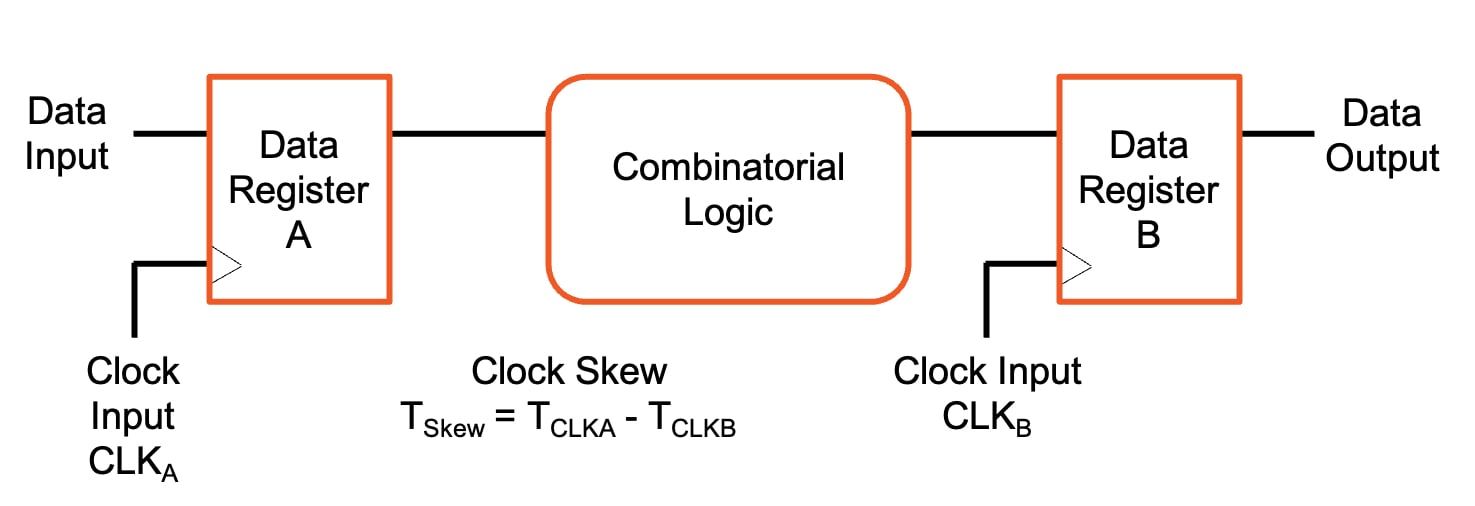

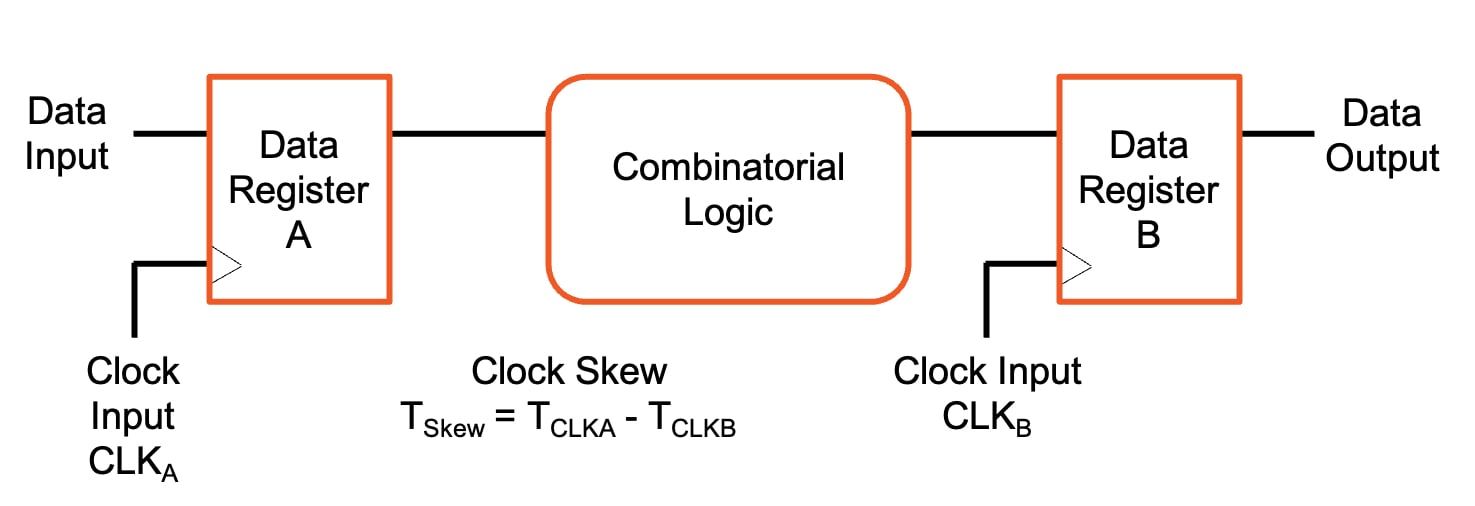

: 所設計系統的穩定情況下的最高時鐘頻率所設計系統的穩定情況下的最高時鐘頻率,他是時序分析中最重要的指標,綜合表現所設計時序的性能首先介紹最小時鐘周期TclkTclk = 寄存器的時鐘輸出延時Tco

2018-07-03 02:11:23

: 所設計系統的穩定情況下的最高時鐘頻率所設計系統的穩定情況下的最高時鐘頻率,他是時序分析中最重要的指標,綜合表現所設計時序的性能首先介紹最小時鐘周期TclkTclk = 寄存器的時鐘輸出延時Tco

2018-07-09 09:16:13

FPGA能否繼續在SoC類應用中替代ASIC?CoreConsole工具是什么,有什么功能?

2021-04-08 06:23:39

運用前須知:1、IWDG所用計時時鐘是不穩定的(35-60KHZ),通常取40KHZ計算.對以下代碼段,定時時間為:T=prer/40000*rlr,單位是Svoid watchdogInit

2021-07-30 06:49:17

時鐘振蕩 計時 評估板

2024-03-14 21:24:48

在設計最初, 由于沒有將時鐘信號定義在全局時鐘引腳上, 導致MAXPLUS II 在時間分析時提示錯誤:(時鐘偏斜加上信號延遲時間超過輸入信號建立時間). 全局時鐘引腳的時鐘信號到各個觸發器的延時

2019-09-19 05:55:36

時鐘振蕩 計時 評估板

2024-03-14 22:58:14

時鐘振蕩 計時 評估板

2024-03-14 22:58:14

2.定時器計時,ETR模式計數(1)問題分析問題由來:項目需要對一個外部輸入信號統計一段時間內負脈沖(低電平)的個數思路:一個定時器用來計時1分鐘,一個定時器通過ETR模式進行邊沿檢測并計數(本次

2021-08-19 07:49:16

ASIC的門密度范圍。SiliconCity柔性架構可讓設計人員針對多種產品變化型款,創建獨特的基礎晶圓架構,同時通過設計復用大幅縮短客戶的設計時間,減少非經常性工程(NRE)成本,并降低開發風險。

2019-08-29 06:00:52

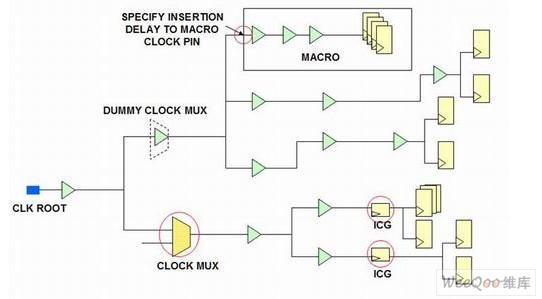

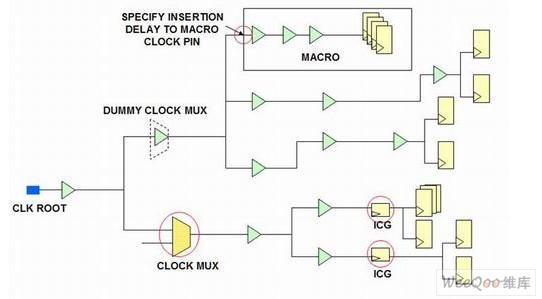

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

嗨,我們正在嘗試使用Vivado工具鏈手動路由FPGA,并想知道應該使用什么工具來手動路由Virtex 7 FPGA。還可以在Vivado時序分析器工具中指定溫度和電壓值來估算設計時序嗎?我們將如

2018-10-25 15:20:50

在對DCS系統進行工程的抗干擾設計時需注意什么?為了保證系統在工業電磁環境中免受或減少內外電磁干擾,必須從設計階段開始便采取三個方面抑制措施:抑制干擾源;切斷或衰減電磁干擾的傳播途徑;提高裝置

2011-11-21 16:55:42

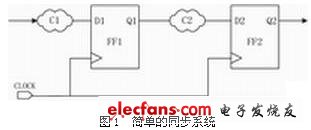

挑戰。本文主要介紹了邏輯設計中值得注意的重要時序問題,以及如何克服這些問題。最后介紹了利用Astro工具進行時序分析的方法。關鍵詞:ASIC;同步數字電路;時序;Astro引言 隨著系統時鐘頻率的提高

2012-11-09 19:04:35

基于DSP的變頻調速系統電磁干擾問題分析,怎么解決這些干擾?

2021-04-25 07:35:17

我的設計完全在Verilog中,并且已經使用Spartan FPGA進行了測試。我將源代碼提供給ASIC工廠,以實現作為ASIC使用他們(我認為)的概要工具。我的問題是,有沒有辦法使用任何

2019-07-25 13:44:31

邏輯。而對其進行時序分析時,一般都以時鐘為參考的,因此一般主要分析上半部分。在進行時序分析之前,需要了解時序分析的一些基本概念,如時鐘抖動、時鐘偏斜(Tskew)、建立時間(Tsu)、保持時間(Th)等

2018-04-03 11:19:08

親愛的大家,我對時鐘信號和數據信號進行采樣,想要饋送到IDDR2,但它需要兩個時鐘。所以我的采樣時鐘信號無法直接饋入IDDR2,需要反向采樣時鐘信號,如何反轉它使反轉信號沒有任何偏斜&與采樣

2019-06-11 06:11:26

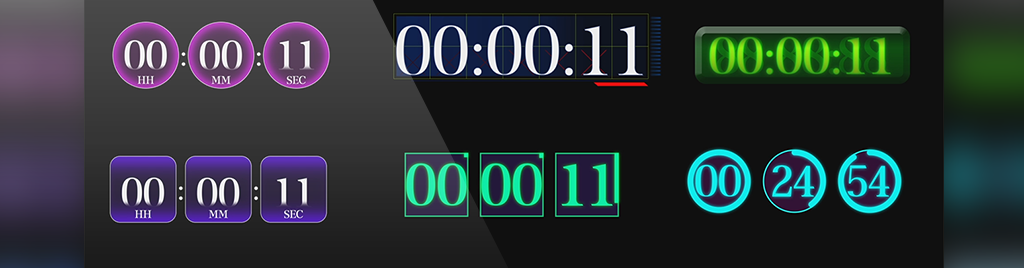

1)設計任務:完成倒計時時鐘的設計。2)指標要求(1)能夠分鐘級的倒計時,分鐘和秒顯示。(2)倒計時的起始值可以設置。(3)具有暫停和清零按鈕,倒計時結束報警。(4)供電電壓3.3V/5V。獲取該

2021-11-11 08:51:16

嗨......我有2個定制FPGA板。主FPGA具有100MHz的osc,用作參考時鐘。這將進入主FPGA芯片上的DCM,用于所有時鐘操作。相同的時鐘被緩沖并從主板驅動出來并發送到類似的FPGA板

2019-03-15 07:17:33

嗨,復位網是否有任何gobal路由資源,因為復位類似于時鐘,它有很多負載到每個FF和很多扇出。我們怎樣才能在合理的偏斜范圍內重置每個FF。 例如在7系列FPGA中謝謝。

2020-08-27 11:45:19

請哪位大俠幫幫忙:利用89C51設計一個時鐘控制系統設計,要求:1、采用LED數碼管顯示時鐘分、秒的計時和靜態顯示;2、采用串口工作方式0對4位共陽數碼管進行時鐘分、秒的計時。。。。。偶是新手,請給位幫幫忙,給個方案,偶先在這里謝過了。。。。。

2011-04-07 20:09:10

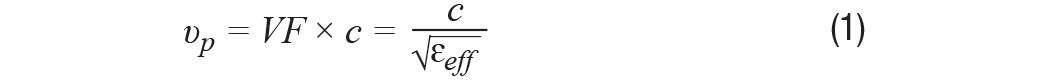

上升/下降沿也包含大量的奇次諧波,其在更高頻率時會引起 EMI。另外,時鐘通常會在板上傳播一段較長的距離,從而更可能給其他組件帶來干擾。通常,EMI 可通過頻譜分析儀測量,如圖 1 所示。圖中,綠色信號存在一些超出紅色 FCC 屏蔽的頻率分量(300MHz…

2022-11-23 06:43:42

`請幫忙分析一下,干擾源及解決方法,不勝感激!`

2015-11-30 22:46:29

在電磁電路中的電磁兼容性很大范圍是由線路貯藏和互相連接的成分決定的。有從天線返回的相應信號列是能放射出電磁能量的,其最主要是由于電流幅值,頻率和電流線圈的幾何面積決定的。通常,有三個主要的電磁干擾

2012-04-18 10:36:30

(FloorPlan)布局規劃就是放置芯片的宏單元模塊,在總體上確定各種功能電路的擺放位置,如IP模塊,RAM,I/O引腳等等。布局規劃能直接影響芯片最終的面積。工具為Synopsys的Astro

2020-02-12 16:07:15

時鐘偏斜是什么?偏斜是由哪些因素造成的?如何去使用Astro工具,有哪些流程?

2021-04-12 06:50:56

嗨,大家好! 我遇到了一個問題,希望能幫助我。當我使用chipcope分析我的設計時,我發現全局差分時鐘引腳與chipcope端口沒有連接,因為它沒有端口與芯片內的差分時鐘引腳相連,但它

2020-06-12 14:22:16

時鐘電路的電磁波干擾

所有會產生電壓頻率信號的電子組件都是潛在的電磁波干擾-Electro-Magnetic Interference, EMI-的來源這些電磁波信號將會影響如收音機電視或行

2010-03-18 10:35:42 29

29 防欺騙抗干擾同步時鐘時間服務器防欺騙抗干擾同步時鐘是針對當下北斗/GPS民用信號易受到干擾、攻擊以及欺騙等特點,導致無法正常授時、定位而開發的衛星信號安全隔離產品。適用于電力、運營商、軌道交通、安防

2024-01-02 15:52:20

摘要:本文通過介紹只有雙時鐘的單片機系統,在多個事件需要分別定時或延時的時候,解決一個時鐘完成多個計時延時的有效方法,通過這種方法可以達到對多個被控事件統一自

2006-03-11 12:38:48 471

471

AT89C51組成的時鐘電路原理圖

我們以一個實際的時鐘電路來說明定時器的軟件編程方法,時鐘就是我們最為常見的顯示時、分、秒為單位的計時工具

2010-03-06 10:10:13 4044

4044

ASIC,ASIC是什么意思

ASIC(Application Specific Integrated Circuits)即專用集成電路,是指應特定用戶要求和特定電子系統的需要而設計、制造

2010-03-26 17:10:27 7379

7379 芯片的偏斜原因有哪些?

一、問題 在電子工業的許多領域,都將倒裝芯片結合到新產品中,呈現增長的規律。因此,

2010-03-27 17:08:57 1558

1558 時鐘計時器元件清單時鐘計時器元件清單時鐘計時器元件清單時鐘計時器元件清單時鐘計時器元件清單

2015-11-18 17:07:37 28

28 簡易數字時鐘計時器DIY制作,有protues仿真和源程序 。可以看看

2015-11-20 16:45:52 82

82 基于MATLAB的系統分析與設計時頻分析。

2016-01-15 16:06:18 16

16 本文結合NCverilog,DesignCompile,Astro等ASIC設計所用到的EDA軟件,從工藝獨立性、系統的穩定性、復雜性的角度對比各種ASIC的設計方法,介紹了在編碼設計、綜合設計、靜態時序分析和時序仿真等階段經常忽視的問題以及避免的辦法,從而使得整個設計具有可控性。

2016-11-29 01:04:11 5074

5074

時鐘與計時的基本原理

2017-10-25 08:52:33 18

18 LUCT是什么? 第一層時鐘樹和第二層時鐘樹 時鐘樹設計及其設計方式是引起系統芯片性能差異的主要原因。 從歷史角度看,ASIC時鐘樹設計人員利用商用自動化工具設計時鐘樹,以確保執行時間等性能取得預期

2018-02-10 04:45:00 7477

7477

當時鐘開始計時,它將運行并且繼續計秒直到它停止。當讓它開始計時的程序停止的時候,時鐘繼續運行。但是,你想要計時的事件可能不再有效。例如,如果程序測量輸入的等待時間,當程序停止的時候,輸入已經被接收。在這種情況下,當程序停止的時候,程序將不能“看到”事件的發生。

2018-04-03 15:45:41 10095

10095 AN-0983:零延遲時鐘計時技術介紹

2018-04-23 10:58:22 0

0 本文主要介紹了時鐘計時器設計與制作.

2018-06-26 08:00:00 42

42 在低于40納米的超深亞微米VLSI設計中,時鐘樹網絡在電路時序收斂、功耗、PVT變異容差和串擾噪聲規避方面所起的作用要更重要得多。高性能DSP芯片會有大量關鍵時序路徑,會要求時鐘偏斜超低的全局時鐘

2018-10-02 13:53:34 4476

4476

了解新的UltraScale ASIC時鐘架構:如何使用它,它帶來的好處以及從現有設計遷移的容易程度。

另請參閱如何使用時鐘向導配置時鐘網絡。

2018-11-29 06:40:00 3390

3390 系統采用AT89C51單片機,以匯編語言為基礎,目的是設計一個可以用四位的數碼顯示管能夠顯示時、分的電子時鐘,電子時鐘是基于單片機的一種計時工具,單片機通過延時中斷產生一定的時間中斷,用秒的定義,通過計數滿60秒進一,滿60分進一,滿24小時清零。從而達到計時的目的,是人們生活的必要工具。

2019-01-17 08:00:00 16

16 TimeQuest Timing Analyzer是一個功能強大的,ASIC-style的時序分析工具。采用工業標準--SDC(synopsys design contraints)--的約束、分析和報告方法來驗證你的設計是否滿足時序設計的要求。

2019-11-28 07:09:00 1753

1753 本文首先介紹了asic的概念,其次介紹了ASIC的特點,最后介紹了ASIC設計過程。

2020-04-23 10:53:45 7603

7603 不大,因為它們只針對幾種信號,可能只能在一條通道上測量問題的影響。頻譜分析儀是工程師非常信賴的工具,用以測量和識別干擾源。市場上有許多不同類型的頻譜分析儀,但許多人首選電池供電的小型頻譜分析儀,因為他們需

2020-10-22 10:41:00 0

0 本文主要就對如何降低時鐘(干擾源)的干擾進行了分析和總結,因此可以得出以下如何切斷時鐘干擾的傳播途徑的結論。

2020-09-02 16:11:09 5433

5433

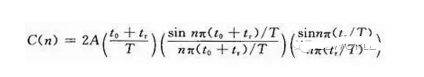

的影響;但是對于10Gbps的信號,1個時鐘周期為100ps,50ps的隨機抖動對系統的影響是致命的。另一方面,速率提升使得通道的損耗變大,碼間干擾會變得更加嚴重。這篇文章主要針對碼間干擾的產生以及如何消除碼間干擾進行分析。 碼間干擾,又稱ISI(

2020-09-11 14:58:19 23309

23309 在 PCB 設計中,您希望時鐘信號迅速到達其集成電路( IC )的目的地。但是,一種稱為時鐘偏斜的現象會導致時鐘信號早晚到達某些 IC 。當然,這會導致各個 IC 的數據完整性不一致。 什么是時鐘

2020-09-16 22:59:02 1938

1938 去年 3 月份,一款支持 5G 的全鍵盤手機 Astro Slide 在 Indiegogo 平臺眾籌成功,卻由于疫情影響遲遲沒有發貨。1 月 15 日,據外媒 XDA 報道,Astro Slide 將于 2021 年 6 月正式發貨,并將于 9 月開放購買。

2021-01-20 16:20:02 1869

1869 時鐘和計時IC評估套件-用戶手冊

2021-04-23 18:00:28 19

19 5G NR 架構要求將 PTP 用作主計時協議來為射頻單元(Radio Unit,RU)提供計時服務(請參見 5G ChangesNetwork Timing Architectures)。從運營商

2021-05-12 16:34:02 6

6 時鐘設計方案在復雜的FPGA設計中,設計時鐘方案是一項具有挑戰性的任務。設計者需要很好地掌握目標器件所能提供的時鐘資源及它們的限制,需要了解不同設計技術之間的權衡,并且需要很好地掌握一系列設計實踐

2021-06-17 16:34:51 1528

1528

門控時鐘的設計初衷是實現FPGA的低功耗設計,本文從什么是門控時鐘、門控時鐘實現低功耗的原理、推薦的FPGA門控時鐘實現這三個角度來分析門控時鐘。 一、什么是門控時鐘 門控時鐘技術(gating

2021-09-23 16:44:47 12192

12192

1)設計任務:完成倒計時時鐘的設計。2)指標要求(1)能夠分鐘級的倒計時,分鐘和秒顯示。(2)倒計時的起始值可以設置。(3)具有暫停和清零按鈕,倒計時結束報警。(4)供電電壓3.3V/5V。獲取

2021-11-06 11:51:05 38

38 CDC(不同時鐘之間傳數據)問題是ASIC/FPGA設計中最頭疼的問題。CDC本身又分為同步時鐘域和異步時鐘域。這里要注意,同步時鐘域是指時鐘頻率和相位具有一定關系的時鐘域,并非一定只有頻率和相位相同的時鐘才是同步時鐘域。異步時鐘域的兩個時鐘則沒有任何關系。這里假設數據由clk1傳向clk2。

2022-05-12 15:29:59 1334

1334 電子發燒友網站提供《使用FPGA的數字時鐘(計時表).zip》資料免費下載

2022-11-23 10:38:36 5

5 ASIC 和FPGA芯片的內核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 686

686

AN3988 基于STM32F4的時鐘配置工具

2022-11-24 08:32:13 0

0 電子發燒友網站提供《復古1980年代LED時鐘/倒數計時器.zip》資料免費下載

2022-12-13 10:03:30 0

0 所有時鐘信號的偏斜小于1 ps。其中一些應用包括相控陣、MIMO、雷達、電子戰 (EW)、毫米波成像、微波成像、儀器儀表和軟件定義無線電 (SDR)。

2022-12-22 15:19:31 628

628

時鐘使能電路是同步設計的基本電路,在很多設計中,雖然內部不同模塊的處理速度不同,但由于這些時鐘是同源的,可以將它們轉化為單一時鐘處理;在ASIC中可以通過STA約束讓分頻始終和源時鐘同相

2023-01-05 14:00:07 949

949 LVDS解串器的偏斜裕量是其抖動容限的指標。應用筆記3821:4通道(3個數據通道加時鐘通道)LVDS串行器/解串器的偏斜裕量測量展示了一種利用串行器和LVDS互連來測量偏斜裕量的方法。本應用筆記描述了如何僅使用解串器測量偏斜裕量。概述的過程幾乎可用于任何LVDS解串器。

2023-01-10 09:20:05 583

583

通過了解同步電路、時鐘傳輸和時鐘分配網絡,了解時鐘偏斜、它是什么及其對現代系統的影響。 現代數字電子產品設計的最大挑戰之一是滿足時序限制的能力。保持可預測且組織良好的邏輯操作流的一種方法是在數

2023-01-27 10:05:00 2273

2273

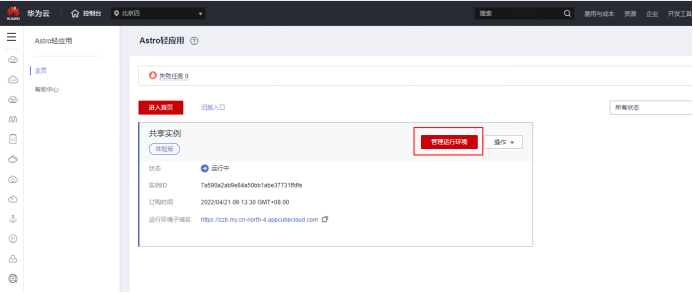

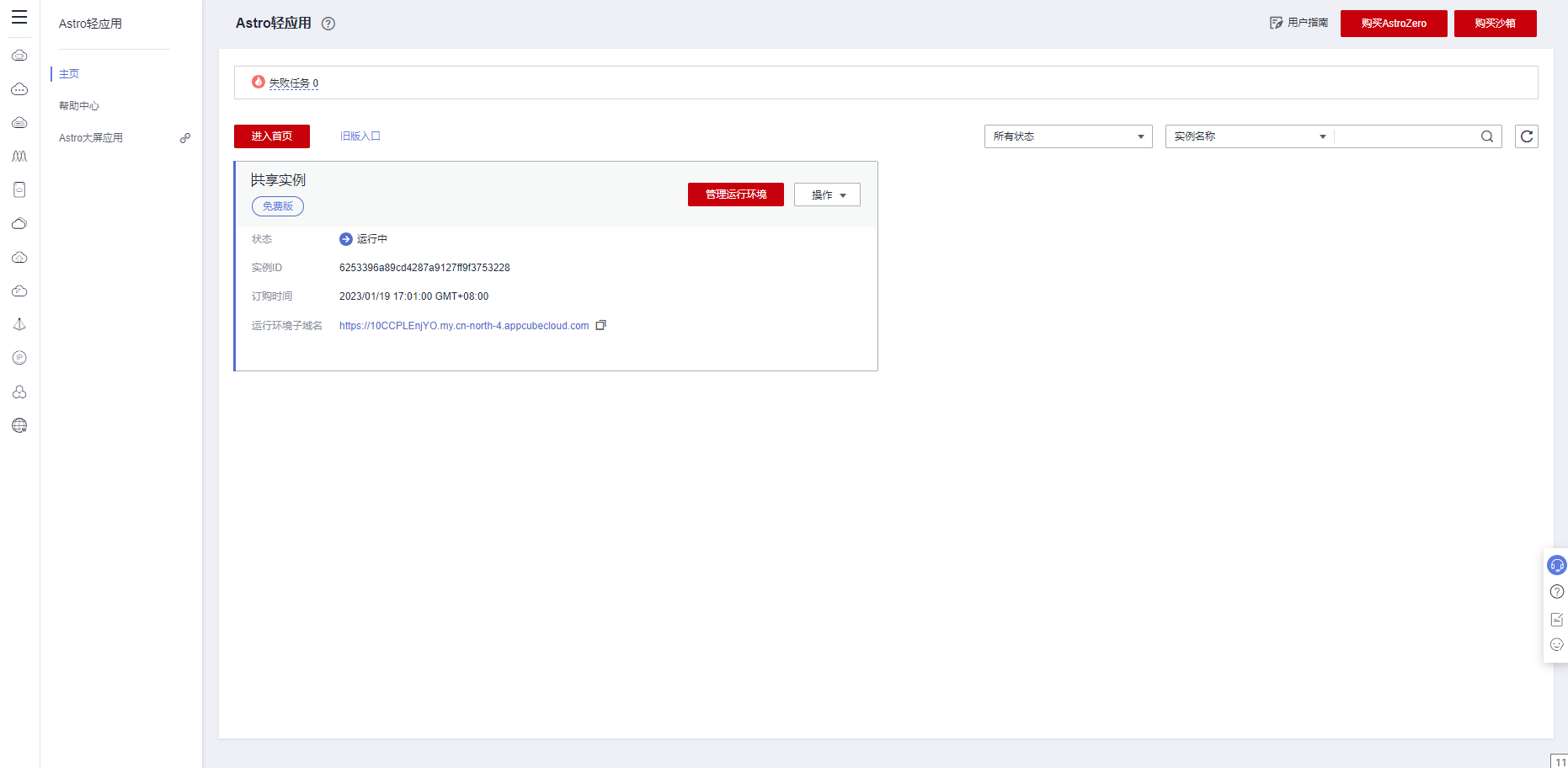

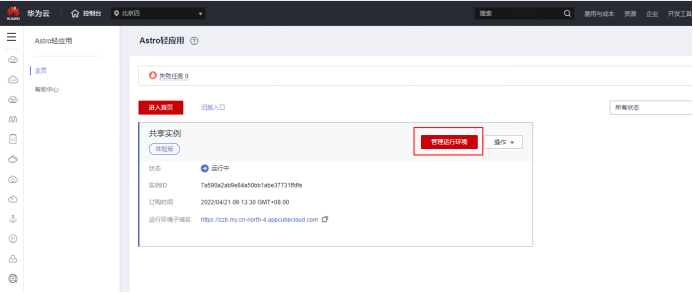

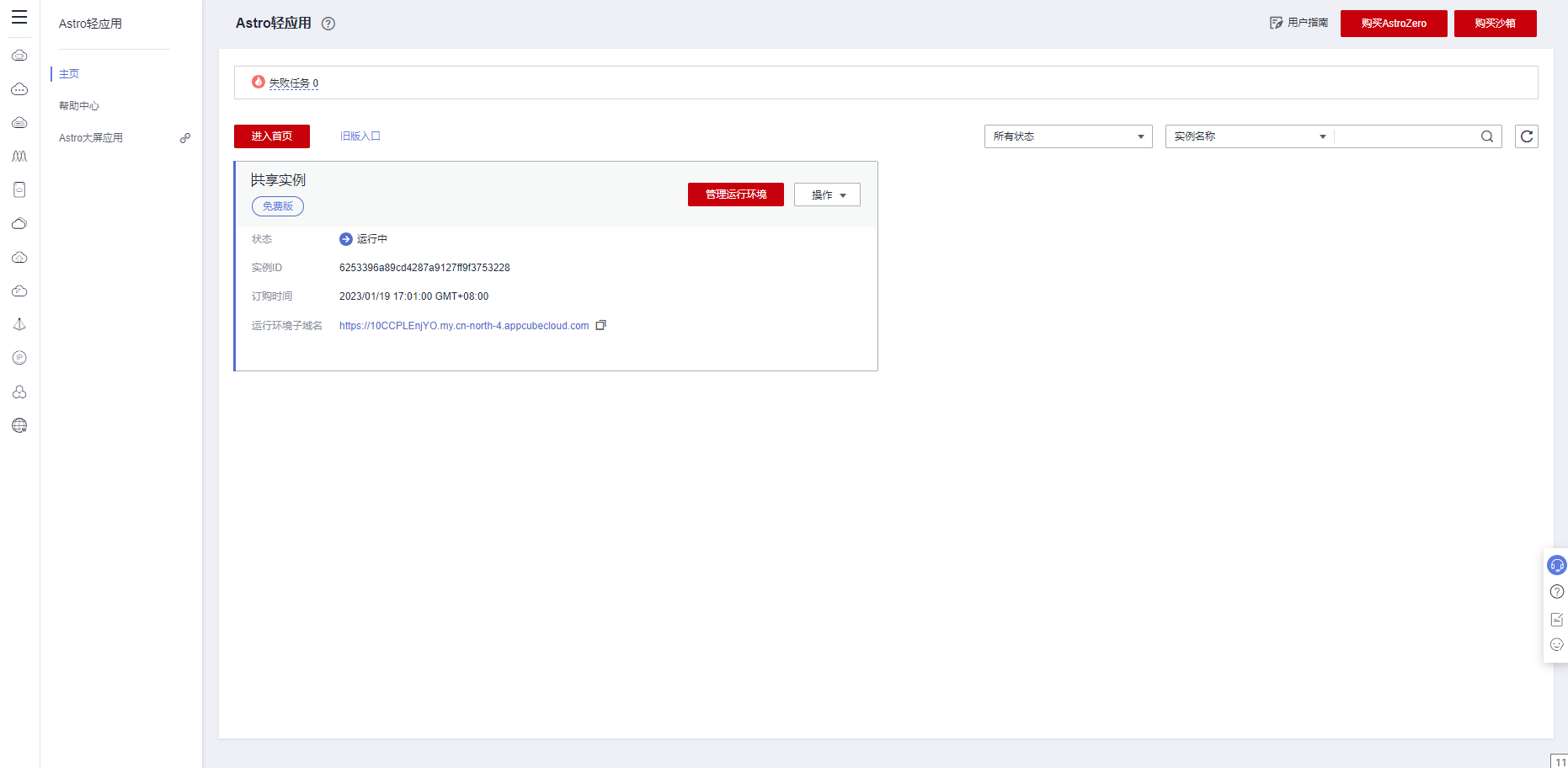

如何基于Astro零代碼能力,DIY開發,完成問卷、投票、信息收集、流程處理等工作,還能夠在線篩選、分析數據。實現一站式快速開發個性化應用,體驗輕松拖拽開發的樂趣。 環境準備 注冊華為云賬號、實名

2023-03-24 20:31:56 393

393

系統時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1637

1637 電子發燒友網站提供《健身房倒計時的時鐘開源設計.zip》資料免費下載

2023-06-19 15:09:45 0

0 電子發燒友網站提供《為新年倒計時制作的實時時鐘.zip》資料免費下載

2023-06-19 10:19:53 0

0 時鐘是每個 FPGA 設計的核心。如果我們正確地設計時鐘架構、沒有 CDC 問題并正確進行約束設計,就可以減少與工具斗爭的時間。

2023-07-05 09:05:28 647

647

時鐘是每個 FPGA 設計的核心。如果我們正確地設計時鐘架構、沒有 CDC 問題并正確進行約束設計,就可以減少與工具斗爭的時間。

2023-07-12 11:17:42 794

794

收藏這份實用又有趣的新手指南,零基礎踏上華為云低代碼開發的奇妙旅程。 第Ⅱ章?Astro 輕應用奇遇——用鼠標「拖拽」的開發 不被編程所困,像玩拼圖一樣打造訂購系統! 今天,我們用鼠標拖拽的方式開發

2023-08-25 15:58:18 192

192

收藏這份實用又有趣的新手指南,零基礎踏上華為云低代碼開發的奇妙旅程。 第Ⅰ章?旅程的開端?發現 Astro 輕應用地圖 第 1 站:創建賬戶 首先,你需要在華為云Astro官網注冊專屬賬號。若已有

2023-08-25 15:58:53 329

329

據稱 Astro 3.0 是首款支持 View Transitions API 的主流 Web 框架。基于該特性,開發者可以在頁面導航中輕松實現淡入淡出、滑動、變形,甚至持久化有狀態元素。此前只有

2023-09-01 15:15:29 414

414

終日專注「敲代碼」的三位華為云 Astro 平臺開發者,7 月 9 日,在華為開發者大會 2023 極客挑戰賽上,給學員們開上了「小灶」。 當多數人仍糾結用哪種編程語言呈現數據時,管玥已利用華為

2023-09-05 22:47:47 665

665

SYNWIT MCU 時鐘計算應用工具

2023-10-17 15:20:55 237

237

摘要:本文主要探討華為云 Astro Canvas 在數據可視化大屏開發中的應用及效果。首先闡述 Astro Canvas 的基本概念、功能和特性說明,接著集中分析展示其在教育、金融、交通

2023-11-12 17:52:17 452

452

電子發燒友網站提供《Astro II的中文手冊.pdf》資料免費下載

2023-11-16 09:32:01 0

0

電子發燒友App

電子發燒友App

評論