ADSP——美國模擬器件公司(ADI : Analog Device Instrument)生產(chǎn)的數(shù)字信號處理芯片(DSP:Digital Singal Processor),代表系列有 ADSP Sharc 211xx (低端領(lǐng)域),ADSP TigerSharc 101,201(高端領(lǐng)域),ADSP Blackfin 系列(消費電子領(lǐng)域)。

ADSP與另外一個著名的德州儀器(TI: Texas Instrument)生產(chǎn)的芯片特點相比較,具有浮點運算強,SIMD(單指令多數(shù)據(jù))編程的優(yōu)勢, 比較新的Blackfin系列比同一級別TI產(chǎn)品功耗低。缺點是ADSP不如TI的C語言編譯優(yōu)化好.TI已經(jīng)普及了C語言的編程,而AD芯片的性能發(fā)揮比較依賴程序員的編程水平.ADSP的Linkport數(shù)據(jù)傳輸能力強是一大特色,但是使用起來不夠穩(wěn)定,調(diào)試難度大。

ADI提供的Visual DSP ++2.0, 3.0, 4.0, 4.5 編程環(huán)境,可以支持軟件人員開發(fā)調(diào)試。下面是電子發(fā)燒友網(wǎng)編輯推薦的幾個關(guān)于ADSP系列芯片的一些典型應(yīng)用。

一、一種基于ADSP-2188M的多傳感器數(shù)據(jù)采集系統(tǒng)

摘 要: 在移動智能體的研制中,能夠?qū)崟r地探測周圍環(huán)境信息的傳感器系統(tǒng)是至關(guān)重要的。本文介紹了一種以DSP-ADSP-2188M為核心的傳感器數(shù)據(jù)采集系統(tǒng)的軟、硬件設(shè)計和工作原理,以及與上位機通信的設(shè)計和實現(xiàn)過程。該系統(tǒng)可以應(yīng)用于移動機器人、智能輪椅、自動制導(dǎo)車輛等移動智能系統(tǒng)中。

引言

在自主移動機器人系統(tǒng)、智能輪椅、自動制導(dǎo)車輛等智能移動系統(tǒng)中,需要實時地采集未知和不確定環(huán)境中的信息,以完成避障、環(huán)境地圖繪制、導(dǎo)航、定位等運作,然后進(jìn)行路徑規(guī)劃等任務(wù)。這些任務(wù)必須依靠能實時感知環(huán)境信息的傳感器系統(tǒng)來完成。為了在復(fù)雜環(huán)境中獲取有效的信息,這些系統(tǒng)往往安裝有種類各異的傳感器。目前,常用的有視覺、激光、紅外、超聲等傳感器。激光傳感器價格昂貴,而且在室內(nèi)的結(jié)構(gòu)化環(huán)境中存在鏡面反射的問題。同時,超聲波傳感器以其性價比高,硬件實現(xiàn)簡單等優(yōu)點,被廣泛地應(yīng)用到感知系統(tǒng)中。同時,超聲傳感器也面臨鏡面反射的問題,方向性上也有欠缺。所以,在眾多傳感器采集系統(tǒng)中還實現(xiàn)了紅外傳感器和相位敏感器件(PSD)的數(shù)據(jù)采集。

隨著微電子技術(shù)和計算機集成芯片制造技術(shù)的不斷發(fā)展和成熟,數(shù)字信號處理芯片(DSP)由于其快速的計算能力,不僅廣泛應(yīng)用于通信與視頻信號處理,也逐漸應(yīng)用在各種高級的控制系統(tǒng)中。AD公司的ADSP-21xx系列提供了低成本、低功耗、高性能的處理能力和解決方案。其中的ADSP-2188M指令執(zhí)行速度高達(dá)75MIPS,加上獨立的算術(shù)邏輯單元,擁有強大的數(shù)字信號處理能力。此外,大容量的RAM被集成到該芯片內(nèi),以形成真正的單芯片控制器,可以極大地簡化外圍電路設(shè)計,降低系統(tǒng)成本和系統(tǒng)復(fù)雜度,也大大提高了數(shù)據(jù)的存儲處理能力。我們設(shè)計的多傳感器數(shù)據(jù)采集系統(tǒng)以ADSP-2188M為核心控制器。本文著重介紹該系統(tǒng)的軟、硬件設(shè)計和工作原理,并給出實驗結(jié)果。

圖1? 多傳感器數(shù)據(jù)采集系統(tǒng)方框圖

?

圖2? 超聲波接收電路

圖3 系統(tǒng)軟件流程圖

系統(tǒng)的硬件設(shè)計

整個多傳感器數(shù)據(jù)采集系統(tǒng)的結(jié)構(gòu)如圖1所示。從圖中可以看出,系統(tǒng)由DSP主控制器、超聲波環(huán)境探測電路、紅外傳感器數(shù)據(jù)采集電路、PSD數(shù)據(jù)采集電路和通信模塊等部分組成。系統(tǒng)的核心為ADSP 2188M,主要完成對各種傳感器的控制,信號的發(fā)射與接收,信息的融合及與上位PC主機進(jìn)行通訊等功能。由于系統(tǒng)對傳感器的信息已經(jīng)進(jìn)行了集中的預(yù)處理,與PC上位機進(jìn)行通信的數(shù)據(jù)量將得到很大的降低,RS232串口通信方式已經(jīng)能夠滿足系統(tǒng)在實時性方面的要求。

超聲波環(huán)境探測電路

超聲波探測電路主要由16路超聲波發(fā)生電路和超聲波接收電路等模塊組成。移動智能系統(tǒng)在運動過程中需要實時地了解環(huán)境信息,常常根據(jù)實際需要將超聲傳感器均勻地布置在系統(tǒng)四周,從而構(gòu)成環(huán)境探測系統(tǒng)。超聲測距的原理較簡單,一般采用渡越時間法,即:

D=Ct / 2 (1)

其中D為移動機器人與被測障礙物之間的距離,C為聲波在介質(zhì)中的傳輸速率,t為渡越時間,聲波在空氣中傳輸速率為:

(2)

其中,T為絕對溫度。在不要求測距精度很高的情況下,一般可以認(rèn)為C為常數(shù)。測量超聲波從發(fā)射到返回的時間間隔t,然后根據(jù)式(1)計算距離。

超聲波發(fā)射部分主要由激勵信號發(fā)生電路,緩沖升壓放大和超聲波換能器等環(huán)節(jié)構(gòu)成。超聲波發(fā)射過程是:首先由DSP控制多路模擬開關(guān)ADG438F,選擇性地啟動16路發(fā)射電路中的4路。然后由ADSP2188M的一個I/O口產(chǎn)生脈寬為25μs的40kHz的調(diào)制脈沖波,通過緩沖放大器7406,再經(jīng)變壓器升壓放大電路產(chǎn)生幅度達(dá)60V的瞬間高能激勵信號,同時激發(fā)4路超聲換能器產(chǎn)生超聲波信號。ADG438F的最大開啟時間為250ns,不會影響系統(tǒng)的實時性。

超聲波的接收與發(fā)射必須協(xié)調(diào)一致工作,才能保證信號準(zhǔn)確靈敏的接收。接收部分主要由接收換能器、放大濾波、整形觸發(fā)輸出等環(huán)節(jié)組成,如圖2所示。由于超聲波在傳播中,其能量會隨傳輸距離的增大而減小,從遠(yuǎn)距離障礙物反射的回波信號一般比較弱(為mv級),所以需要經(jīng)過多級信號放大處理。本系統(tǒng)采用了三級放大處理,將信號放大約150萬倍,然后經(jīng)整形電路輸出。4路超聲傳感器接收電路將經(jīng)過整形以后的信號作為中斷申請信號,通過多路模擬開關(guān)再接入ADSP-2188M的外部中斷引腳,觸發(fā)DSP的外部中斷。

實驗測得該超聲傳感器的靈敏范圍大約為30度,測距范圍為0.30~3m,重復(fù)測距精度在1%以內(nèi)。

紅外傳感器數(shù)據(jù)采集電路

紅外傳感器數(shù)據(jù)采集模塊主要由8路紅外傳感器、光電隔離電路和電子開關(guān)組成。紅外傳感器的探測距離一般比較短,通常被用作近距離障礙目標(biāo)的識別,可以在一定程度上彌補超聲傳感器盲區(qū)特性的不足。其輸出為0或1的開關(guān)量。紅外傳感器一般在靜態(tài)時工作電流為25mA左右,而在動態(tài)工作時可達(dá)60mA。因而,紅外傳感器陣列的使用將會對系統(tǒng)的供電系統(tǒng)帶來很大的負(fù)擔(dān)。為此,在紅外傳感器數(shù)據(jù)采集模塊中引入三極管的電子開關(guān),控制紅外傳感器的供電電源,當(dāng)需要采集紅外傳感器信息時,才接通紅外傳感器的電源。經(jīng)過實驗測定,該電子開關(guān)的反應(yīng)速度達(dá)到5.6μs,對系統(tǒng)的實時性幾乎沒有影響。

8路紅外傳感器的數(shù)據(jù)通過光電耦合電路直接連接到ADSP2188M的高8位數(shù)據(jù)線上,實現(xiàn)并行采集。

PSD數(shù)據(jù)采集電路

PSD數(shù)據(jù)采集電路由4個PSD傳感器組成,用于目標(biāo)距離的檢測。它的工作原理就是通過測量發(fā)射和反射紅外光之間的相位差來測量反射物體的距離,被測物體的顏色也不會影響其測距精度。PSD可以彌補超聲傳感器方向性差,測量響應(yīng)時間較長等缺點。我們使用的是Sharp公司的GP2Y0A02YK紅外測距器件。該器件能夠把相位差的變化轉(zhuǎn)化為輸出電壓的變化,可以連續(xù)的讀出距離。測量范圍為20~150cm,輸出電壓范圍0~2.7V。

系統(tǒng)的軟件描述

系統(tǒng)軟件主要由主循環(huán)模塊、超聲回波中斷接收模塊、通訊模塊等組成。具體流程圖如圖3所示。

隙鍆獾氖奔淅醋槌擅で?郵薄Q郵幣院缶涂梢鑰?敉獠恐卸希?⒀?返卻?超聲回波信號。最后,不管有沒有接收到回波,應(yīng)該進(jìn)行適當(dāng)?shù)难訒r,避免在室內(nèi)工作環(huán)境下超聲波的余波效應(yīng)。

實驗結(jié)果

首先,我們對多傳感器數(shù)據(jù)采集系統(tǒng)中的超聲傳感器和PSD的測距性能進(jìn)行了測試:讓該系統(tǒng)的不同傳感器對同一個目標(biāo)進(jìn)行測距,超聲傳感器的實際結(jié)果如表1所示。試驗證明兩種傳感器的重復(fù)測量精度均在1%之內(nèi),兩者之間的誤差也不超過2%,精度完全能夠滿足一般移動智能系統(tǒng)的要求。

同時,為了驗證整個多傳感器數(shù)據(jù)采集系統(tǒng)的實時性,我們計算了系統(tǒng)的主循環(huán)模塊在最差條件下(即所有的超聲傳感器都沒有探測到回波信號),所用的時間約為35.33ms。也就是說,系統(tǒng)數(shù)據(jù)的更新頻率能夠達(dá)到30Hz左右,證明系統(tǒng)有良好的實時性。

結(jié)語

本文研究了一種高性能、低成本、低功耗多傳感器數(shù)據(jù)采集系統(tǒng)的硬、軟件實現(xiàn)和工作原理。系統(tǒng)以高性能的數(shù)字信號處理器ADSP2188M為核心處理器,集中實現(xiàn)多個紅外、超聲和PSD傳感器數(shù)據(jù)的采集和傳輸。實驗驗證了硬件系統(tǒng)的可靠性、實時性和算法的有效性。

二、基于ADSP-21160的液晶驅(qū)動電路設(shè)計及系統(tǒng)軟件實現(xiàn)

薄膜晶體管液晶顯示器(TFT-LCD)具有重量輕、平板化、低功耗、無輻射、顯示品質(zhì)優(yōu)良等特點,其應(yīng)用領(lǐng)域正在逐步擴大,已經(jīng)從音像制品、筆記本電腦等顯示器發(fā)展到臺式計算機、工程工作站(EWS)用監(jiān)視器。對液晶顯示器的要求也正在向高分辨率、高彩色化發(fā)展。

由于CRT顯示器和液晶屏具有不同的顯示特性,兩者的顯示信號參數(shù)也不同,因此在計算機(或MCU)和液晶屏之間設(shè)計液晶顯示器的驅(qū)動電路是必需的,其主要功能是通過調(diào)制輸出到LCD電極上的電位信號、峰值、頻率等參數(shù)來建立交流驅(qū)動電場。

本文實現(xiàn)了將VGA接口信號轉(zhuǎn)換到模擬液晶屏上顯示的驅(qū)動電路,采用ADI公司的高性能DSP芯片ADSP-21160來實現(xiàn)驅(qū)動電路的主要功能。

硬件電路設(shè)計

AD9883A 是高性能的三通道視頻ADC可以同時實現(xiàn)對RGB三色信號的實時采樣。系統(tǒng)采用32位浮點芯片ADSP-21160來處理數(shù)據(jù),能實 時完成伽瑪校正、時基校正、圖像優(yōu)化等處理,且滿足了系統(tǒng)的各項性能需求。ADSP-21160有6個獨立的高速8位并行鏈路口,分別連接ADSP- 21160前端的模數(shù)轉(zhuǎn)換芯片AD9883A和后端的數(shù)模轉(zhuǎn)換芯片ADV7125。ADSP-21160具有超級哈佛結(jié)構(gòu),支持單指令多操作數(shù) (SIMD)模式,采用高效的匯編語言編程能實現(xiàn)對視頻信號的實時處理,不會因為處理數(shù)據(jù)時間長而出現(xiàn)延遲。

系統(tǒng)硬件原理框圖如圖1所示。系統(tǒng)采用不同的鏈路口完成輸入和輸出,可以避免采用總線可能產(chǎn)生的通道沖突。模擬視頻信號由AD9883A完成模數(shù)轉(zhuǎn) 換。AD9883A是個三通道的ADC,因此系統(tǒng)可以完成單色的視頻信號處理,也可以完成彩色的視頻信號處理。采樣所得視頻數(shù)字信號經(jīng)鏈路口輸入到 ADSP-21160,完成處理后由不同的鏈路口輸出到ADV7125,完成數(shù)模轉(zhuǎn)換。ADV7125是三通道的DAC,同樣也可以用于處理彩色信號。輸 出視頻信號到灰度電壓產(chǎn)生電路,得到驅(qū)動液晶屏所需要的驅(qū)動電壓。ADSP-21160還有通用可編程I/O標(biāo)志腳,可用于接受外部控制信號,給系統(tǒng)及其 模塊發(fā)送控制信息,以使整個系統(tǒng)穩(wěn)定有序地工作。例如,ADSP-21160為灰度電壓產(chǎn)生電路和液晶屏提供必要的控制信號。另外,系統(tǒng)還設(shè)置了一些 LED燈,用于直觀的指示系統(tǒng)硬件及DSP內(nèi)部程序各模塊的工作狀態(tài)。

圖1 系統(tǒng)硬件原理框圖

本設(shè)計采用從閃存引導(dǎo)的方式加載DSP的程序文件,閃存具有很高的性價比,體積小,功耗低。由于本系統(tǒng)中的閃存既要存儲DSP程序,又要保存對應(yīng)于 不同的伽瑪值的查找表數(shù)據(jù)以及部分預(yù)設(shè)的顯示數(shù)據(jù),故選擇ST公司的容量較大的M29W641DL,既能保存程序代碼,又能保存必要的數(shù)據(jù)信息。

圖2為DSP與閃存的接口電路。因為采用8位閃存引導(dǎo)方式,所以ADSP-21160地址線應(yīng)使用A20~A0,數(shù)據(jù)線為D39~32,讀、寫和片選信號分別接到閃存相應(yīng)引腳上。

圖2 DSP和Flash的接口電路

系統(tǒng)功能及實現(xiàn)

本設(shè)計采用ADSP-21160完成伽瑪校正、時基校正、時鐘發(fā)生器、圖像優(yōu)化和控制信號的產(chǎn)生等功能。

伽瑪校正原理

在 LCD中,驅(qū)動IC/LSI的DAC圖像數(shù)據(jù)信號線性變化,而液晶的電光特性 是非線性,所以要調(diào)節(jié)對液晶所加的外加電壓,使其滿足液晶顯示亮度的線性,即伽瑪(γ)校正。γ校正是一個實現(xiàn)圖像能夠盡可能真 實地反映原物體或原圖像視覺信息的重要過程。利用查找表來補償液晶電光特性的γ校正方法能使液晶顯示系統(tǒng)具有理想的傳輸函數(shù)。未校正時液晶顯 示系統(tǒng)的輸入輸出曲線呈S形。伽瑪表的作用就是通過對ADC進(jìn)來的信號進(jìn)行反S形的非線性變換,最終使液晶顯示系統(tǒng)的輸入輸出曲線滿足實際要求。

LCD的γ校正圖形如圖3所示,左圖是LCD的電光特性曲線圖,右圖是LCD亮度特性曲線和電壓的模數(shù)轉(zhuǎn)換圖。

圖3 LCD的γ校正示意圖

伽瑪校正的實現(xiàn)

本文采用較科學(xué)的γ校正處理技術(shù),對數(shù)字三基色視頻信號分別進(jìn)行數(shù)字γ校正(也可以對模擬三基色視頻信號分別進(jìn)行γ校正)。在完成γ校正的同時,并不損失灰度層次,使全彩色顯示屏圖像更鮮艷,更逼真,更清晰。

某 單色光γ調(diào)整過程如圖4所示,其他二色與此相同。以單色光γ調(diào)整為例:ADSP-21160 首先根據(jù)外部提供的一組控制信號,進(jìn)行第一次查表,得到γ調(diào)整系數(shù)(γ值)。然后根據(jù)該γ值和輸入的顯示數(shù)據(jù)進(jìn)行第 二次查表,得到經(jīng)校正后的顯示數(shù)據(jù)。第一次查表的γ值是通過外部的控制信號輸入到控制模塊進(jìn)行第一次查表得到的。8位顯示數(shù)據(jù)信號可查表數(shù)字 0~255種灰度級顯示數(shù)據(jù)(γ校正后)。

圖4 單色光γ調(diào)整的過程

圖像優(yōu)化

為了提高圖像質(zhì)量,ADSP-21160內(nèi)部還設(shè)計了圖像效果優(yōu)化及特技模塊,許多 在模擬處理中無法進(jìn)行的工作可以在數(shù)字處理中進(jìn)行,例如,二維數(shù)字濾波、輪廓校正、細(xì)節(jié)補償頻率微調(diào)、準(zhǔn)確的彩色矩陣(線性矩陣電路)、黑斑校正、g校 正、孔闌校正、增益調(diào)整、黑電平控制及雜散光補償、對比度調(diào)節(jié)等,這些處理都提高了圖像質(zhì)量。

數(shù)字特技是對視頻信號本身進(jìn)行尺寸、位置變 化和亮、色信號變化的數(shù)字化處理,它能使圖像變成各種形狀,在屏幕上任意放縮、旋轉(zhuǎn)等,這些是模擬特技無法實現(xiàn)的。還可以設(shè)計濾波器來濾除一些干擾信號和 噪聲信號等,使圖像的清晰度更高,更好地再現(xiàn)原始圖像。所有的信號和數(shù)據(jù)都是存儲在DSP內(nèi)部,由它內(nèi)部產(chǎn)生的時鐘模塊和控制模塊實現(xiàn)的。

時基校正及系統(tǒng)控制

由于ADSP-21160內(nèi)部各個模塊的功能和處理時間不同,各模塊之間 存在一定延時,故需要進(jìn)行數(shù)字時基校正,使存儲器最終輸出的數(shù)據(jù)能嚴(yán)格對齊,而不會出現(xiàn)信息的重疊或不連續(xù)。數(shù)字時基校正主要用于校正視頻信號中的行、場 同步信號的時基誤差。首先,將被校正的信號以它的時基信號為基準(zhǔn)寫入存儲器,然后,以TFT-LCD的時基信號為基準(zhǔn)讀出,即可得到時基誤差較小的視頻信 號。同時它還附加了其他功能,可以對視頻信號的色度、亮度、飽和度進(jìn)行調(diào)節(jié),同時對行、場相位、負(fù)載波相位進(jìn)行調(diào)節(jié),并具有時鐘臺標(biāo)的功能。

控 制模塊主要負(fù)責(zé)控制時序驅(qū)動邏輯電路以管理和操作各功能模塊,如顯示數(shù)據(jù)存儲器的管理和操作,負(fù)責(zé)將顯示數(shù)據(jù)和指令參數(shù)傳輸?shù)轿唬?fù)責(zé)將參數(shù)寄存器的內(nèi)容 轉(zhuǎn)換成相應(yīng)的顯示功能邏輯。內(nèi)部的信號發(fā)生器產(chǎn)生控制信號及地址,根據(jù)水平和垂直顯示及消隱計數(shù)器的值產(chǎn)生控制信號。此外,它還可以接收外部控制信號,以 實現(xiàn)人機交互,從而使該電路的功能更加強大,更加靈活。

此外,ADSP21160的內(nèi)部還設(shè)計了I2C總線控制模塊,模擬I2C總線的工作,為外部的具有I2C接口的器件提供SCLK(串行時鐘信號)和SDA(雙向串行數(shù)據(jù)信號)。模擬I2C工作狀態(tài)如圖5和圖6所示。

圖5 串行端口讀/寫時序

圖6串行接口-典型的字節(jié)傳送

系統(tǒng)軟件實現(xiàn)

在軟件設(shè)計如圖7所示,采用Matlab軟件計算出校正值,并以查找表的文件形式存儲,供時序的調(diào)用。系統(tǒng)上電開始,首先要完成ADSP- 21160的一系列寄存器的設(shè)置,以使DSP能正確有效地工作。當(dāng)ADSP-21160接收到有效的視頻信號以后,根據(jù)外部控制信息確定γ 值。為適應(yīng)不同TFT-LCD屏對視頻信號的顯示,系統(tǒng)可以通過調(diào)整γ值,以調(diào)節(jié)顯示效果到最佳。再如圖4所示,對先前預(yù)存的文件進(jìn)行查表, 得到所需的矯正后的值,然后暫存等待下一步處理。系統(tǒng)還可以根據(jù)視頻信號特點和用戶需要完成一些圖像的優(yōu)化和特技,如二維數(shù)字濾波、輪廓校正、增益調(diào)整、 對比度調(diào)節(jié)等。這些操作可由用戶需求選擇性使用。利用ADSP-21160還可以實現(xiàn)圖像翻轉(zhuǎn)、停滯等特技。最后進(jìn)行數(shù)字時基校正,主要用于校正視頻信號 中的行、場同步信號的時基誤差,使存儲器最終輸出的數(shù)據(jù)能嚴(yán)格對齊,而不會出現(xiàn)信息的重疊或不連續(xù)。除了以上所述的主要功能以外,ADSP-21160還 根據(jù)時序控制信號,為灰度電壓產(chǎn)生電路和TFT-LCD屏提供必要的控制信號。另外,ADSP-21160還能設(shè)置驅(qū)動通用I/O腳配置的LED燈,顯示 系統(tǒng)工作狀態(tài)。

圖7 軟件流程圖

結(jié)束語

本文介紹了基于ADSP-21160的液晶驅(qū)動電路設(shè)計。該驅(qū)動電路能完成伽馬校正、圖像優(yōu)化及時基校正等功能,并能提供具有足夠驅(qū)動能力的時序和 邏輯控制信號,能驅(qū)動大部分的TFT-LCD。用ADSP-21160設(shè)計驅(qū)動電路實時性好、通用性強、速度快且高效;而且還能在ADSP-21160中 嵌入其他功能模塊控制,增強系統(tǒng)的功能。這樣不僅充分利用了ADSP-21160資源,又節(jié)省了外部資源,簡化了硬件電路的設(shè)計。作者將SONY的 LCX029CPT顯示屏應(yīng)用在本文所設(shè)計的驅(qū)動電路上,顯示出質(zhì)量很高的圖像,因此該設(shè)計滿足驅(qū)動液晶顯示器的要求。

三、基于CY7C68013A和FPGA的ADSP-TS101擴展USB接口設(shè)計

ADI公司的DSP器件(ADSP-TS101)具有浮點實時處理能力強、并行性好等優(yōu)點,從而廣泛被彈載信號處理系統(tǒng)選用。其作為彈載主處理器,在導(dǎo)彈的系統(tǒng)試驗中,需要利用上位機對其中的大數(shù)據(jù)量的軟件變量進(jìn)行實時監(jiān)控和記錄,這就需要一個上行傳輸給上位機的高速通信接口,數(shù)據(jù)上行的數(shù)據(jù)率需要大于6 MB/s。同時這個通信接口還需具有雙向特性,通過數(shù)據(jù)下行可實現(xiàn)在線程序加載與燒寫。這樣的通信接口,還需具備設(shè)備連接簡單、通用性強等特性,并能實現(xiàn)遠(yuǎn)程(大于3m)數(shù)據(jù)傳輸。

ADSP-TS101自身的外總線接口和鏈路口(Linkport接口),雖速度很快,但連接復(fù)雜,難以長線傳輸,并不具備上述需求特征。可以通過在DSP的Linkport總線接口上增加FPGA實現(xiàn)的適配電路,擴展USB 2.0接口,實現(xiàn)上述應(yīng)用需求。下文將介紹具體的實現(xiàn)方案。

1 系統(tǒng)總體方案

系統(tǒng)實現(xiàn)的總體方案如圖1所示。

在本方案中,USB接口芯片選用Cypress公司的CY7C68013A。該芯片是Cypress公司FX2系列USB 2.0集成微控制器之一。集成了USB 2.0收發(fā)器、SIE、增強8051微控制器和GPIF,是一種優(yōu)秀的高速USB外設(shè)控制器。內(nèi)置的8051微控制器獨立于USB數(shù)據(jù)通道,由SIE實現(xiàn)大部分USB 1.1和USB 2.0協(xié)議;USB FIFO和外部從FIFO映射到相同的8個512 B RAM模塊,實現(xiàn)內(nèi)部傳輸和外部傳輸?shù)臒o縫連接,可以較低的代價獲得較高的帶寬;8.5 KB內(nèi)部RAM空間,可運行較為復(fù)雜的固件,實現(xiàn)軟件對硬件的配置。GPIF是由用戶可編程有限狀態(tài)機驅(qū)動的柔性8/16位并行口,可編程GPIF向量組成一個GPIF波形,匹配受控接口的時序。

ADSP-TS101作為彈載主DSP芯片,含4個鏈路口,每個鏈路口可在時鐘雙沿以8位進(jìn)行雙向數(shù)據(jù)傳輸,速率高達(dá)250 MB/s。通過該接口,DSP每個處理幀將預(yù)觀測的變量結(jié)果以DMA的方式打包向上位機發(fā)送。

FPGA實現(xiàn)ADSP-TS101的Linkport接口與CY7C68013A之間的雙向數(shù)據(jù)緩沖和接口協(xié)議轉(zhuǎn)換。考慮到CY7C68013A中的 FIFO容量較DSP的一個處理幀預(yù)發(fā)送或接收的數(shù)據(jù)量較小,故在FPGA中設(shè)置上行和下行各一個大容量FIFO,用于數(shù)據(jù)緩沖,以減少對DSP中并行流水運行的程序的打擾。這里,由于DSP鏈路口的瞬時數(shù)據(jù)率遠(yuǎn)高于USB芯片的傳輸速率(理論上限為60 MB/s),故FIFO的DSP端口的數(shù)據(jù)傳輸為:一個處理幀只操作一次,而USB芯片端則分成多次操作。

限于篇幅,下文將重點對傳輸數(shù)據(jù)率要求高、設(shè)計難度大的上行通道的設(shè)計進(jìn)行詳細(xì)描述。

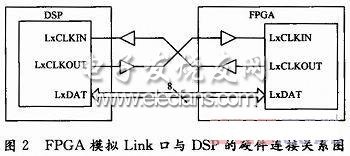

FPGA需要模擬Linkport口的接口時序,其與DSP的硬件連接關(guān)系圖如圖2所示。

Link協(xié)議通過8位并行數(shù)據(jù)總線完成雙向數(shù)據(jù)傳輸,與數(shù)據(jù)總線配合的還有相應(yīng)的時鐘信號線LxCLKIN,LxCLKOUT。

2.1 Linkport口的傳輸協(xié)議

Linkport口傳輸數(shù)據(jù)時,每8個周期傳送一個4字組(16 B),在時鐘的上升沿和下降沿均傳送一個字節(jié)。在傳送過程中,發(fā)送端將檢測接收端的LxCLKOUT信號,僅當(dāng)接收端將它的LxCLKOUT置為高時,即接收端處于接收方式,且有空閑的緩沖時,發(fā)送端才可以啟動下一個傳送過程。

傳送啟動過程如圖3所示,發(fā)送端驅(qū)動信號LxCLKOUT為低電平,以此向接收端發(fā)出令牌請求,發(fā)出令牌請求后,發(fā)送端等待6個周期,并驗證LxCLKIN是否依舊為高,若是則啟動傳送過程。傳送過程啟動一個周期以后,接收端將發(fā)送端的LxCLKIN驅(qū)動為低,以此作為連接測試。若接收完當(dāng)前4字組后接收端無法再接收另外的4字組,則接收端保持LxCLKIN為低。這種情況下,緩沖空閑后LxCLKIN信號被禁止。若緩沖為空,則接收端將置LxCLKIN為高電平。

作為同步信號,LxCLKOUT信號由發(fā)送端驅(qū)動。數(shù)據(jù)在LxCLKOUT的上升沿和下降沿處鎖存到接收緩沖中,發(fā)送和接收緩沖都是128b寬。 LxCLKIN信號由接收端驅(qū)動,發(fā)往發(fā)送端,它通常用作“等待”指示信號,但LxCLKIN信號也可以用作連接測試信號,保證接收端能正確地接收當(dāng)前傳送數(shù)據(jù)。

當(dāng)LxCLKIN信號用于等待指示信號時,接收端驅(qū)動LxCLKIN信號為低電平。若LxCLKIN信號保持低電平狀態(tài),則發(fā)送端可以[完成當(dāng)前的4字組傳送,但無法啟動下一個垂字組傳送。若還有其余的數(shù)據(jù)需要傳送,發(fā)送端需將LxCLKOUT置低,并等待接收端將 LxCLKIN驅(qū)動為高電平。如果在第12個時鐘沿到來之前LxCLKIN變?yōu)楦唠娖剑瑒t緊跟著傳送的將是新的4字組。

2.2 FPGA內(nèi)的Linkport口邏輯設(shè)計

由于Link協(xié)議采用雙時鐘沿傳輸數(shù)據(jù),而同步FPGA系統(tǒng)中,一般只采用單一時鐘的上升沿完成操作,因此需要將FPGA系統(tǒng)工作頻率SCLK設(shè)定為Link時鐘的2倍。然后將該時鐘的兩分頻輸出作為LxCLKOUT信號,有效數(shù)據(jù)則在SCLK的上升沿更新。

FPGA中的Linkport口接口模塊電路與ADSP-TS101的Linkport口完全兼容,且采用了雙向雙倍數(shù)據(jù)傳輸DDR技術(shù),能實現(xiàn)雙向雙倍的數(shù)據(jù)傳輸。FPGA中的Link口接口模塊電路如圖4所示。

圖5是FPGA內(nèi)實現(xiàn)DSP數(shù)據(jù)上行的Linkport口接收時序仿真圖(基于Modelsim仿真軟件)。

Link口協(xié)議的一大特點就是在收發(fā)數(shù)據(jù)時可以選擇是否需要校驗位VERE比特,VERE的啟用或關(guān)閉可以通過ADSP-TS101中的寄存器來設(shè)置,也可以通過FPGA模塊中的Verein信號置高或置低來設(shè)置。該設(shè)計在FPGA中設(shè)置VERE信號的啟用或關(guān)閉。當(dāng)VERE啟用后,F(xiàn)PGA模塊中的輸出信號Rx_Vere_Bad用于表征最后接收的128 b數(shù)據(jù)是否正確。由于使用VERE有兩個好處,一是能保證數(shù)據(jù)的完整性;二是能減小在兩個時鐘不嚴(yán)格一致的系統(tǒng)中傳輸數(shù)據(jù)時產(chǎn)生數(shù)據(jù)重疊的可能性。因而在設(shè)計中采用了帶數(shù)據(jù)校驗的傳輸方式。

3.1 傳輸方式的確定

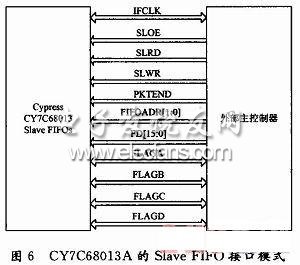

CY7C68013A芯片具有GPIF模式和從屬FIFO(Slave FIFO)模式兩種接口工作模式。在本設(shè)計中,USB數(shù)據(jù)傳輸存儲模塊負(fù)責(zé)完成存儲算法產(chǎn)生的大量數(shù)據(jù)的高速傳輸,由于不涉及到對外部電路的控制,所以不選用GPIF模式,而選擇Slave FIFO模式進(jìn)行連接。在數(shù)據(jù)傳輸時,用Slave FIFO接口模式,批量傳輸,自動輸入(AUTOIN)方式,使用EP6端口作為上行輸入緩沖區(qū)。CY7C68013A的,Slave FIFO接口模式如圖6所示。

?

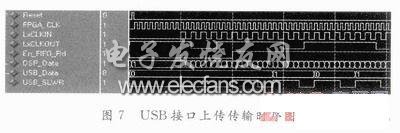

3.2 EZ-USB FX2時序設(shè)計

在本設(shè)計的FPGA中,設(shè)計了如圖6的外部主控制器的功能邏輯。由于DSP端Linkport口數(shù)據(jù)傳輸速率很高,而在USB端的速率可能無法跟 Linkport口的數(shù)據(jù)率相匹配,故在FPGA中開辟一個2KB的FIFO,經(jīng)由Linkport上傳的數(shù)據(jù)首先傳送到FIFO中,之后再經(jīng)由USB口上傳至主機。為了保證數(shù)據(jù)傳輸?shù)耐暾裕O(shè)計USB的數(shù)據(jù)傳輸速率為DSP Link口的1/8。在此,對FPGA邏輯應(yīng)用Modelsim軟件進(jìn)行了仿真,仿真結(jié)果如圖7所示。

圖7中,在LxCLKIN時鐘的上升沿和下降沿將DSP_Data中的數(shù)據(jù)寫入到FPGA的FIFO中,然后再把FIFO中的數(shù)據(jù)從數(shù)據(jù)線 USB_Data中輸出給EZ-USB FX2的FD數(shù)據(jù)線,最后經(jīng)由USB傳送給主機。圖中USB_Data的數(shù)據(jù)率明顯只有DSP_Data數(shù)據(jù)率的1/8,是符合設(shè)計要求的。

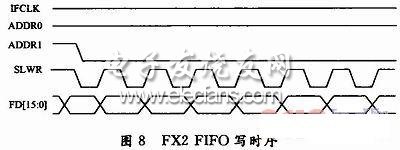

在上傳傳輸時,采用異步自動輸入方式。EZ-USB FX2芯片F(xiàn)IFO異步寫時序如圖8所示。根據(jù)此時序,在本設(shè)計中,F(xiàn)PGA輸出的USB_Data信號提供給USB的FD數(shù)據(jù)線,F(xiàn)PGA輸出的 USB_SLWR提供給USB的SLWR,USB端便能在SLWR的下降沿把數(shù)據(jù)線FD中的數(shù)據(jù)寫入到FX2芯片F(xiàn)IFO中,并由USB傳送給主機。

4 結(jié)語

本文重點對DSP擴展USB接口的數(shù)據(jù)上行通道的硬件設(shè)計進(jìn)行了詳細(xì)論述。本系統(tǒng)經(jīng)測試驗證,通過該擴展USB接口,配合定制的上位機軟件,DSP數(shù)據(jù)上傳PC機的速率平均達(dá)到8 MB/s以上,連接可靠穩(wěn)定,滿足對DSP變量實時監(jiān)測的數(shù)據(jù)率需求,同時可通過此接口完成程序的加載與燒寫功能。僅需一臺帶USB接口的PC機,就能完成彈載DSP系統(tǒng)的實時測試與在線程序加載,簡捷、通用、方便,具有顯著的工程實用價值。

四、基于SigmaDSP的車載音響噪音降低方案

?

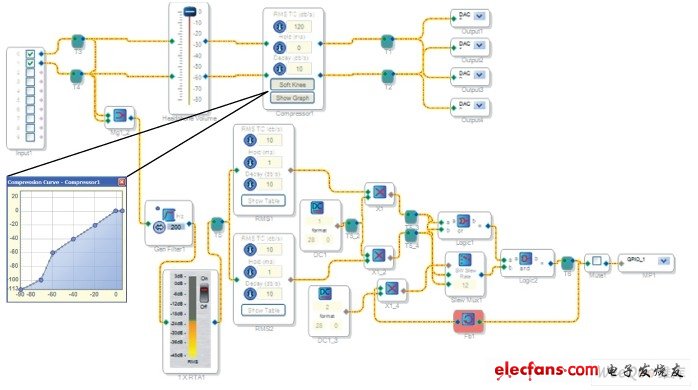

ADAU1401是一款完整的單芯片音頻系統(tǒng),包括完全可編程的28/56位音頻DSP、模數(shù)轉(zhuǎn)換器(ADC)、數(shù)模轉(zhuǎn)換器(DAC)及類似微控制器的控制接口。信號處理包括均衡、低音增強、多頻段動態(tài)處理、延遲補償、揚聲器補償和立體聲聲場加寬。這種處理技術(shù)可與高端演播室設(shè)備的效果相媲美,能夠彌補由于揚聲器、功放和聽音環(huán)境的實際限制所引起的失真,從而明顯改善音質(zhì)。

借助方便易用的SigmaStudio開發(fā)工具,用戶可以使用不同的功能模塊以圖形化的方式配置信號處理流程, 例如雙二階濾波器、動態(tài)處理器、電平控制和GPIO接口控制等模塊。

噪底

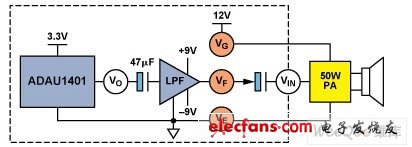

與便攜式設(shè)備不同,車載音響系統(tǒng)配有高功率放大器,每個功放能夠提供高達(dá)40 W-50 W功率,每輛汽車至少有四個揚聲器。由于功率較大, 噪底很容易被放大,使得人耳在安靜的環(huán)境下就能感受到。例如,假設(shè)揚聲器靈敏度約為90 dB/W,則4 Ω揚聲器中的1 mV rms噪聲可以產(chǎn)生大約24 dB的聲壓級(SPL),這一水平噪音人耳在安靜環(huán)境下就能夠感受到。可能的噪聲源有很多, 如圖1所示,主要噪聲源包括電源噪聲(VG)、濾波器/緩沖器噪聲(VF)以及電源接地布局不當(dāng)引起的噪聲VE。VO是來自處理器的音頻信號,VIN是揚聲器功率放大器的音頻輸入信號。

圖1. 車載音響系統(tǒng)的噪聲源示例

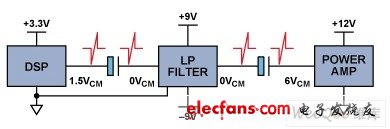

電源開關(guān)期間的爆音:車載音頻功率放大器一般采用12 V單電源供電,而DSP則需要使用低壓電源(例如3.3 V),濾波器/緩沖器可能采用雙電源供電(例如±9 V)。在以不同的電源電壓工作的各部分電路之間,必須使用耦合電容來提供信號隔離。在電源開/關(guān)期間,電容以極快的速度充電/放電,產(chǎn)生的電壓跳變沿著信號鏈傳播,最終導(dǎo)致?lián)P聲器發(fā)出爆音。圖2顯示了這一過程。

圖2. 揚聲器產(chǎn)生爆音的原理

雖然知道噪底和爆音的來源,而且也努力采用良好的電路設(shè)計和布局布線技術(shù),以及選擇噪聲更低的優(yōu)良器件來降低信號源處的噪聲,但在設(shè)計過程中仍然可能出現(xiàn)許多不確定性。汽車多媒體系統(tǒng)的設(shè)計人員必須處理許多復(fù)雜問題,因此必須具備高水平的模擬/混合信號設(shè)計技能。即便如此,原型產(chǎn)品的性能仍有可能與原來的預(yù)期不符。例如,1 mV rms的噪聲水平會帶來巨大挑戰(zhàn)。至于爆音,現(xiàn)有解決方案使用MCU來控制電源開關(guān)期間功率放大器的操作順序,但當(dāng)MCU距離功率放大器較遠(yuǎn)時,布局布線和電磁干擾(EMI)會構(gòu)成潛在問題。

功耗

隨著車載電子設(shè)備越來越多,功耗問題變得日趨嚴(yán)重。例如,如果音頻功率放大器的靜態(tài)電流達(dá)到200 mA,則采用12 V電源時,靜態(tài)功耗就高達(dá)2.4 W。如果有一種方法能檢測到?jīng)]有輸入信號或信號足夠小,進(jìn)而關(guān)閉功率放大器,那么在已開機但不需要揚聲器發(fā)出聲音的時候,就可以節(jié)省不少功耗。

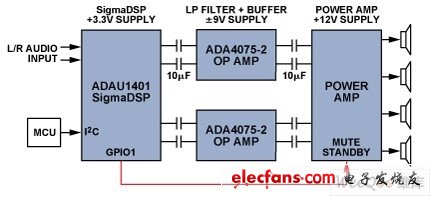

將車載音響系統(tǒng)的噪聲和功耗降至最低

利用SigmaDSP技術(shù),就可以提供這樣一種方法, 可以減小系統(tǒng)噪聲和功耗,同時不增加硬件成本。圖3是一個4揚聲器車載音響系統(tǒng)的框圖,其中ADAU1401 SigmaDSP處理器用作音頻后處理器。除了采樣、轉(zhuǎn)換、音頻信號數(shù)字處理和生成額外的揚聲器通道以外,SigmaDSP處理器還具有通用輸入/輸出 (GPIO)引腳可用于外部控制。微控制器(MCU)通過I2C接口與SigmaDSP處理器進(jìn)行通信,模擬輸出驅(qū)動一個采用精密運算放大器 ADA4075-2的低通濾波器/緩沖器級。

圖3. 四揚聲器車載音響系統(tǒng)

SigmaDSP處理器與功率放大器之間的紅色信號線控制功率放大器的靜音/待機引腳。在正常默認(rèn)工作模式下,開集GPIO1引腳通過10 kΩ上拉電阻設(shè)置為高電平(圖中未標(biāo)注)。ADAU1401具有均方根信號檢測功能,可確定是否存在輸入信號。當(dāng)沒有輸入信號時,GPIO1變?yōu)榈碗娖剑β史糯笃髦糜陟o音/待機模式,因而揚聲器沒有噪聲輸出,同時功放的待機功耗也很低。當(dāng)檢測到高于預(yù)定閾值(例如–45 dB)的輸入信號時,GPIO1變?yōu)楦唠娖剑β史糯笃髡9ぷ鳌_@時雖然噪底仍然存在,但由于信號的高信噪比(SNR)將其屏蔽,使它不易被人耳感知到。

電源開關(guān)期間,SigmaDSP處理器(而不是MCU)通過響應(yīng)MCU的命令直接控制功率放大器的靜音/待機。例如,在電源接通期間,來自MCU的控制信號通過I2C接口設(shè)置SigmaDSP處理器的GPIO1,使之保持低電平(靜音),直到預(yù)定的電容充電過程完成,然后MCU將 GPIO1設(shè)置為高電平,由此消除啟動瞬變所引起的爆音。關(guān)閉電源時,GPIO立即變?yōu)榈碗娖剑构β史糯笃魈幱陟o音/待機狀態(tài),從而消除電源切斷時產(chǎn)生的爆音。將功率放大器置于SigmaDSP處理器而不是MCU的直接控制之下的原因是SigmaDSP處理器通常距離功率放大器更近,因此布局布線和 EMI控制也更容易實現(xiàn)。

如上所述,利用SigmaStudio軟件算法可以測量輸入信號的均方根電平。使用SigmaStudio圖形開發(fā)工具,很容易設(shè)置均方根檢測模塊,并用它來控制GPIO狀態(tài),如圖4的范例所示。

?

圖4. SigmaStudio均方根檢測、GPIO控制和壓限器電路圖

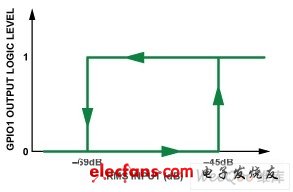

均方根檢測功能利用均方根算法單元和邏輯單元實現(xiàn)。信號閾值必須具有遲滯功能,用以消除靜音功能響應(yīng)小變化而產(chǎn)生的震顫。例如RMS1閾值設(shè)置為–45 dB,RMS2閾值設(shè)置為–69 dB。當(dāng)輸入信號高于–45 dB時,GPIO1為高電平。當(dāng)輸入信號低于–69 dB時,GPIO1為低電平。當(dāng)輸入信號位于這兩個閾值之間時,GPIO1輸出信號保持先前所處的狀態(tài)(參見圖5)。

圖4還顯示了用以進(jìn)一步降低輸出噪聲的壓限器功能。例如,當(dāng)輸入信號低于–75 dB時,揚聲器系統(tǒng)的輸出信號將會衰減到–100 dB,從而也降低了系統(tǒng)噪底。

圖5. RMS閾值設(shè)置以及輸入與輸出之間的關(guān)系

總結(jié)

噪聲和功耗是車載音響系統(tǒng)設(shè)計面臨的巨大挑戰(zhàn)。ADI公司的SigmaDSP處理器已廣泛應(yīng)用于車載音響系統(tǒng)的數(shù)字音頻后處理,若利用其均方根檢測和 GPIO控制功能來顯著降低噪聲和功耗,則能進(jìn)一步發(fā)揮更大作用。SigmaStudio圖形化開發(fā)工具支持以圖形方式設(shè)置各種功能,而不需要編寫代碼,令設(shè)計工作倍加簡單。此外,由于功率放大器模塊通常離SigmaDSP處理器比離MCU更近,因此用SigmaDSP處理器來控制靜音功能,可以簡化布局布線工作并提高EMI抗擾度。

五、基于CPCI總線的多片ADSP-TS201引導(dǎo)設(shè)計

?

數(shù)字信號處理器DSP是一種具有特殊結(jié)構(gòu)的微處理器,它專門為實現(xiàn)數(shù)字信號處理的各種算法而設(shè)計,因而在硬件結(jié)構(gòu)上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定點和浮點計算功能的高速DSP。該處理器廣泛應(yīng)用于視頻、通信市場和國防軍事裝備中,適合于大數(shù)據(jù)量實時處理的應(yīng)用領(lǐng)域。

TigerSHARC系列DSP引導(dǎo)程序的加載方法非常靈活,可根據(jù)實際系統(tǒng)的需求靈活選用。某雷達(dá)信號處理機采用6U板形,CPCI總線采用歐洲卡尺寸標(biāo)準(zhǔn),通過CPCI總線與主機進(jìn)行數(shù)據(jù)通信。針對該信號處理機硬件系統(tǒng),本文提出一種引導(dǎo)方案,該方案采用CPCI總線向板卡傳輸引導(dǎo)代碼,進(jìn)而依靠FPGA通過鏈路口引導(dǎo)DSP自啟動。

1 ADSP-TS201引導(dǎo)模式

DSP的引導(dǎo)就是在DSP系統(tǒng)復(fù)位的情況下從DSP外部存儲器裝載算法程序代碼的過程。TS201支持兩種引導(dǎo)模式:主引導(dǎo)(Master Boot)模式和從引導(dǎo)(S|ave Boot)模式。

在主引導(dǎo)模式下,TS201作為主動方,用外部口輸出地址,讀引導(dǎo)方式選擇(![]() )等控制信號,從EPROM或FLASH中加載代碼。在從引導(dǎo)模式下,TS201作為被動方,不向外部輸出控制信號,外部主機或其他設(shè)備向TS201的主機或鏈路口傳送要加載的代碼,TS201僅啟動若干DMA通道,并執(zhí)行第一個DMA所接收的加載核。

)等控制信號,從EPROM或FLASH中加載代碼。在從引導(dǎo)模式下,TS201作為被動方,不向外部輸出控制信號,外部主機或其他設(shè)備向TS201的主機或鏈路口傳送要加載的代碼,TS201僅啟動若干DMA通道,并執(zhí)行第一個DMA所接收的加載核。

另外,F(xiàn)S201還可以選擇一種“非引導(dǎo)”模式,或利用TS201的(仿真器)USB-ICE加載程序,這種方式可直接將程序加載到TS201內(nèi)部的RAM或外部的RAM中,DSP直接從RAM中運行程序,常用于DSP的調(diào)試過程。

通過對TS201的![]() 引腳的設(shè)置,可將DSP的引導(dǎo)過程設(shè)置成主引導(dǎo)模式或從引導(dǎo)模式。在DSP復(fù)位期間,如果引腳為低電平,則選擇主引導(dǎo)模式,DSP從外部EPROM或FLASH中加載程序;若

引腳的設(shè)置,可將DSP的引導(dǎo)過程設(shè)置成主引導(dǎo)模式或從引導(dǎo)模式。在DSP復(fù)位期間,如果引腳為低電平,則選擇主引導(dǎo)模式,DSP從外部EPROM或FLASH中加載程序;若![]() 引腳為高電平,則進(jìn)入從引導(dǎo)模式,DSP為空閑狀態(tài),等待主機或鏈路口加載程序。兩種引導(dǎo)模式都有相同的加載過程,具體步驟如下:

引腳為高電平,則進(jìn)入從引導(dǎo)模式,DSP為空閑狀態(tài),等待主機或鏈路口加載程序。兩種引導(dǎo)模式都有相同的加載過程,具體步驟如下:

(1)TS201自動啟動一個DMA,自動把256個字(32位)傳送到內(nèi)部存儲器的地址0x00~0xFF。

(2)TS201執(zhí)行上述256個字的指令(加載核),加載核啟動其他DMA,把后續(xù)指令和數(shù)據(jù)加載到內(nèi)部和/或外部存儲器中。

(3)加載核自我覆蓋,執(zhí)行DSP算法程序。

本系統(tǒng)引導(dǎo)方案采用從引導(dǎo)模式,通過CPCI總線將代碼從主機傳至FPGA中,再利用FPGA經(jīng)過鏈路口啟動DSP。

2 某雷達(dá)信號處理機的引導(dǎo)設(shè)計方案

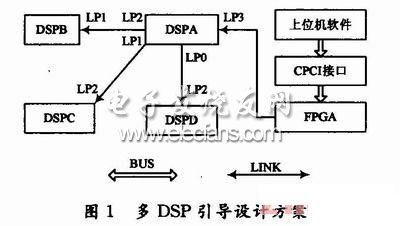

基于某雷達(dá)信號處理機硬件處理平臺,采用如圖1所示的多DSP引導(dǎo)設(shè)計方案。

4片DSP的算法程序代碼(.LDR文件)通過上位機軟件傳輸?shù)紽PGA中,F(xiàn)PGA通過與DSPA的鏈路口給DSPA加載程序。DSPA加載成功后,分別引導(dǎo)DSPB,DSPC,DSPD啟動。

采用這種方式加載DSP的優(yōu)點:調(diào)試DSP時可以不使用JTAG仿真器;同時當(dāng)DSP自啟動時,可以不采用FLASH或E2PROM存放程序代碼,對于DSP程序的大小沒有限制,也節(jié)約了電路板的空間及其硬件設(shè)計復(fù)雜度。

采用這種方式加載DSP的難點:CPCI總線與FPGA數(shù)據(jù)傳輸無誤及FPGA與TS201鏈路口通信,這兩個難點在實際工程中都已經(jīng)解決。CPCI總線與FPGA接口可以采用PLX9656芯片完成數(shù)據(jù)傳輸,所以這種加載模式的設(shè)計是可行的。

2.1 自動引導(dǎo)程序設(shè)計思路

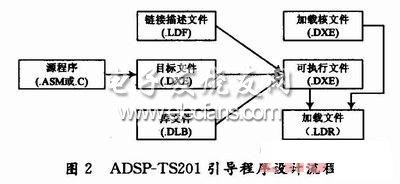

為了設(shè)計加載(自動引導(dǎo))程序,首先必須了解ADSP-TS201的軟件設(shè)計流程,其流程圖如圖2所示。

其中,鏈接描述文件(.LDF)定義了整個系統(tǒng)的存儲器配置和程序中數(shù)據(jù)及代碼的具體存放位置。加載核文件(.DEX)是指加載引導(dǎo)核程序,其功能是將用戶工程所編譯成功的可執(zhí)行文件(.DXE)合成一個鏈路口加載方式的輸出文件(.LDR)。該加載輸出文件用來定義加載過程中TS201的內(nèi)部和外部存儲器如何被初始化。

在VisualDSP++安裝目錄的ldr子目錄下,ADI公司提供了標(biāo)準(zhǔn)加載核文件和相應(yīng)的源程序(.ASM)和鏈接描述文件。一般可直接使用提供的標(biāo)準(zhǔn)加載核文件或?qū)ζ湎鄳?yīng)的源程序進(jìn)行簡單修改,重新編譯鏈接生成的加載核文件。加載文件是由引導(dǎo)加載器 (elfloader)將可執(zhí)行文件進(jìn)行一定的格式變化,并在起始位置附加上加載核文件生成的。

由于TS201有三種引導(dǎo)方式(不考慮非引導(dǎo)模式),ADI公司相應(yīng)地提供了三種不同的加載和文件,分另0為:TS201_prom.dxe,TS201_li- nk.dxe,TS201_host.dxe。三個程序的核心思想和功能完全一致,只是由于使用的加載端口和方式不同,在具體代碼實現(xiàn)上稍有差異。由于本系統(tǒng)采用鏈路口啟動,同時對于DSPA,DSPB,DSPC,DSPD都采用不同的鏈路口啟動,因此采用鏈路口加載核文件,需要對加載核文件稍作修改,滿足不用鏈路口啟動的需求。

2.2 本信號處理機的復(fù)位引導(dǎo)設(shè)計流程

如圖1所示,4片DSP要運行的程序最終通過上位機讀取后,通過CPCI總線傳至FPGA,4片DSP為鏈路口引導(dǎo)模式。DSP復(fù)位后,DSPA從FPGA加載程序,DSPA加載完成后,再分別通過鏈路口加載DSPB,DSPC,DSPD。加載完成后,4片DSP正常執(zhí)行各自的程序。

結(jié)合以上各部分的分析,可以看出要實現(xiàn)該信號處理機中4片DSP的正確引導(dǎo),所需的工作由以下幾步組成:

(1)由DSPB要執(zhí)行的程序(DSPB.dxe),結(jié)合鏈路口的加載核程序生成DSPB的加載文件(DSPB_bin.ldr)。需要注意的是,該鏈路口加載核程序不能直接使用提供的標(biāo)準(zhǔn)鏈路口加載程序,必須將提供的鏈路口加載核文件(TS201_link.asm)中的LINK常數(shù)改為 1(#define LINK 1),即DSPB由鏈路口1引導(dǎo)。

(2)與(1)類似,生成DSPC的加載文件 (DSPC_bin.ldr),只是需要把鏈路口加載核文件(TS201_link.asm)中的LINK常數(shù)改為2(#define LINK 2),即DSPC由鏈路口2引導(dǎo)。同樣DSPD由鏈路口2加載,同樣生成DSPD的加載文件(DSPD_bin.ldr)。

(3)由于 DSPA要通過鏈路口來對DSPB,DSPC,DSPD進(jìn)行程序引導(dǎo),所以在進(jìn)行DSPA編程時,需要在程序的最開始添加給后面所有ADSPTS2 01的引導(dǎo)程序。而每片ADSP-TS201的程序都由引導(dǎo)碼和用戶程序構(gòu)成,所以在DSPA給其余DSP傳輸程序時將傳輸完整.1dr文件的數(shù)據(jù)。

DSPA程序流程圖如圖3所示。

(1)DSPA關(guān)閉所有中斷,所有鏈路口和所有DMA通道,進(jìn)行初始化;

(2)開啟鏈路口3,2,1,0,設(shè)置鏈路口3接收中斷,鏈路口2,1,O發(fā)送中斷;

(3)設(shè)置鏈路口3通過DMA模式接收128 b數(shù)據(jù);

(4)判斷目前加載的DSP,設(shè)置相應(yīng)的鏈路口,發(fā)送接收到的128 b數(shù)據(jù);

(5)判斷DSPB,DSPC,DSPD是否加載完成,否則繼續(xù)通過鏈路口3接收數(shù)據(jù),直到DSP都加載完成;

(6)加載完成后,DSPA運行自身DSP程序。

3 系統(tǒng)測試結(jié)果

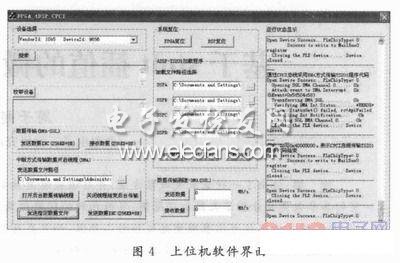

上述引導(dǎo)設(shè)計在某雷達(dá)信號處理機中得到驗證,通過上位機軟件,能靈活地加載引導(dǎo)代碼,使得調(diào)試更加便捷。測試上位機軟件如圖4所示。

修改雷達(dá)系統(tǒng)的數(shù)字信號處理算法,成功地將算法代碼加載到信號處理機中,從而驗證引導(dǎo)設(shè)計方案正確可行。

4 結(jié)語

本文以某雷達(dá)信號處理機為平臺,設(shè)計實現(xiàn)了基于CPCI總線的鏈路口多DSP引導(dǎo)方案,介紹了軟件設(shè)計流程及引導(dǎo)方案思想,最后成功驗證了本引導(dǎo)方案的正確性和可行性。本引導(dǎo)方案不使用FLASH或E2PROM存放代碼,使多DSP的軟件編寫更加靈活,調(diào)試更加方便,同時使得硬件電路設(shè)計更加簡潔。

?

電子發(fā)燒友App

電子發(fā)燒友App

評論