在選擇FPGA時,關注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因為它們是FPGA架構中的兩個核心資源,對于設計的性能和資源利用至關重要。

2023-11-21 15:03:06 548

548

FPGA 使用新手 調用雙口ram 中的數據。操作遇到問題。 DSP跟FPGA數據交互正常,但是在FPGA內,編寫verilog按照dsp 的時序去讀取字節數據存在問題,讀出來的數據都為0x00;有哪位大蝦能提示下,這個使用過程中需要注意的關鍵。

2016-02-17 17:03:16

利用FPGA設計雙口ram,最大設計多的空間的?如果是cpld來實現,空間是不是更小?如何去確定這個大小呢?求指導

2013-10-21 21:23:21

各位大神,我最近在做FPGA項目遇到一個問題,我想實現這樣的功能:向RAM里寫一次數據,再多次讀出來,可是我發現IP核里的RAM讀第二次的時候RAM數據就清零了,根本讀不我寫的數據,請問有什么好的解決辦法嗎?謝謝啦!

2015-06-07 20:31:57

[attach]***[/attach](給出雙口RAM的結構.介紹雙口RAM的忙邏輯,并主要介紹了在雷達終端的數據處理過程中兩個 CPU通過雙El RAM進行數據的儲存、交換和共享的設計原理和方法。

2012-08-11 16:21:22

利用FPGA自帶的IP核實現雙口RAM用于2片MCU進行數據交換時多次讀數據后RAM中數據變為了0,是什么意思,打什么幫幫忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

本帖最后由 mr.pengyongche 于 2013-4-30 02:56 編輯

雙口RAM怎么實現左右兩側同時寫入這是怎么實現

2012-08-15 18:18:34

用雙口RAM實現和DSP的通信,用chipscope將要看的輸出信號加進去的時候發現信號線呈現紅色,BASE TYPE是IOBUF類型,這個應該是錯的,加信號進去會警告提示布局布線可能會出錯,事實的確如此,有人知道是什么原因嗎?

2016-04-20 20:06:44

,寫信號wr,我使用FPGA實現雙口ram,雙口ram一端連接主板的雙口ram信號,另外一端連接我的nios II處理器由于控制采集處理等,現在問題存在地址沖突,比如我將數據存在0x00

2018-01-18 13:51:58

系統結構與功能: lpc3131外接8k*8雙口ram與8G Flash,從雙口ram讀取數據(來自FPGA),并存至Flash中。問題: 丟數據,系統速度遠低于ram的讀速與Flash的寫速度。雙

2011-08-04 11:05:31

告訴我,對于所有斯巴達3代設備,RAM是18Kbit塊,這意味著該塊的最大雙端口實現是512深36寬。我知道要弄清楚我需要什么,我必須寫兩個塊然后并行運行它們然而我不知道該怎么做。誰能幫幫我嗎。是不是

2019-02-13 08:12:00

本帖最后由 咖小啡 于 2011-3-23 11:41 編輯

請高手指教DSP-TMS320F2812與雙口RAM-IDT7130的通信程序,

2011-03-23 11:41:04

ERAM用作簡單雙口RAM時,哪個信號可以作為wren使用?

2023-08-11 09:50:55

和后仿真。以上介紹了一種應用于通用微處理器系統中的SDRAM與雙口RAM之間的數據轉移接口控制電路,由VHDL語言設計,用Xilinx公司4000系列FPGA實現,目前該電路硬件實現和微處理器系統已經通過驗證,證明可將SDRAM作為高速、大容量存儲器應用在簡單電子系統中。

2019-06-10 05:00:08

SDRAM與雙口RAM的區別?它們兩者一樣嗎?不一樣的話能互相代替使用嗎?

2012-09-05 16:51:10

過多介紹。下面給出幾個各種實現方式的Verilog示例代碼。分布式RAM下面給出一個異步讀模式的雙口分布式RAM的示例:module rams_dist ( input [5:0]a, dpra, output [15:0]spo, dpo if (we) ram[a]

2020-09-29 09:40:40

雙口RAM如何實現跨時鐘域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

`嵌入式RAM使用之雙端口RAM實驗目的: 1.學習Altera公司Cyclone IV系列器件的內部結構2.學會調用Quartus II軟件中提供雙口RAM核并進行仿真實驗平臺:芯航線FPGA學習

2017-01-02 09:40:23

應用系統實驗平臺:芯航線FPGA學習套件核心板實驗原理:為了實現通過串口發送數據到FPGA中,FPGA接收到數據后將數據存儲在雙口ram的一段連續空間中,當需要時,按下按鍵0,則FPGA將RAM中存儲

2017-01-04 00:54:36

針對目標板上的雙口RAM芯片的右端口進行讀寫測試,來檢測右端口和內部存儲地址的正確性。原理圖1:RS422接口:MCU:LDO:DB9接口:PCB LAYOUT:PCB 3D view:

2018-08-30 09:48:15

活動第一季——看教程,秀筆記,贏好禮https://bbs.elecfans.com/jishu_520463_1_1.html23【連載視頻教程(十三)】嵌入式塊RAM應用之雙口RAM:https

2015-10-23 12:47:16

什么是雙口RAM?基于FPGA的雙口RAM有哪些應用?

2021-05-06 07:41:03

設計來增設全新的芯片功能,據此實現了芯片整體構造的簡化與性能提升。下面英尚微電子介紹FPGA開發板內部ram是如何操作的。 除邏輯外,所有新的FPGA都有專用的靜態ram塊,這些塊在邏輯元素之間分布并由

2020-09-10 11:11:57

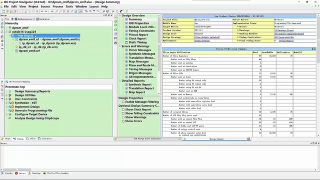

`例說FPGA連載84:工業現場實時監控界面設計之雙口RAM特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc ① 在新建的工程中,點擊菜單

2017-03-26 21:18:53

我現在需要設計一個雙口的ram,它要求數據和地址線是復用的,雙向的,想利用FPGA設計,請教下大家思路,謝謝。

2012-07-13 08:52:18

在設置雙口RAM的時候,我想在數據同時讀寫時,先讀這個地址上一次的數據再寫入新的數據,就和ise中的read first類似。但是我設置的仿真結果總是先把數據寫進去再讀取,等于輸入什么輸出什么,有什么辦法么?

2020-03-16 10:25:01

哪位大神有verilog實現的雙口RAM例程,就教!

2015-07-29 20:44:56

畢業設計在做基于FPGA的多通道數據采集系統,現在基本的硬件原理圖已經完成就還有一個USB控制芯片(CY7C68013,56引腳)與雙口RAM(CY7C09279V-12AC)之間的接口和通信

2014-04-16 21:14:56

的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系統中的海量數據存儲和時鐘匹配。功能仿真驗證該設計的正確性,該設計能減小電路設計的復雜性,增強設計的靈活性和資源的可配置性能,降低設計成本,縮短

2010-04-24 09:44:28

的下一個周期將讀控制信號置為無效,狀態機恢復為讀空閑狀態。3 FPGA仿真實現在Modelsim開發平臺下,實現了PCI9052讀寫雙口RAM的仿真過程,該仿真波形如圖4所示。從仿真波形可以看出該代碼可以

2018-12-12 10:27:45

介紹一種基于雙口RAM的L0NW0rkS現場總線智能通信節點的設計方法,并給出詳細的設計步驟、硬件及軟件實現。通過此LonWorkS智能通信節點,能夠完成RS-232-C/RS-485標準

2011-03-08 17:25:48

,利用基于雙端口RAM 中一種巧妙的地址映射機制實現同時對多行代碼設置斷點的功能,并且能夠方便地實現被調試系統和調試主機之間調試信息和命令的交互。UDM 還具有易于擴展的優點,當SOPC 系統中有多個

2020-08-15 09:59:40

最近再做一個雙CPU板子,需要搭建一個雙DSP系統,它們之間的數據傳輸通過雙口RAM通訊,求各位大神指導

2016-05-04 13:00:06

求教大牛關于CPLD的雙口RAM設計程序!

2012-10-22 16:18:14

大神們。我是新手!求解決 在做FPGA 配置雙口RAM和rom如何消除讀取延遲

2015-11-17 19:42:18

如何利用FPGA實現UART的設計?UART的結構和幀格式

2021-04-08 06:32:05

本文介紹了一種利用雙口RAM實現DSP與單片機高速數據通信的方法,給出了它們之間的接口電路以及軟件實現方案。

2021-06-03 06:18:37

如何利用雙端口RAM去實現PCI總線接口?

2021-05-06 06:30:53

本文結合組合導航系統設計,介紹了利用又口RAM實現導航計算機主從機之間通信的一種實用、高效的系統設計方法。

2021-05-28 06:58:45

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個單獨的奇偶校驗寫使能位,但在FPGA RAM中沒有單獨的Pariaty寫使能位。 如何實現ASIC RAM奇偶校驗寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

PCI9052是什么?什么是雙DRAM?怎樣去設計PCI和雙口RAM之間的接口?

2021-05-07 06:03:59

請教各位大神!是否可以通過FPGA內核配置的雙口RAM,實現FPGA與DSP之間的數據交換?可以的話怎么實現?怎么設置FPGA的內核RAM?如何連接DSP的外部存儲器XINTF的引腳和FPGA的引腳?謝謝!

2017-12-07 15:44:03

技術要求;通過雙口RAM接收捷聯慣性導航系統IMU及系統實時解算等數據并以bin格式文件形式將其存儲在SD卡中,以時間為文件名保存,SD卡不小于16GB,數據存儲速率不小于50000字節/秒(數據頻率500HZ,每幀100字節)有大神愿意做的聯系,名字q

2018-05-07 13:45:20

我想選一片雙口RAM,是32KX8,5V供電的,我首先選擇了IDT7007但是發現沒有工業級的,軍用級價格很貴但是采購有很麻煩,請求大家推薦一塊雙口RAM!謝謝大家!!!

2011-09-20 10:30:19

小弟最近在設計一款雙核采集系統使用ep1c6q240c8和tms320vc5509a雙核,兩塊芯片使用外部雙口RAM進行數據傳輸,請教各位大神ep1c6q240c8怎么和雙口RAM連接啊???????????????????????

2012-11-05 10:42:41

從雙口ram里讀數據的時候一直有兩個時鐘的延時??[attach]***[/attach]

2017-05-13 09:38:29

我想用fpga實現一個雙口的ram,有8位的數據和地址線,他們是共享的,分時復用,請問怎么解決這個問題,另外讀寫沖突的問題怎么解決應該,哪位高手指點一下,謝謝啦。

2012-07-10 11:21:39

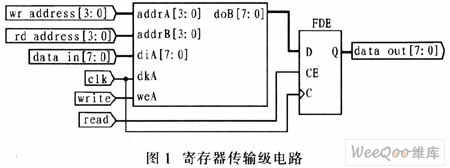

使用FPGA自行設計橋接電路,本設計結合系統需要,采用雙口RAM實現數據交換,FPGA實現接口邏輯轉換。接口設計方案如圖1所示。圖1中DSP為Analog Devices公司TS101,4片TS101

2019-04-22 07:00:07

你好,我想知道簡單的雙端口和真正的雙端口RAM之間的資源使用差異? True雙端口Ram中的額外讀寫端口是否在不使用fpga結構資源的情況下處理?如果這是真的那么為什么要專門使用簡單的雙端口配置呢

2019-06-10 07:15:24

在FPGA中怎樣去構造存儲器?如何利用庫函數去構造雙端口RAM?庫函數法構造雙端口RAM的有哪些步驟?其它存儲器的構造方法有哪些?雙端口RAM在高速數據采集中有什么應用?

2021-04-14 06:57:55

為了在高速采集時不丟失數據,在數據采集系統和CPU之間設置一個數據暫存區。介紹雙口RAM的存儲原理及其在數字系統中的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系

2010-02-11 11:20:27 69

69 摘要:分析了在空間環境下影響RAM可靠性的主要因素及主要故障模式,介紹了利用FPGA實現RAM檢錯糾錯電路的方法,給出了仿真結果,并將此方法同用中小規模集成電路實現RAMEDAC的方

2010-05-10 09:42:23 15

15 基于Actel FPGA 的雙端口RAM 設計雙端口RAM 芯片主要應用于高速率、高可靠性、對實時性要求高的場合,如實現DSP與PCI 總線芯片之間的數據交換接口電路等。但普通雙端口RAM 最大

2010-11-15 17:44:19 82

82 利用FPGA實現時分多址的方法有很多種,但大多數方法都對FPGA芯片資源的占用非常巨大。針對這一問題,提出一種改進型方法來實現時分多址。通過使用FPGA芯片內部的雙口隨機訪問存儲器(雙口RAM),利用同一塊RAM采用兩套時鐘線,地址線和數據線,例化雙口RAM的

2011-01-15 15:41:26 29

29 摘要: 在高速并行流水信號處理中,ASIC(FPGA)+DSP+RAM是目前國際流行的一種方式,尤其是FPGA+DSP+RAM更適合中國的國情.本文利用FPGA的算術邏輯單元與外部存儲器相結合,解決了線路板面積有限與雷達數據處理需要大量存儲空間的矛盾;利用FPGA的并行流水特點解決了

2011-02-27 16:00:26 83

83 FPGA內部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA中RAM的使用探索。以4bitX4為例,數據位寬為4,深度為4。

2018-03-28 17:07:28 9726

9726

大家好,又到了每日學習的時間了,今天我們來聊一聊在FPGA設計中RAM的兩種使用方法,RAM是用來在程序運行中存放隨機變量的數據空間,使用時可以利用QuartusII的LPM功能實現RAM的定制

2018-06-08 11:30:28 19561

19561 本文介紹了如何在FPGA 中利用Block RAM 的特殊結構實現HDTV視頻增強算法中灰度直方圖統計。

2019-07-10 08:10:00 2578

2578 些大材小用,因此xilinx公司在其FPGA內部專門集成了很多存儲器模塊,稱作Block RAM,其猶如slice海洋當中的一顆顆明珠,專門實現數據暫存功能,且每個時鐘區域都布置了若干個Block

2020-11-23 14:08:43 7378

7378

在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優化整個設計,節約資源利用率,充分開發FPGA芯片中的潛在價值,本文結合安路科技FPGA做簡單總結,說明基本原理。

2020-12-24 14:28:09 916

916 我們知道,RAM是用來在程序運行中存放隨機變量的數據空間,使用時可以利用QuartusII的LPM功能實現RAM的定制。

2020-12-30 16:27:53 9

9 FPGA可以調用分布式RAM和塊RAM兩種RAM,當我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數據的情況,同樣它也是ROM,FIFO的基礎。本實驗將為大家介紹如何使用FPGA內部的RAM以及程序對該RAM的數據讀寫操作。

2022-02-08 15:50:49 12183

12183

FPGA在一個時鐘周期可以讀取多個RAM數據嗎?如何理解FPGA中存放程序的RAM? FPGA在一個時鐘周期可以讀取多個RAM數據 FPGA中的RAM是FPGA中存儲數據的主要形式之一,許多FPGA

2023-10-18 15:28:20 598

598 FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現并行訪問。

2024-03-15 13:58:14 80

80

電子發燒友App

電子發燒友App

評論