本文將介紹三個(gè)常見(jiàn)的ARM SoC,包含ARM7和ARM9,并試著分析與比較它們的性能。

ARM7族群

低耗電量和低成本是ARM7的優(yōu)點(diǎn)。不過(guò),ARM7的最大執(zhí)行速率不到100 MHz,因此,在應(yīng)用上,它和8051之類的微控制器(MCU)類似,但在功能上,ARM7通常優(yōu)于MCU。

由于一般的MCU都是8-bit,而且不支持操作系統(tǒng)(O.S.),所以使用MCU開(kāi)發(fā)應(yīng)用產(chǎn)品的成本通常會(huì)比使用ARM7來(lái)得便宜。然而,就簡(jiǎn)單的應(yīng)用而言,ARM7也可以不需要操作系統(tǒng),只使用純粹的韌體,照樣可以達(dá)到和MCU一樣或優(yōu)于MCU的效能。

TI的TMS470

它的CPU核心是ARM7TDMI,16/32-bit RISC。其正常模式的系統(tǒng)時(shí)脈是28 MHz、管線模式是48 MHz。內(nèi)含128K Bytes的FLASH和8K Bytes的SRAM。其它電路單元還包含:

零腳位鎖相回路(ZPLL)時(shí)脈模塊。

模擬的看門狗定時(shí)器(analog watchdog timer;AWD)。

實(shí)時(shí)中斷模塊(real-time interrupt;RTI)。

兩個(gè)”序列外圍接口”(SPI)模塊。

兩個(gè)”序列通訊接口”(SCI)模塊。

標(biāo)準(zhǔn)的”控制局域網(wǎng)絡(luò)”(control area network;CAN)控制器(SCC)。

第二類序列界面(C2SIa)。

10-bit、16個(gè)輸入信道多重緩沖”模擬數(shù)字轉(zhuǎn)換器”(MibADC)。

高階定時(shí)器(high-end timer;HET),控制16個(gè)輸出入端口(I/O)。

外部時(shí)脈預(yù)分頻器(external clock prescale;ECP)。

共49個(gè)I/O腳位,1個(gè)只能輸入的腳位。

TMS470的系統(tǒng)功能有:

地址譯碼。

保護(hù)內(nèi)存。

監(jiān)督內(nèi)存和各外圍的總線。

重置(reset)和取消(abort)的例外管理。

所有內(nèi)部中斷源的排序(prioritization)。

裝置的時(shí)脈控制。

平行的特性記號(hào)(signature)分析(PSA):是一種自動(dòng)檢測(cè)故障的功能,可以利用多個(gè)輸入的特性記號(hào)來(lái)檢測(cè)數(shù)據(jù)流。這個(gè)特性記號(hào)可以用來(lái)判定處理器是處于好的或壞的狀態(tài)。

上述的ZPLL、HET、MibADC是TMS470的特殊功能。ZPLL包含了一個(gè)PLL、一個(gè)時(shí)脈監(jiān)督(clock-monitor)電路、一個(gè)時(shí)脈致能(clock-enable)電路和一個(gè)預(yù)分頻器(預(yù)分頻值是從1~8)。ZPLL的功能是將外部的參考電壓乘以預(yù)分頻值,以獲得較高的頻率,供給TMS470內(nèi)部使用。ZPLL提供ACLK給TMS470的系統(tǒng)模塊,之后,系統(tǒng)模塊會(huì)產(chǎn)生系統(tǒng)時(shí)脈(SYSCLK)、實(shí)時(shí)中斷時(shí)脈(RTICLK)、CPU時(shí)脈(MCLK)、外圍接口時(shí)脈(ICLK)。所謂”零腳位”是指ZPLL沒(méi)有提供外部濾波器的接腳,亦即不需要連接外部濾波器的意思。

許多不熟悉TI芯片的硬件工程師,經(jīng)常不知道要如何將石英振蕩器(crystal oscillator)或外部的時(shí)脈信號(hào)連接到TI芯片上。其實(shí),TMS470內(nèi)部已經(jīng)具有一個(gè)振蕩器電路(在ZPLL內(nèi)),但若要啟動(dòng)它,外部需要連接一個(gè)4MHz~20 MHz的石英或諧振器(resonator),并且要在OSCIN和OSCOUT腳位之間連接負(fù)載電容,如圖2(a)所示。這個(gè)負(fù)載電容的大小應(yīng)該由石英振蕩器的供貨商提供,如果施予不正確的載電容值,可能無(wú)法使TMS470正常開(kāi)機(jī)和工作。

此外,如果不使用TMS470內(nèi)部的振蕩器,而改用外部的參考時(shí)脈或外部的振蕩器輸出信號(hào),此時(shí)要將1.8V的時(shí)脈信號(hào)連接到OSCIN腳位,并將OSCOUT腳位保持開(kāi)路的狀態(tài),如附圖2(b)所示。當(dāng)然,不同廠牌的芯片的時(shí)脈來(lái)源之連接方式不盡相同,硬件工程師事先應(yīng)仔細(xì)查閱它們的技術(shù)手冊(cè)。

HET是一種先進(jìn)的智能型定時(shí)器,它為實(shí)時(shí)的應(yīng)用提供精確的計(jì)時(shí)功能。此定時(shí)器是由軟件控制的,使用精簡(jiǎn)的指令集、特殊的微電路架構(gòu)、I/O端口。它可以應(yīng)用于數(shù)據(jù)比較、采集,或當(dāng)成GPIO,尤其適用于對(duì)多個(gè)傳感器(sensor)的輸入數(shù)據(jù)做比較,或輸出復(fù)雜的和精確的時(shí)間脈沖(如:PWM脈沖)來(lái)驅(qū)動(dòng)起動(dòng)器(actuator)。

HET的周邊具有”XOR—分享”的功能,此功能可以讓兩相鄰的HET通道被XOR在一起,和HET的標(biāo)準(zhǔn)輸出脈沖相比,這能夠輸出更小的脈沖信號(hào)。

為了讓使用者可以為FLASH、RAM、HET RAM尋址,TMS470有提供“內(nèi)存選擇”(memory selection)的功能。每一個(gè)“內(nèi)存選擇”具有它自己的“內(nèi)存基本地址緩存器(memory base address register)”—MFBAHRx和MFBALRx(分別是高位和低位元),用來(lái)定義各個(gè)內(nèi)存區(qū)塊的起始(基本)地址、區(qū)塊大小和保護(hù)方式。每一個(gè)“內(nèi)存選擇”的基本地址是透過(guò)緩存器來(lái)設(shè)定的,它們應(yīng)該要符合附圖3中的映像地址之邊界值—必須是區(qū)塊大小的整數(shù)倍。圖4是TMS470的“內(nèi)存選擇”的分配情形。

MibADC接受一個(gè)模擬信號(hào),并將它轉(zhuǎn)換成一個(gè)10-bit的數(shù)字信號(hào)。MibADC具有兩個(gè)模式:相容vs.緩沖模式。在兼容模式中,TMS470的“程序模型”(programmer‘s model)和TMS470的ADC模塊兼容,而且MibADC的數(shù)字輸出是儲(chǔ)存在“數(shù)字輸出緩存器”(digital result register)中;“程序模型”包含:緩存器、尋址模式(addressing mode)和中斷。兼容模式能讓ADC的程序設(shè)計(jì)工作變得比較容易,因?yàn)橹灰苯幼x取數(shù)字輸出緩存器即可取得轉(zhuǎn)換后的數(shù)字?jǐn)?shù)據(jù)。在緩沖模式中,數(shù)字元輸出緩存器被3個(gè)FIFO緩沖存儲(chǔ)器取代—分別表示不同的轉(zhuǎn)換群組(事件、群組1、群組2)。在兼容模式中,MibADC的FIFO是被“中斷服務(wù)例程(ISR)”讀取。

Philips的LPC2214

它的CPU核心是16/32-bit ARM7TDMI-S,S是“可合成”(synthesizable)的意思,可讓SoC設(shè)計(jì)業(yè)者能將ARM7TDMI核心快速地和靈活地與其它IP合成。LPC2214的主要特性如下:

內(nèi)建有256 Kbytes的FLASH、16 Kbytes的SRAM,工作速率60 MHz。128-bit的“內(nèi)存加速模塊”(memory accelerator module;MAM),能使CPU快速攫取到(prefetch)下一個(gè)ARM指令,因此,執(zhí)行速率可以達(dá)到60 MHz。

透過(guò)芯片內(nèi)的開(kāi)機(jī)加載軟件(boot loader),可以達(dá)到“系統(tǒng)內(nèi)編程”(In-System Programming;ISP)和“應(yīng)用中編程” (In-Application Programming;IAP)的功能。

所謂”系統(tǒng)內(nèi)編程”是指利用JTAG和軟件,可以在很短的時(shí)間內(nèi)(約30秒~40秒),將使用者系統(tǒng)程序?qū)懭隖LASH中,或清除FLASH的所有內(nèi)容;在這過(guò)程中,并不需要從主機(jī)板中將處理器或FLASH拆除,因此可以節(jié)省成本和時(shí)間。這有利于產(chǎn)品的開(kāi)發(fā);或能讓技術(shù)人員到客戶端更新軟件或參數(shù),且不需要拆機(jī)殼大翻修。目前大多數(shù)的MCU、SoC、DSP、FPGA/CPLD都有提供類似的工具和功能。

所謂“應(yīng)用中編程”是指利用兩組FLASH,可以在遠(yuǎn)程將韌體版本升級(jí)。當(dāng)將第一組FLASH的程序代碼被清除或被重新寫入時(shí),處理器使用第二組FLASH的程序代碼來(lái)執(zhí)行。當(dāng)?shù)谝唤MFLASH的寫入作業(yè)完成之后,系統(tǒng)可以馬上切換去執(zhí)行第一組FLASH里面的程序代碼。這個(gè)功能對(duì)網(wǎng)絡(luò)通訊設(shè)備而言,是很重要的,因?yàn)楫?dāng)韌體版本升級(jí)時(shí),這些設(shè)備的操作系統(tǒng)是不能停止的。

支持EmbeddedICE-RT和Embedded Trace接口,透過(guò)RealMonitor軟件可以進(jìn)行實(shí)時(shí)除錯(cuò)。

8個(gè)通道的10-bit ADC,轉(zhuǎn)換時(shí)間小于2.44μs。

2個(gè)32-bit定時(shí)器(4個(gè)采集信道和4個(gè)比較信道),1個(gè)PWM單元(6個(gè)輸出)、1個(gè)實(shí)時(shí)時(shí)脈產(chǎn)生器(real time clock)、1個(gè)看門狗定時(shí)器。

多種序列接口,這包含:2個(gè)UART、1個(gè)快速I2C(400 Kbps)、2個(gè)SPI。

1個(gè)向量式中斷控制器(可設(shè)定中斷的優(yōu)先級(jí)和中斷向量的地址)。

可設(shè)定的外部?jī)?nèi)存接口,最多可設(shè)定4個(gè)內(nèi)存排組(bank),每排最長(zhǎng)16M-bit和8/16/32-bit的數(shù)據(jù)寬度(因此,支持的最大內(nèi)存空間是64 MBytes)。

最多112個(gè)GPIO腳位(5V)。9個(gè)外部中斷腳位(邊緣或水平觸發(fā))。

內(nèi)建有PLL,支持的最大CPU時(shí)脈為60 MHz。

內(nèi)建有石英振蕩器,工作頻率范圍是1 MHz~30 MHz。

兩種低功率模式:閑置(Idle)和功率下降(Power-down)。

透過(guò)外部中斷,可以將處于“功率下降模式”的處理器喚醒。

為了使功率的利用能夠達(dá)到最佳化,可以開(kāi)啟(enable)或關(guān)閉(disable)個(gè)別的周邊功能。

LPC2214也和TMS470一樣有支持ADC的功能,因此,它們都很適合用來(lái)開(kāi)發(fā)數(shù)據(jù)采集用途的裝置,例如:條形碼掃描機(jī)等。不過(guò),TMS470的MibADC可以支持16個(gè)通道,但LPC2214只支持8個(gè)通道。

其實(shí),LPC2214的PWM的運(yùn)作原理和定時(shí)器一樣。定時(shí)器是依照7個(gè)比較緩存器(match register)來(lái)計(jì)算外圍裝置的時(shí)脈周期數(shù)目,并產(chǎn)生中斷;或當(dāng)定時(shí)器的計(jì)數(shù)數(shù)目達(dá)到特定值時(shí),系統(tǒng)就會(huì)去執(zhí)行指定的工作。因?yàn)樗軌蚍謩e控制上升緣和下降緣的位置,所以應(yīng)用較廣。例如:多相(multi-phase)馬達(dá)的控制通常需要3個(gè)不重迭的(non-overlapped)PWM輸出,分別控制3個(gè)脈沖寬度和位置。7個(gè)比較緩存器能夠提供最多6個(gè)單邊(single edge)控制的,或3個(gè)雙邊(double edge)控制的PWM輸出脈沖。

LPC2214的內(nèi)存映像(圖4)是固定的,在重新映像時(shí),不需要再設(shè)計(jì)其它復(fù)雜的程序代碼,以便在不同的地址區(qū)塊執(zhí)行。其中,CPU中斷向量可以被重新映像,好讓中斷向量能儲(chǔ)存于芯片內(nèi)的FLASH中(默認(rèn)值為0x00000000),或儲(chǔ)存于芯片內(nèi)的SRAM中。藉由設(shè)定MEMMAP緩存器的值,就可以進(jìn)行重新映射,重新映射完成后,開(kāi)機(jī)碼區(qū)塊(boot block)將被搬移(relocate)至芯片內(nèi)存儲(chǔ)器映像的最上方。

LPC2000系列的SoC都具有下列三種工作模式或開(kāi)機(jī)狀態(tài):

開(kāi)機(jī)加載模式:被硬件重置啟動(dòng),之后,開(kāi)機(jī)加載程序會(huì)被執(zhí)行。開(kāi)機(jī)碼區(qū)塊里的中斷向量會(huì)被映像至內(nèi)存映像(FLASH)的最下方,以便于在開(kāi)機(jī)加載過(guò)程,能夠處理例外和中斷請(qǐng)求。

使用者FLASH模式:當(dāng)開(kāi)機(jī)加載程序發(fā)現(xiàn)FLASH里有使用者程序存在時(shí),而且開(kāi)機(jī)加載程序不需要再執(zhí)行時(shí)(沒(méi)有被強(qiáng)制執(zhí)行),就進(jìn)入此模式。(這很像PC的BIOS開(kāi)機(jī)過(guò)程,若一直按F1或DEL鍵,就會(huì)進(jìn)入BIOS模式;若不按此鍵,則操作系統(tǒng)會(huì)正常運(yùn)作。)在此模式中,中斷向量不會(huì)被映射,仍然位于FLASH的最下方。

使用者RAM模式:被使用者程序啟動(dòng)。中斷向量被重新映射至SRAM的最下方。

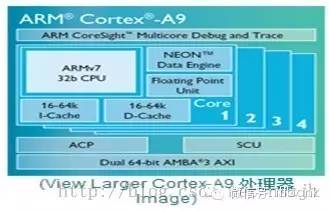

ARM9族群

ARM9大約可以達(dá)到180MHz~200 MHz的工作速率。因此,它能驅(qū)動(dòng)的周邊裝置比ARM7多,應(yīng)用范圍也比較廣。下面舉Atmel的AT91RM9200來(lái)說(shuō)明。

Atmel的AT91RM9200

它的CPU核心是16/32-bit的ARM920T,其主要功能簡(jiǎn)述如下:

內(nèi)建有16 Kbytes的SRAM和128 Kbytes的ROM。

外部總線接口(External Bus Interface;EBI):可以支持SDRAM、SRAM、“暴量傳輸?shù)?burst)”FLASH(亦即NOR FLASH)、能直接(glueless)和CompactFlash、SmartMedia、NAND FLASH連接。

7個(gè)外部中斷來(lái)源,1個(gè)快速中斷來(lái)源。

4個(gè)32-bit可程序I/O控制器,122個(gè)可程序I/O腳位,每個(gè)I/O腳位具有輸入變動(dòng)中斷和”開(kāi)路泄極”(open-drain)的功能。“開(kāi)路泄極”是指在芯片內(nèi)部的MOS FET輸出電路上的泄極沒(méi)有連接任何組件(電阻)。通常,它可以用來(lái)驅(qū)動(dòng)高電流或高電壓的負(fù)載;或者說(shuō),多個(gè)外部裝置可以和此單一線路做雙向通信。

具有20個(gè)信道的周邊裝置控制器(DMA)。

4個(gè)可程序外部時(shí)脈信號(hào)。

內(nèi)建2個(gè)振蕩器,以及2個(gè)PLL。

軟件控制的功率最佳化功能。

實(shí)時(shí)時(shí)脈產(chǎn)生器具有警報(bào)中斷功能。

中斷控制器具有8個(gè)不同等級(jí)的優(yōu)先級(jí)。能個(gè)別屏蔽的向量式中斷來(lái)源,可抑制寄生信號(hào)對(duì)中斷信號(hào)的干擾。

支持以太MAC 10/100 Base-T、MII或RMII,整合了28-byte的FIFO和專屬的DMA傳收通道。

支持USB 2.0(12 Mbps)主機(jī)端口(host port)和裝置端口(device port)。主機(jī)端口有整合FIFO和專屬的DMA。

多媒體記憶卡接口(multimedia card interface;MCI):支持自動(dòng)的通信協(xié)議控制、和自動(dòng)化的數(shù)據(jù)快速傳輸;與MMC和SD標(biāo)準(zhǔn)兼容,最多可支持2個(gè)SD記憶卡。

3個(gè)同步的序列控制器(SSC):每個(gè)傳送器和接收器都具有獨(dú)立的時(shí)脈和訊包同步信號(hào)。支持I2S模擬接口,采用分時(shí)多任務(wù)技術(shù)。

4個(gè)萬(wàn)用同步/異步接收傳送器(USART):可支持RS485、IrDA、調(diào)制解調(diào)器(modem)、ISO 7816的T0/T1 Smart Card。

主從式序列外圍接口(SPI):8到16-bit的可程序數(shù)據(jù)長(zhǎng)度,可以選擇4個(gè)外部外圍芯片。

2組3-通道、16-bit的定時(shí)器/計(jì)數(shù)器(TC):3個(gè)外部輸入時(shí)脈、每個(gè)通道具有2個(gè)多用途I/O腳位。能夠產(chǎn)生雙PWM信號(hào)。

雙線路界面(two-wire interface;TWI):支持主控模式(master mode),支持Atmel所有的雙線路EEPROM。

所有數(shù)字腳位都支持IEEE 1149.1 JTAG邊界掃描。

AT91RM9200算是性能非常強(qiáng)大的SoC,它可以用來(lái)開(kāi)發(fā)通信、儲(chǔ)存、控制等產(chǎn)品。由于它的功能很多,所以本文無(wú)法逐項(xiàng)詳細(xì)說(shuō)明,在此僅介紹它的USB 2.0主機(jī)端口。

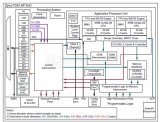

它的USB 2.0主機(jī)端口支持“開(kāi)放式主機(jī)控制器接口”(Open Host Controller Interface;OHCI) v1.0規(guī)格,以及USB v2.0全速(12 Mbps)和低速(1.5 Mbps)規(guī)格的信訊協(xié)議。它整合了1個(gè)“根部集線器”(root hub)和下游的2個(gè)USB傳收器。標(biāo)準(zhǔn)的OHCI USB通訊堆棧驅(qū)動(dòng)程序可以輕易地移植到此架構(gòu)中,不需要顧慮硬件的兼容問(wèn)題;可以執(zhí)行現(xiàn)有全部的USB類別驅(qū)動(dòng)程序,這表示所有標(biāo)準(zhǔn)的USB類別裝置(class device)都能被自動(dòng)偵測(cè),讓使用者應(yīng)用。圖5是其內(nèi)部架構(gòu)圖。

在主機(jī)控制器和主機(jī)控制器驅(qū)動(dòng)程序之間,有兩個(gè)通信信道。第一個(gè)信道使用主機(jī)控制器內(nèi)部的作業(yè)緩存器組,這個(gè)信道的通信對(duì)象(目的地)就是主機(jī)控制器。這組緩存器包含了控制、狀態(tài)、串行指針(list pointer)緩存器。它們都被映像至系統(tǒng)總線(ASB)的映像區(qū)域內(nèi)。其中有一個(gè)指標(biāo)是指向處理器的地址空間—稱為“主機(jī)控制器通訊區(qū)域”(Host Controller Communication Area;HCCA)。HCCA正是第二個(gè)通信信道。在此信道內(nèi),主機(jī)控制器是通信主控(主導(dǎo))者。HCCA包含一些起始指標(biāo)(head pointer),分別指向中斷模式的“端點(diǎn)描述者”(Endpoint Descriptor)串行、已處理完畢的隊(duì)列(done queue),和“訊框起始”(start-of-frame;SOF)所代表的狀態(tài)信息。

此接口的基本建構(gòu)區(qū)塊包含:端點(diǎn)描述者(ED)和傳輸描述者(Transfer Descriptor;TD)。主機(jī)控制器對(duì)系統(tǒng)內(nèi)的每一個(gè)端點(diǎn)各別分配一個(gè)ED,TD隊(duì)列連結(jié)至特定的ED上。

雖然有了硬件的USB 2.0主機(jī)端口,但是USB的軟件驅(qū)動(dòng)程序仍然是不可或缺的。圖7是它的USB驅(qū)動(dòng)程序架構(gòu)。USB的數(shù)據(jù)處理作業(yè)是透過(guò)下列的通信層完成的:

主機(jī)控制器硬件和序列引擎(serial engine):在總線上,傳送和接收USB數(shù)據(jù)。

主機(jī)控制器驅(qū)動(dòng)程序:驅(qū)動(dòng)主機(jī)控制器硬件和處理USB通信協(xié)議。

USB總線驅(qū)動(dòng)程序和集線器驅(qū)動(dòng)程序:處理USB命令和“列舉”(enumeration)。提供一個(gè)硬件的獨(dú)立接口。

迷你驅(qū)動(dòng)程序(mini driver):處理USB裝置特有的命令。不同廠牌的USB裝置可能具有不同功能的特殊命令。

類別驅(qū)動(dòng)程序:處理標(biāo)準(zhǔn)的裝置及其命令。某一標(biāo)準(zhǔn)類別的USB裝置之類別驅(qū)動(dòng)程序都具有共同的特性,或類似的程序代碼和邏輯;例如:人機(jī)接口裝置(HID)的驅(qū)動(dòng)程序。

性能比較分析

目前在國(guó)外市場(chǎng)上TMS470、LPC2214、AT91RM9200等ARM SoC很受到歡迎。當(dāng)然,還有其它廠牌的ARM SoC也很受歡迎,譬如:Samsung、Analog等。雖然在價(jià)格上它們不見(jiàn)得是最便宜的,但是由于它們的性能優(yōu)異、容易應(yīng)用,所以擁有許多忠實(shí)的用戶。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論