思考:

1、 SOC一上電,只有一個核啟動,還是所有核都啟動?

2、如果SOC一上電,如果只有一個核啟動,那么從核啟動的時候,從核的入口是哪里?

3、啥是cold boot?啥時warm boot? 在哪些場景下會使用warm boot?

4、啥是cold reset/warm reset/primary boot/senondary boot?

說明:

1、本文以為armv8-aarch64、armv9為例、TF-A代碼為例,不討論其它硬件架構和固件軟件中的設計。

2、重點講述cold reset/warm reset/primary boot/senondary boot之間的流程和概念。

1、基礎概念

請先自行理解以下4個概念:

cold boot

warm boot

Primary boot

Secondary boot

另外還兩種配置:

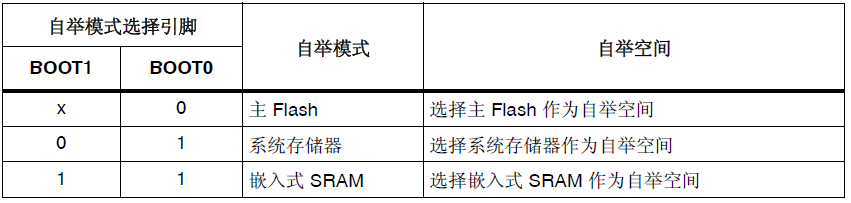

你的reset地址是可編程的,則會配置?PROGRAMMABLE_RESET_ADDRESS=1,與之對立的則是你的reset地址是不可編程的。

你在SOC啟動的時候,首先只啟動一個core,則會配置?COLD_BOOT_SINGLE_CPU=1,與之對立的則是你的SOC啟動的時候,所有core都上電了。

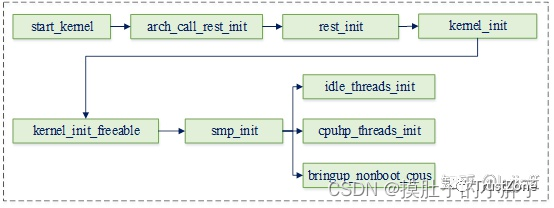

2、啟動流程

我們就假定 reset地址是可編程的、SOC啟動的時候只啟動一個core,來講解我們的boot流程:

(1)、SOC一上電,SOC給ARM Core的signal configuration會改變RVBAREL3,這里一般就是就是bootrom的首地址。即CPU一上電,Primary core的PC指向的就是RVBAREL3的地址,機器就開始啟動了。

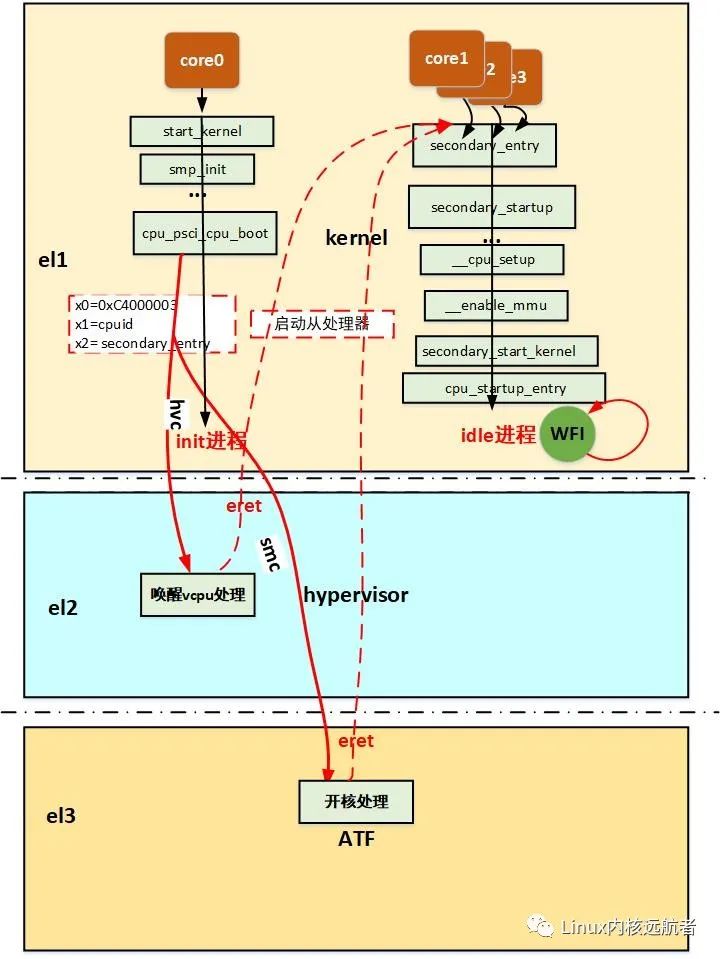

(2)、當需要Secondary Core啟動的時候,例如會走PSCI協議,【主核】進入ATF會將bl31warmentrypoint(或平臺自定義的地址)寫入到SOC寄存器,改變reset地址(改變RVBAREL3的值),然后此時SOC的PMIC給Secondary Core上電,此時Secondary Core也就發生了cold reset,PC從RVBAREL3(bl31warmentrypoint或平臺自定義函數)處開始執行.

總結(針對本文示例情況:reset地址是可編程的、cold boot的時候只啟動一個cpu):

開機一上電只有Primary Core再跑,從RVBAR_EL3處開始跑,屬于cold boot

從核啟動時,會修改reset的值,影響到RVBAR_EL3的值,然后給從核上電,此時屬于Secondary boot,仍然是cold boot.

一般會將bl31warmentrypoint設置為reset地址,即Secondary Core的啟動地址;

這個示例中沒有用到warm boot

3、ATF(TF-A)代碼的剖析

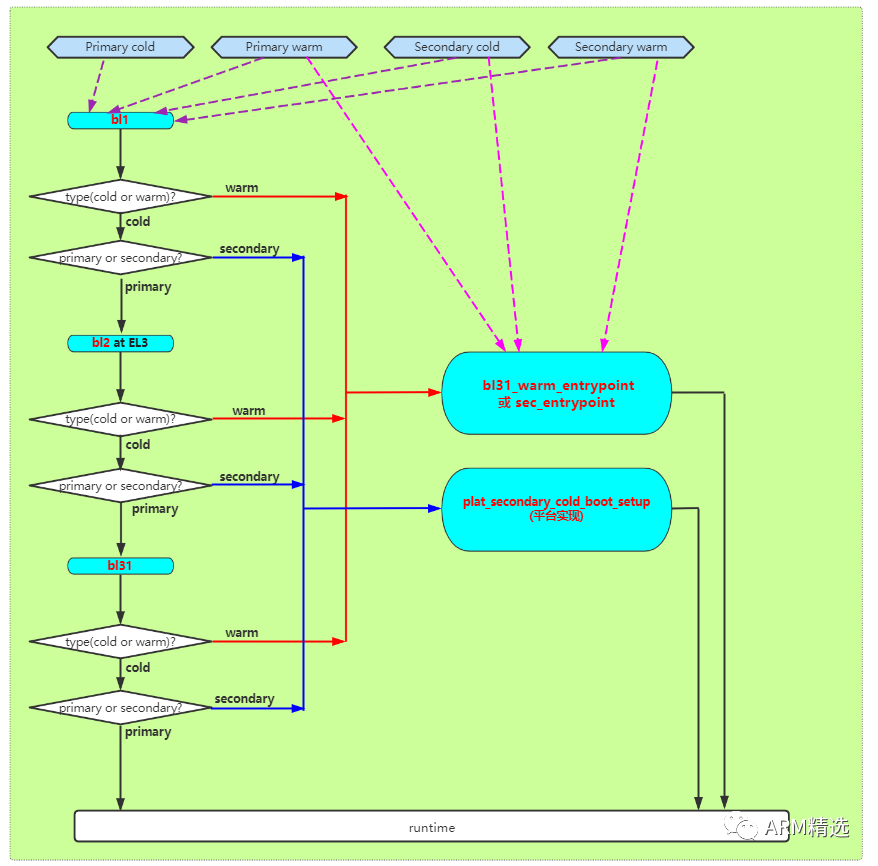

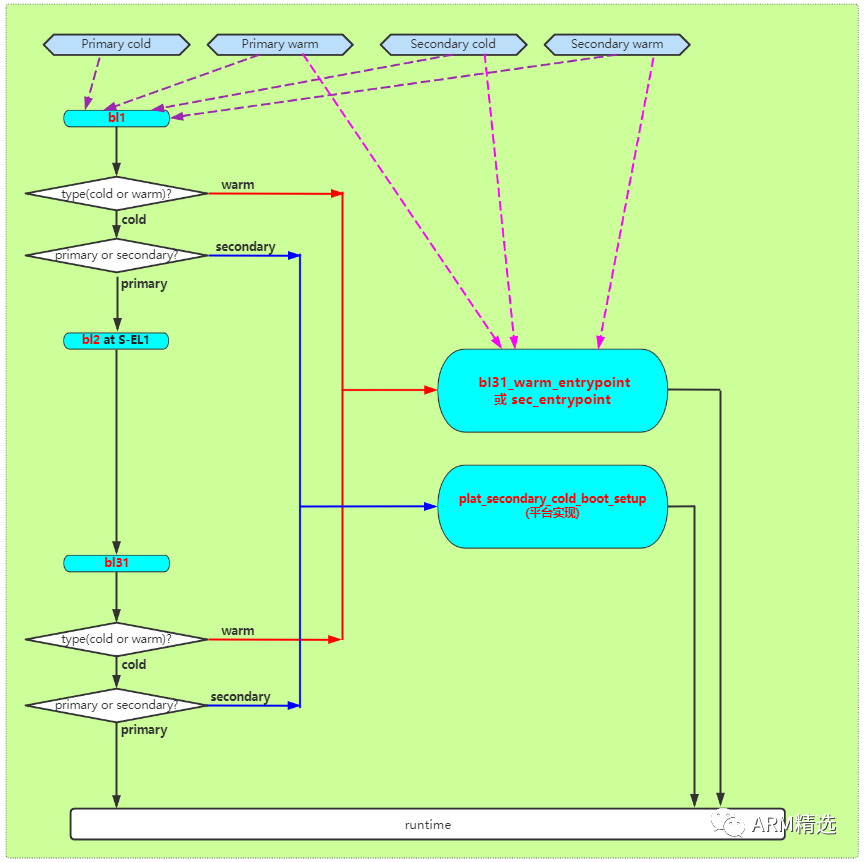

以BL1代碼為例分析,該代碼適配支持cold reset/warm reset/primary boot/senondary boot等諸多場景。

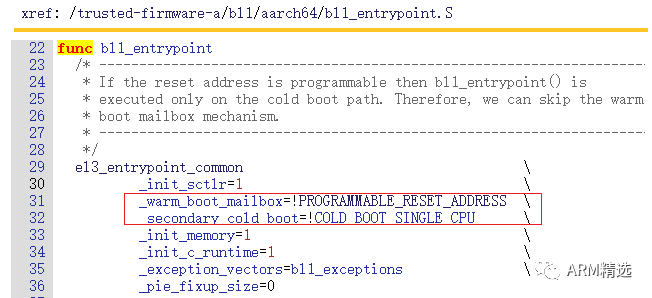

如果reset是可編程的,?PROGRAMMABLE_RESET_ADDRESS=1, 則?_warm_boot_mailbox=0,則下面這段代碼不會被編譯,無論cold boot還是warm boot都不會走?_warm_boot_mailbox。

如果reset是不可編程的,?PROGRAMMABLE_RESET_ADDRESS=0, 則?_warm_boot_mailbox=1,則下面這段代碼會被編譯,但cold boot走?do_cold_boot流程,warm boot需要走?br x0流程

.if \_warm_boot_mailbox

/* -------------------------------------------------------------

* This code will be executed for both warm and cold resets.

* Now is the time to distinguish between the two.

* Query the platform entrypoint address and if it is not zero

* then it means it is a warm boot so jump to this address.

* -------------------------------------------------------------

*/

bl plat_get_my_entrypoint

cbz x0, do_cold_boot

br x0

do_cold_boot:

.endif /* _warm_boot_mailbox */

如果SOC啟動的時候只啟動一個core,?COLD_BOOT_SINGLE_CPU=1,?_secondary_cold_boot=0,則下面代碼不被編譯, 則無論主核還是從核都不需要走?_secondary_cold_boot流程

如果SOC啟動的時候啟動多個core,?COLD_BOOT_SINGLE_CPU=0,?_secondary_cold_boot=1, 則下面代碼會被編譯,則主核走?do_primary_cold_boot流程, 從核需要走?plat_secondary_cold_boot_setup流程

.if \_secondary_cold_boot

/* -------------------------------------------------------------

* Check if this is a primary or secondary CPU cold boot.

* The primary CPU will set up the platform while the

* secondaries are placed in a platform-specific state until the

* primary CPU performs the necessary actions to bring them out

* of that state and allows entry into the OS.

* -------------------------------------------------------------

*/

bl plat_is_my_cpu_primary

cbnz w0, do_primary_cold_boot

/* This is a cold boot on a secondary CPU */

bl plat_secondary_cold_boot_setup

/* plat_secondary_cold_boot_setup() is not supposed to return */

bl el3_panic

do_primary_cold_boot:

根據以上的代碼規則,這里也畫了兩張圖:(1)、BL2 at EL3的場景

(2)、BL2 at S-EL1的場景

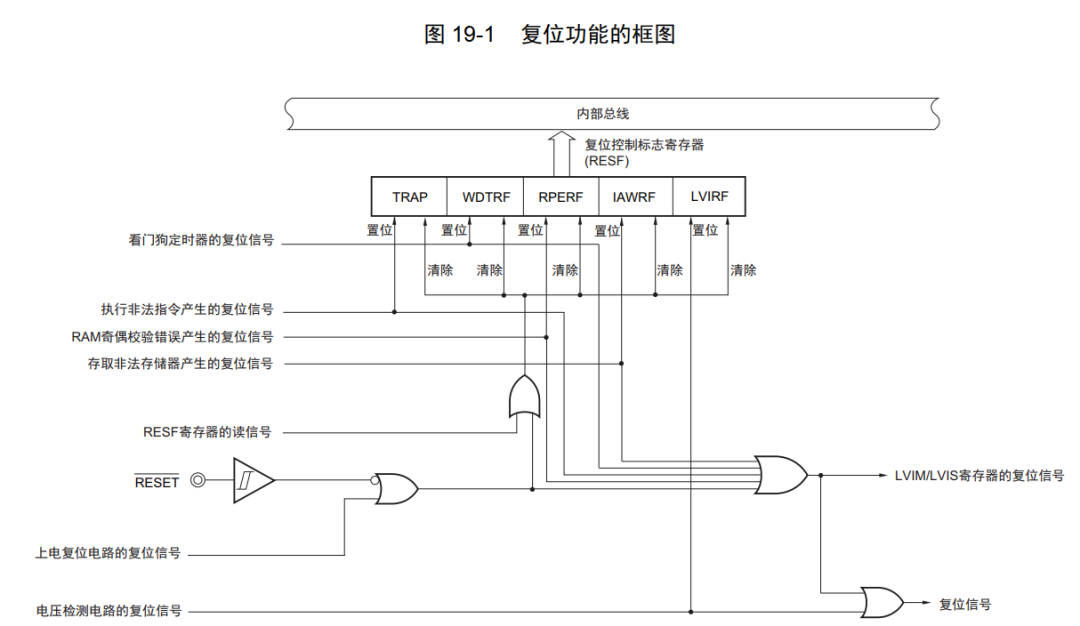

5、軟件如何判斷當前是cold reset/warm reset/primary boot/senondary boot

TF-A中定義了多核的啟動框架,如上一節框圖所示,在啟動的過程中會進行一些判斷,是cold reset還是warm reset,是primary boot還是secondary boot?那么代碼中是怎么知道這些狀態的呢?

5.1 cold reset和warm reset

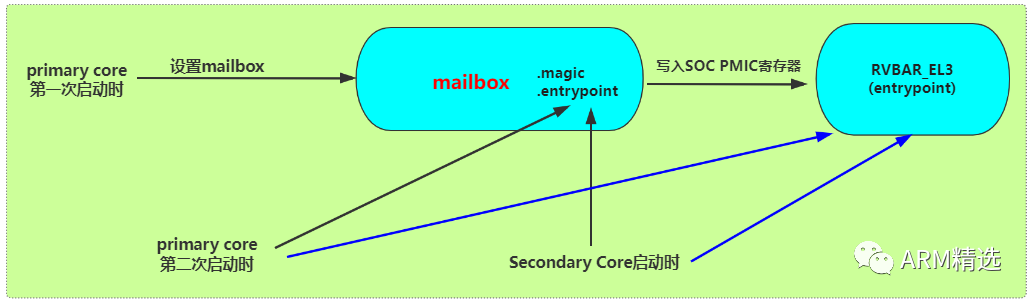

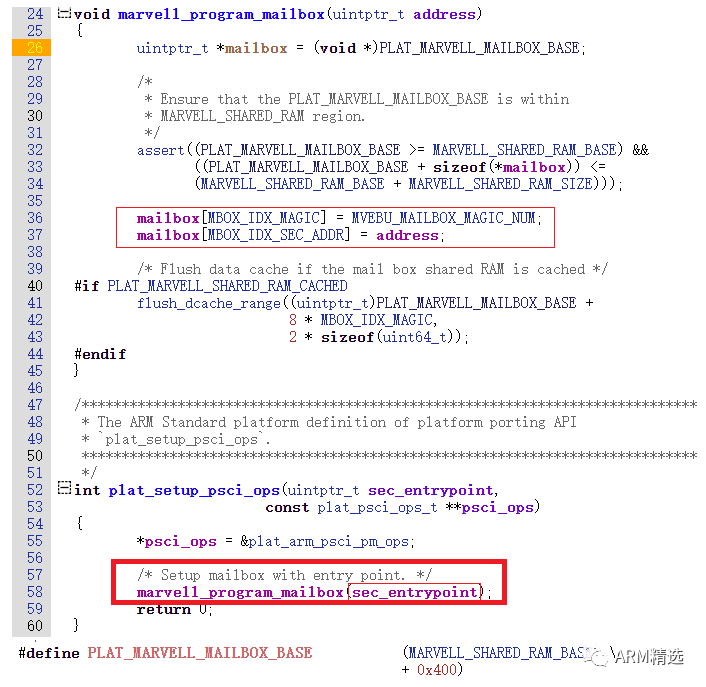

這種判斷方法由平臺實現,其實就是讀取mailbox的值。在第一個核cold boot時,會寫mailbox內存(magic,entrypoint...)在第二個核啟動時、或第一個核再次啟動時(有可能是resume喚醒時),會讀取mailbox內存,如果讀取到了符合期望的magic的值,則走warm流程,否則走cold流程。注意這里所說的warm流程,只是軟件上的warm流程,并非說當前是warm reset。

5.2 primary boot和secondary boot

這種判斷方法由平臺實現,看似也很簡單,一般而言就說讀取mpidr寄存器進行判斷。

(trusted-firmware-a/plat/marvell/armada/a8k/common/aarch64/plat_helpers.S)

func plat_is_my_cpu_primary

mrs x0, mpidr_el1

and x0, x0, #(MPIDR_CLUSTER_MASK | MPIDR_CPU_MASK)

cmp x0, #MVEBU_PRIMARY_CPU

cset w0, eq

ret

endfunc plat_is_my_cpu_primary

6、mailbox的介紹

6.1 mailbox是什么

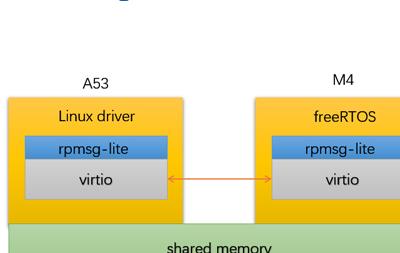

mailbox就說一塊內存,所有的core都能訪問這塊內存。第一次啟動時,core會填充mailbox,將其下次resume時的地址、secondary core的啟動地址、warm reset的地址寫入到mailbox內存中,這幾個地址其實是一個地址。同時也會將這個地址寫入到SOC PMIC寄存器中,影響到RVBAR_EL3的值。

當SOC一上電所有core都啟動的這種情況下,主核會繼續跑,從核會在SOC一上電就進入wfi狀態。當從核需要繼續啟動時,該core從BL1 BL2 BL31正常流程啟動時,會在BL1、BL2 at EL3、BL31中,強制跳轉到mailbox的地址,跳過主核已經初始化的部分;

當SOC一上電,只有一個core上電的情況下,主核繼續跑,從核未上電。當從核需要啟動時,相當于cold reset,從核會直接從RVBAR_EL3處開始跑,也就是你設置的entrypoint。

6.2 mailbox的作用

mailbox中定義了entrypoint地址,當core從BL1 BL2 BL31正常流程啟動時,會在BL1、BL2 at EL3、BL31中,強制跳轉到mailbox的地址,以跳過已初始化的部分。

6.3 mailbox的示例

其實就是定義了一塊內存,主核第一次跑時,會填充該內存。主核第二次跑時或從和跑時,檢測該內存已經填充過了,則走warm啟動流程,即強制跳轉到mailbox中的address地址。

7、具體場景的總結

串口中斷中敲擊reboot命令、或系統panic時導致的機器重啟?:在一些的SOC廠商設計中,應該是code reboot。比如在Linux Kernel中敲擊reboot,到底層還是寫的一些寄存器控制pmic(或PMU),直接給cpu下電了。然后再上電,SOC還是會給Core發送signal configuration,此時RVBAR_EL3又會變成ASIC設置的值.

Suspend和Resume?:比如我在看ATF中的海思平臺,在ATF的suspend函數,將bl31_warm_entrypoint地址寫入到了SOC PMIC的一個寄存器中(上電時,該寄存器會影響的是RVBARADDR信號)。此時系統深睡的時候,應該是Linux Kernel調用到ATF,將bl31_warm_entrypoint地址寫入到了pmu/pmic相關的寄存器中,在下一次reset時,會影響到signal configuration繼而改變RVBAR_EL3的值。然后還會給各個模塊下電(給哪些模塊下電是SOC的設計和邏輯),最后再給ARM Core下電, 這就算是深睡了。Resume的時候,也是有一些SOC的硬件行為,然后再給Core上電,那給Core上電后,一上電執行的是哪里?PC還是指向RVBAR_EL3中的地址,當然這是我們suspend的時候更改過的,其實就是bl31_warm_entrypoint

RMR_EL3?:本文中都沒有提到RMR_EL3。那么RMR_EL3是干啥的呢?這是ARM的一個feature,怎么用?是你自己的設計,隨便你。你寫RMR_EL3中的bit,就可以觸發warm reset. 一般的kernel dump、或者一些工具,就可以主動觸發RMREL3,然后去干一些活. 還有在csdn上看到一篇高通soc的啟動流程的博客,他們正常的啟動流程中,某一個鏡像跳轉到另外一個鏡像時,竟然就是寫了一些RMR_EL3,觸發warm_reset,另外一個鏡像的地址恰好就是warm reset的跳轉地址。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論