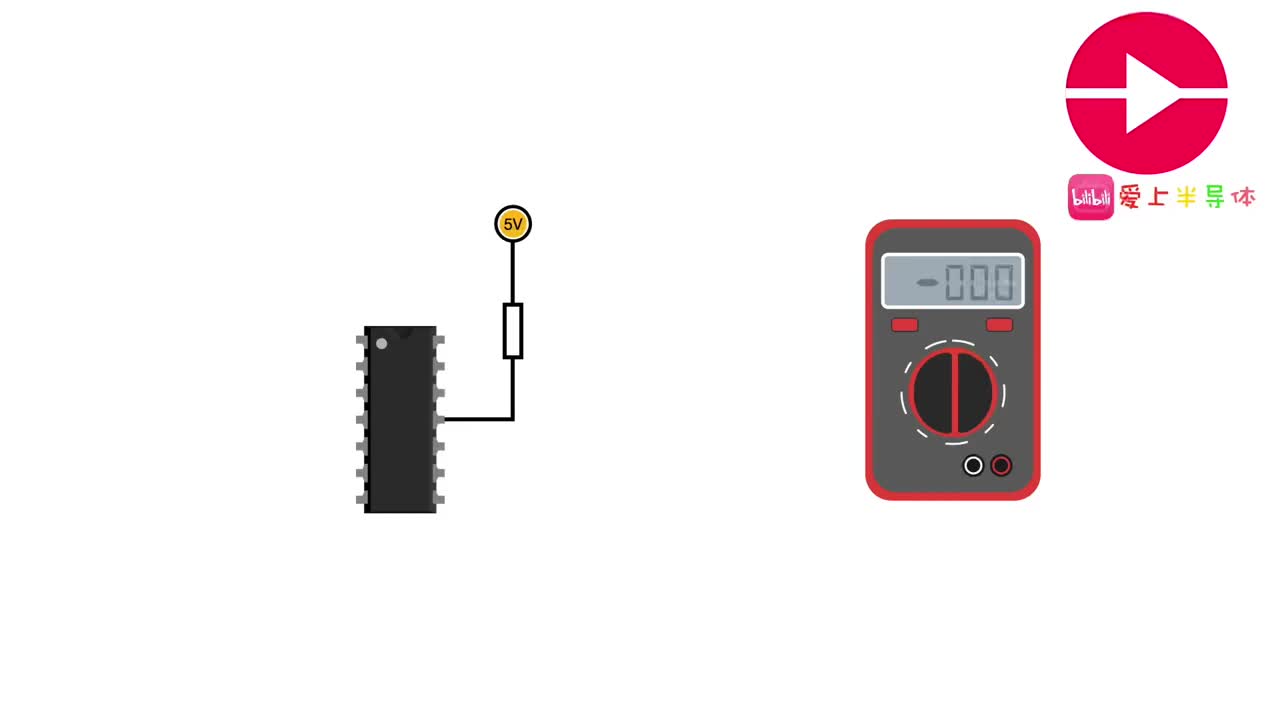

,led亮。注意到了嗎? LED 不發(fā)光的時候,上拉電阻給的電流全部灌入單片機的引腳了!如果在一個 8 位的接口,安裝了 8 個 1K 的上拉電阻,當(dāng)單片機都輸出低電平的時候,就有 40mA 的電流灌入

2013-11-18 16:23:14

使用外部可調(diào)電阻上拉(PORTX為0),管腳電壓隨著外部上拉電阻的阻值的下降而升高,當(dāng)外部可調(diào)電阻的組織大約是40K時,該管腳電壓接近Vcc供電電壓,并且降低電阻,電壓也不再升高。總結(jié)出一個規(guī)律,如果使用外部上拉電阻,該阻值應(yīng)該不能超過40K,否則該引腳的電壓將不能到達Vcc的電壓。

2011-11-15 14:10:42

的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、 長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、 從節(jié)約功耗及芯片

2017-08-28 09:27:18

的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、 長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、 從節(jié)約功耗及芯片

2017-11-16 17:14:38

下拉電阻是電阻匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。3、對于高速

2011-09-19 08:55:51

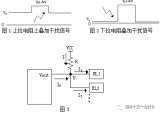

(上拉下拉電阻)所謂上拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與電源VCC相連,固定在高電平;同理下拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與地GND相連,固定

2022-01-14 08:44:01

上拉電阻與下拉電阻上拉(Pull Up )或下拉(Pull Down)電阻(兩者統(tǒng)稱為“拉電阻”)最基本的作用是:將狀態(tài)不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它

2021-12-13 07:08:22

上拉電阻與下拉電阻是如何定義的?拉電阻的作用有哪些?上拉電阻的應(yīng)用原則有哪些?

2021-10-14 07:20:37

硬件電路中的上拉電阻為什么能上拉?

2021-01-28 07:50:20

一般IIC和SPI接口建議加上拉電阻

但有時(比如SPI)不上拉,或使用內(nèi)部上拉也能正常運行。

請問,上拉主要與什么有關(guān)?是否高波特率必須強上拉?

一般上拉電阻選取多大阻值?

2023-10-28 06:23:36

經(jīng)常看到芯片設(shè)計手冊時,芯片外圍會有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時候,有個特定的范圍?對上拉電阻和下拉電阻

2021-11-12 07:28:55

上拉電阻和下拉電阻的區(qū)別及案列分析上拉電阻在一個信號未過來之前、默認(rèn)(保證)該電位的電平信號是高電平,在信號過來后如果是高電平、那么保持高電平。如果過來低電平信號、那么輸出的信號就會變成低電平。改圖

2022-01-14 06:30:35

上拉電阻和下拉電阻上拉電阻(Pull-Up)所謂上拉電阻就是用一個電阻將VCC和單片機的IO口直接連接起來,目的是當(dāng)IO在沒有輸出一個確定信號時將IO的電位鉗在一個高電平上。上拉電阻作用如下:1.當(dāng)

2022-01-25 07:23:49

下拉電阻是電阻匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。3、對于高速

2008-05-22 08:46:35

上、下拉電阻一、定義1、上拉就是將不確定的信號通過一個電阻嵌位在高電平!“電阻同時起限流作用”!下拉同理!2、上拉是對器件注入電流,下拉是輸出電流3、弱強只是上拉電阻的阻值不同,沒有什么嚴(yán)格區(qū)分4

2015-06-24 11:24:37

。 四、上拉電阻阻值選擇原則: 1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。 2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。 3、對于高速電路,過大的上拉電阻可能

2018-10-19 16:30:19

。 7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 上拉電阻阻值的選擇原則包括: 1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。 2

2019-06-27 05:55:08

門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻...

2021-12-07 08:27:59

加上拉電阻,才能使用。3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路。5、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁

2021-11-25 08:33:42

高電平。上拉電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻可能邊沿變平緩。

2021-12-01 11:15:35

上拉電阻有什么作用?如何去計算上拉電阻的阻值?51型單片機IO口有什么特點?AVR單片機IO口的輸入狀態(tài)有哪幾種?

2021-07-07 07:29:25

。2、OC 門電路必須加上拉電阻,以提高輸出的搞電平值。3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉...

2021-07-27 06:52:51

引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。(二)上拉電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠

2014-05-12 08:24:37

什么是上拉和下拉電路?上拉與下拉電路的實際作用是什么?上/下拉電阻阻值的選擇原則是什么?

2021-09-29 07:14:38

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理。也是將不確定的信號通過一個電阻鉗位在低電平。 上拉是對器件輸入電流,下拉是輸出電流;強弱只是上拉電阻的阻值

2018-10-08 15:44:08

,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。EDA365論壇網(wǎng)站|PCB論壇網(wǎng)|PCB layout論壇|PCB設(shè)計論壇|SI仿真技術(shù)

2014-11-17 10:24:15

波干擾。 8、在數(shù)字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。 四、上拉電阻阻值選擇原則 1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。 2、從確保足夠

2020-12-14 17:21:30

! -------上拉是對器件注入電流,下拉是輸出電流 -------弱強只是上拉電阻的阻值不同,沒有什么嚴(yán)格區(qū)分 -------對于非集電極(或漏極)開路輸出型電路(如普通門電路)提升電流和電壓的能力是有限

2018-06-28 06:21:54

上拉電阻的目的是什么?選擇上拉電阻阻值的原則有哪些?電阻的具體取值怎么計算的?

2021-10-11 07:43:03

ADXL313加速度傳感器用I2C通信協(xié)議與外部連接時,上拉電阻的阻值如何確定呢?看數(shù)據(jù)手冊里要參考《UM10204 I2C總線規(guī)范和用戶手冊》,修訂版2007年6月03-19日。但是沒有找到這個手冊,請問可以提供一下嗎?

2023-12-27 08:16:53

I2C信號一般需要外接上拉電阻,如果主控內(nèi)部有上拉電阻,是否可以省略外部上拉?這個是否需要上拉根據(jù)什么來決定?是根據(jù)從器件的輸入電流來決定的嗎?芯片的輸入電流參數(shù)(Ii 即input current)怎么理解,設(shè)計電路時針對這個參數(shù)需要注意什么?

2018-06-07 10:01:00

IO內(nèi)置上拉電阻的阻值是多少?所有IO都有內(nèi)置上拉電阻么,阻值是否一樣?

2024-02-21 06:17:58

Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法:

2015-05-13 17:06:07

Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法在使用 Altera 的 FPGA 時候,根據(jù)系統(tǒng)設(shè)計需要在管腳的內(nèi)部加上上拉電阻

2012-08-12 16:10:09

我現(xiàn)在遇到一個問題HDC1080 SDA引腳與STM32F031F6 PA7相連,頻率從1k到100K,上拉電阻為1K和10K時,STM32F031F6檢測的數(shù)據(jù)都是滿偏AD值,在SDA總線上加一個

2018-09-26 17:03:56

。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則 從灌電流的能力

2018-03-06 14:49:03

上拉下拉電阻的定義以及用法為什么要使用拉電阻上拉電阻阻值的選擇原則

2021-04-06 06:06:42

電阻,以提高輸出高電平的值。2、OC門電路必須使用上拉電阻,以提高輸出的高電平值。3、為增強輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。4、在CMOS芯片上,為了防止靜電造成損壞,不用的管腳

2022-01-14 07:43:57

如果在IC芯片輸入端串聯(lián)一個電阻R,起到上拉作用,R電阻值越大則電阻電壓UR就越大,IC就獲得低電平。R電阻值越小則電阻電壓UR就越小,IC就獲得高電平。這樣的接法不就起到上下拉的作用?為什么都說上拉電阻接Vcc端,下拉電阻接地?所謂的上拉是指UR變大還是IC輸入電壓變大?

2018-04-13 11:19:32

在選擇上拉電阻值時,要根據(jù)系統(tǒng)實際情況在功耗和速度上兼顧。

從IC(MOS工藝)的角度,分別就輸入/輸出引腳做一解釋。

1、對芯片輸入管腳,若在系統(tǒng)板上懸空(未與任何輸出腳或驅(qū)動相接)是比較危險

2023-05-18 17:30:56

fpga管腳接上拉電阻,此時我不能將此管腳配置為輸出0,但可以輸出1,不知道這是為什么,還請高手解答!

2014-04-09 15:00:25

外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。8、在數(shù)字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。四、上拉電阻阻值選擇原則

2018-11-30 11:55:14

上拉電阻在單片機電路中的作用主要有以下幾點:

限制電流的流動:在單片機電路中,電阻的作用之一是限制電流的流動。電阻的阻值越大,通過電阻的電流就越小,反之亦然。通過選擇不同阻值的電阻,可以控制電路中

2023-09-05 16:45:53

不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 上拉電阻阻值的選擇原則包括: 1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。 2、從確保足夠的驅(qū)動電流

2019-09-06 15:19:36

電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻可能邊沿變平緩。綜合考慮

2011-11-02 10:20:11

干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。8、在數(shù)字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。四、上拉電阻阻值選擇原則1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻

2011-07-28 09:58:10

選擇時應(yīng)該注意哪些問題,又該按照怎樣的標(biāo)準(zhǔn)來進行選擇呢?下面大家就一起來學(xué)習(xí)一下吧。 對于上拉電阻的選擇,最重要的就是要結(jié)合開關(guān)管的特性與下級電路的輸入特性。總的來說需要考慮以下幾個因素: 1 驅(qū)動

2016-01-20 10:39:09

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2020-08-14 06:35:49

大家好,我使用的是DSPIC33 FJ256MC710A DSP。我無法理解如何選擇IO引腳上的上拉或下拉電阻。我查閱了數(shù)據(jù)表,它指出:可選擇的開放漏極、上拉和下拉。在輸入輸出引腳的參考指南中,我

2019-08-07 14:05:23

1:僅僅一根線路就可能發(fā)生短路(左),一個上拉電阻就可以防止輸入管腳懸空,同時防止不必要短路現(xiàn)象的發(fā)生那么我們怎樣選擇合適的電阻呢?正如大多數(shù)工程的問題一樣,答案取決于你的應(yīng)用。首先我們以極端條件0

2018-11-30 09:12:02

上拉電阻的設(shè)定的原則有哪些?下拉電阻的設(shè)定的原則有哪些?對上拉電阻和下拉電阻的選擇主要考慮哪幾個因素?

2021-06-08 06:57:54

的能力是有限的,上拉和下拉電阻的主要功能是為集電極開路輸出型電路提供輸出電流通道。上拉是對器件注入電流,下拉是輸出電流;強弱只是上拉或下拉電阻的阻值不同,沒有什么嚴(yán)格區(qū)分。當(dāng)IC的I/O端口,節(jié)點為

2019-10-11 08:30:00

上拉電阻和下拉電阻上下拉電阻的出發(fā)點在正常工作或單一故障狀態(tài)下,管腳均不應(yīng)出現(xiàn)不定狀態(tài)從功耗角度考慮,在長時間的管腳等待狀態(tài)下,管腳端口的電阻不應(yīng)消耗太多電流上下拉的選擇從抗擾角度出發(fā),信號端口優(yōu)選

2022-01-14 07:42:58

:一般用途為1kΩ至10kΩ。如果你有一個低功耗的用例,例如電池供電的設(shè)備,則為10kΩ至100kΩ。最后要考慮的是許多微控制器都有內(nèi)部上拉電阻,可以通過代碼打開。請務(wù)必查看數(shù)據(jù)表,以確定內(nèi)部電阻值是否適合您的應(yīng)用。如果沒有,則必須使用外部上拉電阻。

2018-11-09 09:14:56

什么是上拉電阻?上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。為什么需要上拉電阻?一般作單鍵觸發(fā)使用時,如果IC本身沒有內(nèi)

2021-08-12 13:35:38

會產(chǎn)生浪涌,特別是火車上的車載電視啊等,電源上要加一些保護裝置,如RClamp0504F 等能將電壓嵌位10、一般RST,CLK 管腳接上拉電阻選擇上拉電阻阻值的原則包括:1、從節(jié)約功耗及芯片的灌電流

2014-08-21 09:56:08

的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻

2011-06-02 16:03:48

的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2、從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻可能

2012-06-10 21:25:15

前言:在一張原理圖中無論時上拉還是下拉都是非常普遍的,轉(zhuǎn)載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉的原理與應(yīng)用2者共同的作用是:避免電壓的“懸浮

2022-01-14 08:28:26

引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 另外,上拉電阻阻值的選擇原則包括:1.從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。2.從確保足夠的驅(qū)動電流考慮應(yīng)當(dāng)足夠

2017-05-22 18:49:54

我想在 LPC1114FHN33 的標(biāo)準(zhǔn) I/O 引腳上安裝一個外部下拉電阻。內(nèi)部的下拉電阻和上拉電阻可以通過設(shè)置寄存器來切換,但這是因為我們要將邏輯固定為“L”,直到反映出下拉或上拉。 所以我有一個問題。請告知電源電壓為3.3V時不損壞LPC1114的外部下拉電阻值范圍。

2023-04-20 08:30:38

電路設(shè)計的上拉/下拉電阻阻值應(yīng)該怎樣選?隨便弄一個,如4.k、10k的成嗎?

2023-10-28 07:37:23

確定上拉電阻值時需要考慮哪些注意事項?穩(wěn)定可靠的I2C通信的設(shè)計計算公式

2021-05-25 06:35:11

時能低于0。8V即可。當(dāng)輸出高電平時,忽略管子的漏電流,兩輸入口需200uA,200uA x15K=3V即上拉電阻壓降為3V,輸出口可達到2V,此阻值為最大阻值,再大就拉不到2V了。選10K可用。【最大

2015-06-26 14:26:17

各位好,我在查看USB協(xié)議時看到是需要在DP或DM上外接上拉電阻來選擇速度模式的,且F1系列的評估板也是如此,如圖

但當(dāng)我查看H7的評估板時就沒看到外部上拉電阻。如圖

是內(nèi)部集成了嗎?是下圖那

2024-03-08 06:54:40

大家好,我在設(shè)計一個使用PIC18F14K50的PCB,我在大多數(shù)I/O引腳上使用外部上拉電阻,但是我的空間已經(jīng)用完了。所以我想知道PIC18F14K50中的內(nèi)部上拉電阻值多少,以及它是否值得

2019-07-08 09:06:36

按鍵輸入已經(jīng)設(shè)了內(nèi)部上拉沒接外部上拉電阻為什么電壓只有1.44v?

2020-06-18 07:02:11

請問用TMS320C5515的GPIO口模擬I2C總線需要接外部上拉電阻嗎?需要的話阻值為多少比較合適呢?

2019-10-28 09:37:43

輸出端的電位。示例:51單片機中除了P0口有兩個場效應(yīng)管,其余三個端口P1,P2,P3都有上拉電阻。如下圖所示:作用除此之外,上拉電阻作用還有很多。比如CMOS芯片上輸入的電阻一般很大,為了防止靜電造成損壞,不用的管腳不能懸空,一般會接上拉電阻來保護內(nèi)部電路;加上拉電阻還能提高輸出端的電流

2022-01-25 06:28:33

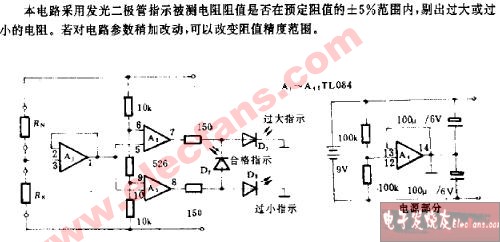

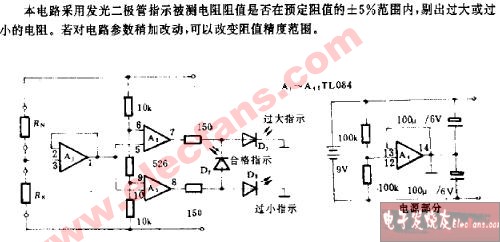

電阻阻值選擇電路

2009-02-06 11:53:40 707

707

電阻器阻值的簡易測量

一般的電阻器的阻值可用萬用表進行測量,測量前應(yīng)先根據(jù)電阻器的標(biāo)稱阻值選擇好電阻測量擋,然后將兩測試表筆短接進行電阻擋的校零。測

2009-06-15 19:40:12 1331

1331 上拉電阻的作用及阻值的選擇原則

2018-03-21 11:17:55 2

2 對于驅(qū)動TTL集成電路,上拉電阻的阻值要用1~10K之間的,有時候電阻太大的話是拉不起來的,因此用的阻值較小。但是對于CMOS集成電路,上拉電阻的阻值就可以用的很大,一般不小于20K,通常用100K

2018-05-26 09:16:09 23825

23825

本文首先介紹了上拉電阻阻值的選擇原則,其次介紹了上拉電阻阻值計算原則。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2018-08-30 18:37:13 19406

19406 制動電阻的選擇除受到變頻器專用型能耗制動單元最大允許電流的限制外,與制動單元也并無明確的對應(yīng)關(guān)系,其阻值主要根據(jù)所需制動轉(zhuǎn)矩的大小選擇,功率根據(jù)電阻的阻值和使用率確定。

2021-01-27 16:00:11 5877

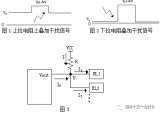

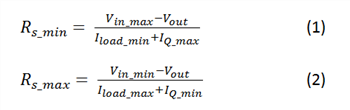

5877 具有一個能夠支持寬輸入電壓范圍,并且能夠?qū)崿F(xiàn)低壓降運行的電壓基準(zhǔn)。

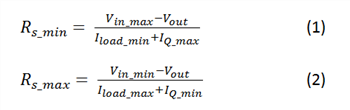

為了使支路電流保持在器件的工作電流范圍內(nèi),你必須選擇一個電阻值范圍介于方程式1與2所定義電阻值之間的外部電阻器:

通過以即時

2022-01-21 14:17:00 522

522

案例背景 某樣品貼片電阻在實際應(yīng)用環(huán)境中出現(xiàn)故障,經(jīng)排查為電阻值降低導(dǎo)致失效。 分析過程 外觀分析 說明: 對樣品電阻進行外觀檢測,電阻三防漆有氣泡狀態(tài),整體電阻未見異物附著。 X-Ray分析 說明

2023-01-30 15:39:12 1193

1193 如何去選擇和使用固定電阻器?固定阻值電阻器選用原則? 固定電阻器(也稱為固定阻值電阻器)是一種常見的電子元器件,用于限制電流、分壓、和保護電路等方面。在選擇和使用固定電阻器時,需要考慮其阻值、功率

2023-12-20 10:45:56 438

438

電子發(fā)燒友App

電子發(fā)燒友App

評論