當前,數字影像設備種類繁多,視音頻處理硬件與軟件技術高度發達[2],為數字視頻的流行起到了推波助瀾的作用。在很長的一段時間內,圖像處理將成為信息技術的前沿領域和熱門課題。圖像處理技術的應用取得了良好的社會效益和經濟效益,其原因主要在于計算機技術以及大規模集成電路技術的發展與成熟,使得利用嵌入式系統作為視頻圖像的輸入輸出處理正逐漸成為主流,硬件解決方案也從專用處理芯片、DSP發展至FPGA,極大地提高了系統的靈活性、小型化。

人的視覺信息占所有獲得信息總量的70%以上,特別是隨著現代科學技術的進步和社會發展,人們所接觸的信息量也在不斷增加。所以,顯示技術的重要性越來越大。而視頻技術[1]也經歷了由模擬視頻向數字視頻的發展,在人們日常生活中的應用越來越廣泛,例如電視電話會議、高清數字電視(HDTV)、移動視頻及3G可視通信等。

1 系統設計

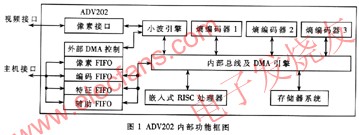

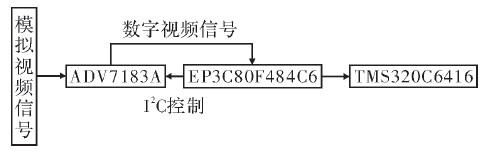

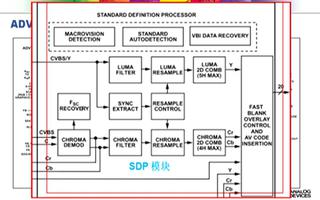

利用單片機MSP430F169與解碼芯片ADV7183B的配置,使得整個視頻解碼系統可以靈活地根據輸入視頻源進行相應的配置以輸出不同的數字視頻數據。MSP430F169的最高運算速度達到8 MIPS,具有易操作、低功耗等特點[3-4],特別是其可通過I2C接口與解碼器進行數據傳輸,以實現對不同格式視頻輸入源的解碼。而ADV7183B是一款綜合的視頻解碼芯片[5-6],它能夠自動將一種兼容國際標準NTSC或PAL的模擬視頻基帶信號轉換成另一種兼容8 bit/16 bit CCIR656的YCrCb型4:2:2的數字視頻數據,其靈活的數字式輸出接口能夠在基于緩存器結構和行鎖時鐘的系統中完成視頻解碼和轉換功能。視頻解碼系統的硬件框圖如圖1所示。MSP430F169是主控芯片,針對不同的模擬視頻源,利用C語言編程,對解碼芯片ADV7183B的寄存器進行相應的配置,產生符合要求的數字視頻數據及行、場信號,以便于視頻后處理系統進行濾波、顯示。

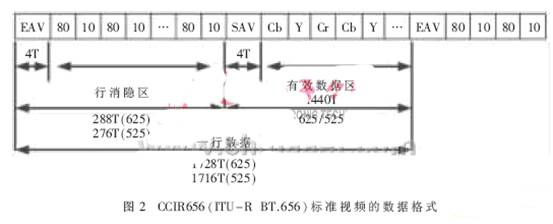

數字視頻數據是把模擬視頻信號解碼為Y、U、V分量后,將其分別進行A/D量化采樣,轉換為數字視頻流,時間上也按上面的順序依次輸出。這里,采用的是成立于1927年的國際無線電咨詢委員會CCIR656(Consultative Committee of International Radio)標準[7-8],也稱為ITU-R BT.656。該標準規定:Y、U、V 3個分量的抽樣頻率分別為13.5 MHz、6.75 MHz、6.75 MHz。采用線性量化,每個樣點的量化比特用于演播室為10 bit,用于傳輸則為8 bit。Y、U、V 3個分量樣點之間比例為4:2:2,數據格式如圖2所示。

圖2中,T為采樣時鐘37 ns(27 MHz);SAV為有效視頻開始的定時基準標志碼;EAV為有效視頻結束的定時基準標志碼;每個基準信號由4個周期的數據組成,格式為FF,00,00,XY,以16進制表示,前3個為固定的前綴,第4個字用來定義奇偶場、場消隱和行消隱信息。在消隱期間,傳輸80 H,10 H,80 H,10 H;在有效期間,按Cb,Y,Cr,Y,Cb,Y順序傳送。

2 ADV7183B的設置

根據實際需要,這里采用了Analog Device公司的ADV7183B芯片作為系統的解碼芯片。它是一款綜合的視頻解碼芯片,能夠處理NTSC或PAL制式下的CVBS、S-Video、YPrPb 3種格式的輸入視頻源,從而廣泛地應用于放映機、數字電視、DVD、游戲機等電子產品。ADV7183B的主要特點[9]如下:

(1)內部帶有行鎖定系統時鐘(LLC)和自適應數字線長跟蹤(ADLLT)電路,可以提供雙重視頻鎖定功能;

(2)具有實時時鐘、信息輸出功能以及3行色度梳狀濾波器;

(3)具有完整的AGC和箝位控制功能,可對色度、亮度、飽和度和對比度進行編程視頻調節;

(4)可自動進行NTSC或PAL檢測,且有12個模擬視頻輸入信道;

(5)可設置為二線連續雙向端口模式,并與I2C兼容;

(6)支持不同模式的視頻輸入和16 bit寬度總線數字輸出;

(7)輸入峰峰值為0.5 V~2 V。

通過不同的配置,ADV7183B的6個模擬視頻輸入信道可支持6個CVBS輸入信號、3個S-video輸入信號和2個YPrPb構成的模擬視頻輸入信號,可由寄存器INSEL控制輸入源的類型和信道。此外,ADV7183B支持3種輸出接口模式:兼容LLC的同步像素接口、CAPI接口和SCAPI接口,默認模式為兼容LLC的8 bit CCIR656數據。

在電路設計時,ADV7183B的工作晶振為27 MHz,ALSB為地址片選端口,由于軟件程序的設計需要,將其接地,置為低電平。CVBS接入AIN5腳,S-Video接入AIN1和AIN4腳,YPrPb則接入AIN2、AIN3和AIN6腳;P0~P15為數據輸出端;LLC1、LLC2為時鐘輸出端口,當為8 bit數據輸出時,LLC1為27 MHz,LLC2為13.5 MHz。而當為16 bit數據輸出時,LLC1和LLC2均為13.5 MHz;HS為行同步信號輸出,VS為場同步信號輸出,FIELD為奇偶場信號輸出。當系統通電后,板上的2個LED燈會交替閃爍10次,提示用戶可通過按鍵進行輸入源信道的選擇操作:SW1鍵選擇S-Video視頻源輸入,SW2鍵選擇YPrPb視頻源輸入,若不操作則默認CVBS視頻源輸入。

由于MSP430F169和ADV7183B均有自帶的I2C模塊,利用I2C總線協議,系統通過中斷程序進行解碼芯片的各種寄存器配置,從而產生YCrCb型4:2:2的數字視頻數據,軟件流程圖如圖3所示。

首先,初始化時鐘和傳輸模式,使MSP430F169工作在所需的模式下;其次,初始化I2C功能,使其準備將從機地址發送到I2C總線上,等待總線上的從機應答,若無應答則重復發送,若有應答則通信初始化并開中斷,發送所需配置的寄存器地址和數據[10-11]。需要注意的是,在每次發送數據前都要初始化主機模式和傳輸模式的設置,因為每次發送完數據后,這兩個標志位都會被自動清零。

為了使ADV7183B正常工作,幾個主要寄存器的配置內容如下:

(1)輸入選擇寄存器INSEL,地址為0x00。根據外部接口情況,用戶可通過設置這個寄存器選擇模擬視頻源的輸入通道和輸入模式,即選擇通過CVBS、S-Video或YPrPb輸入。在該系統中,CVBS信號由AIN5輸入,則寄存器內容設置為0x04;S-Video信號的Y接入AIN1,C接入AIN4,則寄存器內容設置為0x06;YPrPb信號的Y接入AIN2,Pb接入AIN3,Pr接入AIN6,則寄存器內容設置為0x0A。同時,未連接的其他輸入通道管腳必須接地。

(2)輸出模式選擇寄存器OF_SEL,地址0x03。通過設置此寄存器,用戶可控制輸出數據為8 bit或16 bit。不過,此寄存器必須和像素時鐘寄存器(LLC_PAD_SEL,地址0x8F)一起設置。當輸出16 bit數據時,像素時鐘為13.5 MHz;而當輸出8 bit數據時,像素時鐘則為27 MHz(默認設置)。所以程序中,8 bit輸出時,0x03設置為0x0C,0x8F設置為0x00;16 bit輸出時,0x03設置為0x00,0x8F設置為0x50。

(3)ADC低功耗控制寄存器,地址0x3A。這個寄存器可以選擇ADC的工作個數。在CVBS模式下,ADC1和ADC2低功耗,即不工作;在S-Video模式下,ADC2低功耗;而在YPbPr模式下,3個ADC全部工作。同時,還需要配置相應的寄存器地址是0xC3和0xC4,這2個寄存器設置了3個ADC所連接到的管腳。根據外部的模擬輸入源,CVBS模式時,ADC0連接AIN5,則0xC3設置為0x05,0xC4設置為0x80;S-Video模式時,ADC0連接AIN1,ADC1連接AIN4,則0xC3設置為0x41,0xC4設置為0x80;YPrPb模式時,ADC0連接AIN2,ADC1連接AIN3,ADC2連接AIN6,則0xC3設置為0x32,0xC4設置為0x86。

(4)行、場同步信號的相關寄存器,一般采用默認設置即可。

3 實驗結果

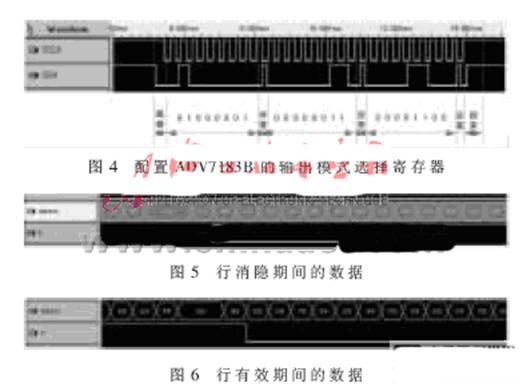

在系統調試時,采用了一個彩色數字攝像頭作為視頻輸入源,即輸入CVBS格式的模擬視頻信號,通過邏輯分析儀捕獲輸出管腳的波形,觀測相應的信號和輸出數據。通過不斷修改程序,最終實現視頻圖像的采集、顯示。圖4是通過MSP430F169設置ADV7183B的輸出模式選擇寄存器的波形。可見,時序滿足標準的I2C總線協議的傳輸時序:起始—從器件地址(0x40)—應答—從器件的寄存器地址(0x03)—應答—寫數據(0x0C)—應答—結束。圖5和圖6是解碼后的視頻數據。在圖5中,根據固定前綴FF 00 00 F1可知,F1(1111 0001)所包含的信息是表示行由0跳變為1,場由0跳變為1,傳輸數據進入的是行和場的消隱期。而圖6中,由固定前綴FF 00 00 80可知,80(1000 0000)所包含的信息是表示行由1跳變為0,場由1跳變為0,傳輸數據進入的是行和場的有效期。由此表明,視頻解碼系統輸出的視頻數據符合CCIR656標準,達到了設計要求。

綜上所述,本視頻解碼系統利用MSP430F169進行解碼芯片ADV7183B的設置,具有低功耗、小巧靈活等特點。同時,作為視頻輸入前端,將彩色攝像頭的模擬視頻源轉換成16 bit的YCrCb型4:2:2數字視頻數據,并進行格式轉換、濾波等處理后,通過DVI接口在CRT上清晰顯示,達到了設計要求,能夠為相應的視頻后處理設備(如DSP、FPGA等)提供良好的數字視頻數據。

電子發燒友App

電子發燒友App

評論