1 引言

??? 隨著嵌入式微處理器和嵌入式操作系統的發展,嵌入式系統在通訊、控制和消費電子等諸多領域得到了廣泛的應用。嵌入式系統通常是面向特定應用的嵌入式CPU,與通用型的最大不同就是嵌入式CPU大多工作在為特定用戶群設計的系統中,它通常都具有低功耗、體積小、集成度高等特點,能夠把通用CPU中許多由板卡完成的任務集成在芯片內部,從而有利于嵌入式系統設計趨于小型化,以動能力增強,與網絡的耦合也越來越緊密。

??? 本文利用ARM嵌入式系統構造微型化的工程地震儀雛形,以滿足特定條件的工作需要,降低功耗,節省能源以延長工作時間,減小儀器尺寸和重量,使儀器更為輕便。

2 現有工程地震儀簡介

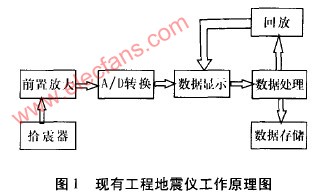

??? 工程地震儀應用于地基、路基與基礎工程檢測;隧道工程檢測;大中型水庫的運行觀測;橋梁工程檢測;環境與地質災害檢測與評價等工程領域的地震檢測任務l2 。一般來講工程地震儀器利用錘擊、電火花或爆炸等作為激發震源,硬件上由前置放大器,數據采集卡,A/D轉換器,工控機(便攜式微機)等部分組成。而數據采集,數據處理,分析軟件都存儲在工控機內,可以隨時處理現場所采集的原始數據,發現問題及時處理。其功能一般有:瞬態多點端雷波勘探淺層反射測量淺層折射測量波速(剪切波)測量多波高密度地震映像樁基檢測土建工程質量檢測場地常時微動測量震動爆破測量。如圖1 所示

其中,數據的顯示,數據的處理和存儲都是用工業控制微機來完成的,下面是一款典型的現有工程地震儀器工業控制微機的硬件配置:

CPU :PIII 500MHz

內存:128MB

硬盤:不小于40GB

光驅:內置

顯示屏:800×600點陣VGA液晶顯示屏(TFT真彩)

輸入設備:觸摸屏輸入、精致小鍵盤、光電鼠標

接口:雙串一并、雙USB口、鼠標口、鍵盤口等標準口

移動存儲:256M電子U盤

??? 現有工程地震儀由于工控機功耗較高,體積尺寸大,野外攜帶不很方便,尤其是當野外工作需要電池支持時,受功耗的影響工作時間可能受一定的限制。對于某些特定場合,如煤礦井下作業時要考慮到防爆因素,必須在儀器外裝加防爆外殼,而防爆因素與功耗,體積等密切相關,這便要求有相對功耗小,體積重量小的微型工程地震儀的出現。

3 系統硬件設計

3.1 工作原理

??? 系統硬件主要分為ARM處理器模塊、協處理器FPGA模塊、預處理和A/D模塊、通用外設模塊4個部分,ARM處理器和現場可編程門陣列(FP.GA)共同組成監控系統的核心處理單元。現場勘探檢測時,可利用爆炸的方式作為激發震源,當一次爆炸啟動后,傳感器信號通過模擬開關,先經過前置放大和濾波等預處理,獲取符合A/D轉換芯片要求的信號,經過A/D轉換,進入FIFO,然后由嵌入式微處理器讀取并處理數據,然后將數據存儲到SIM卡或USB存儲設備中。在A/D轉換模塊中,采用多路模擬開關,可完成大數量點的數據采集。FPGA是整個系統的控制中心,控制采集通道的切換,A/D轉換芯片的啟停,轉換后的數據在FIFO中的存放以及向主處理器$3C2410A產生中斷請求讀取FIFO中的數據。如圖2所示。

3.2 硬件介紹

3.2.1 協處理器模塊

???? 系統的協處理器采用Xilinx公司的FPGA,型號為SPARTANIIE XC2SIOOE。該芯片共有2700個邏輯單元,10萬個邏輯門,片內塊RAM為40KB。其具體實現以下功能:

· A/D模塊讀/寫時序控制;

· 生成FIFO,其主要功能是存儲經A/D編碼的數據:

· 提供ARM處理器控制信號。

FPGA芯片分4部分來實現上述功能:

(1)內部控制信號產生器

FPGA對50 MHz時鐘分頻產生A/D芯片采樣時鐘Sampleclk和ARM處理器外部時鐘Sysclk;Sysclk經鎖相環電路(PLL)后產生ARM處理器工作所需的時鐘信號 。

(2)ARM控制器

提供ARM處理器正常工作所必須的各種控制信號;實現ARM處理器地址總線、數據總線和外部中斷信號接入 。

(3)A/D控制器

控制A/D模塊的數據轉換。產生A/D轉換起始信號(/HOLD),檢測數據轉換完成信號(/EOC),產生FIFO寫入信號,實現數據轉換通道選擇。

(4)FIFO存儲器

生成FIFO,完成A/D轉換數據的存儲。

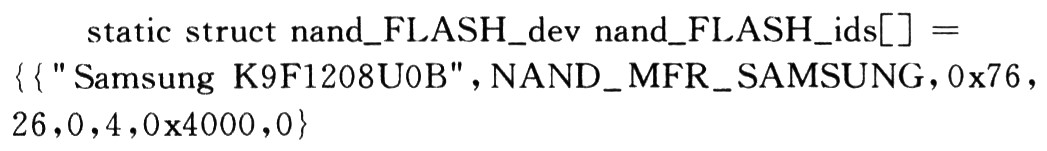

3.2.2 ARM處理器模塊

??? ARM 處理器模塊由FLASH、SDRAM 和s3C2410共同構建。系統選用Samsung公司的K9F1208UOA構建8位FLASH 存儲器系統。K9F1208UOA單片容量為64 MB;選用兩片單片容量32 MB。數據寬度為16位HY57V561620CT,并聯構建32位SDRAM存儲器系統,共64 MB的SDRAM空問可以滿足嵌入式操作系統和各種復雜算法的運行要求。ARM處理器對各模塊的控制則是通過底層驅動控制協處理器FPGA產生各種控制信號來實現。

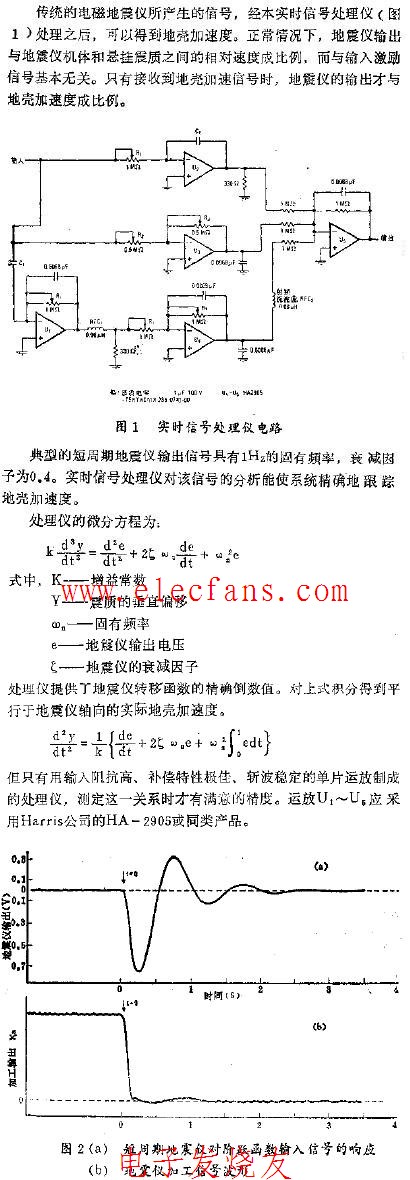

3.2.3 預處理和A/D模塊

??? 傳感器傳播的模擬信號比較微弱,需要經過前置放大等預處理后方具備數據有效性。預處理主要是由前置放大電路構成,A/D模塊主要由模擬開關和A/D轉換芯片構成。模擬開關采用AD公司的AD7506,可實現12通道數據采集。A/D轉換芯片采用CIRRUS公司的CS5381,是120dB、192kHz高性能立體聲24位Σ 一△ A/D變換器,內置雙極性電路構成的混合集成轉換顯片,具有外接元件少,功耗低,精度高等特點,并且具有自動校零和自動極性轉換功能,只需外接少量的阻容件即可構成一個完整的A/D轉換器。

3.2.4 接口和顯示模塊

??? 包括常用的接口和顯示器件。接口包括常用的串口等,用以進行數據的外部存儲。顯示模塊主要包括構成操作的LCD和觸摸屏等外圍顯示設備。

4 嵌入式系統軟件設計

??? 軟件部分分為FPGA控制程序和ARM處理器兩部分,FPGA用VHDL來設計,基于s3C2410A的軟件設計主要任務有數據采集的驅動程序,操作系統的移植以及上層應用軟件的設計。嵌入式操作系統應用WinCe.net,上層應用軟件開發使用Em-bedded Visual C++,底層驅動和ARM處理器的調試則使用c語言。

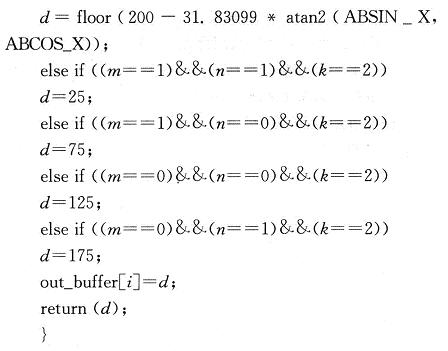

???? 系統開始工作后ARM處理器和FPGA協處理器中的FIFO開始初始化。經A/D轉換后的數據存入對應的FIFO中。FIFO中的數據容量達到一定限度即產生巾斷,ARM處理器中的主程序產生中斷等待線程;一旦中斷產生則進入中斷服務程序,讀取數據,之后進入ARM系統進行相應的處理,然后存儲到存儲設備。如圖3所示。

?4.1 嵌入式操作系統WindowsCE.net的裁減

??? 使用集成開發環境Platform Builder根據提示完成操作系統鏡像的定制、編譯與調試工作,并可在此環境巾進行應用軟件、驅動程序的開發。在ARM中植入Windows CE.net平臺,首先根據目標設備的硬件配置及需要,對Windows CE.net進行基本定制,開發并安裝驅動程序,增加必要的特性,生成鏡像文件,通過JTAG將bootloader寫入flash后,通過網卡將鏡像文件下載到目標設備中,進行調試 同時要導出SDK,以備后面用EVC開發應用程序。

4.2 數據采集驅動程序

???? 在數據采集中,主要對外部I/0口的訪問,Wince的BSP都實現WRITE—PORT—UCHAR和READ— PORT— UCHAR函數。訪問方式采用中斷方式。WinCE把中斷處理分為兩部分中斷服務例行程序ISR和中斷服務線程,用戶的中斷處理主要在IST中完成 。。這里采用基于中斷方式的非標準驅動,要實現兩個步驟:編寫中斷服務線程IST和注冊中斷服務線程。中斷信號由FIFO經FPGA不斷產生,每發生一次中斷,運行在核心態的中斷服務例行程序就調用一次IST。

4.3 中斷控制

??? 系統如果對A/D轉換數據采用實時讀取的方式,則必然導致ARM處理器工作效率較低,所以在電路設計時采用中斷方式。A/D模塊輸出數據以循環方式分別寫入FIFO中。一旦FIFO中可使用數據容量減小到一定限度則產生中斷,ARM處理器進入中斷服務程序并讀取FIFO中的數據。

4.4 上層應用軟件

上層應用軟件的開發包含以下模塊:

數據采集系統:實施采集的控制和監測。

數據處理系統:簡單處理采集到的數據,如數字濾波等。

圖形顯示系統:將采集到的數據以波形的形式顯示在顯示儀器L。

數據存儲系統:構造數據存儲系統,使數據以文件形式存入存儲設備(FLASH閃存,USB外設,存儲卡等),硬件上還要求支持USB通用串行總線,支持設備的熱插拔,傳輸速度快.結構簡單。

5 結束語

??? 本文所研制的微型工程地震儀系統綜合利用了嵌入式系統設計技術,與傳統地震勘探設備相比大大提高了設備的便攜性和節能性。同時,該系統注重數據快速存儲的研究,并在實際系統中加以應用。本系統在設計時充分考慮了電路的靈活性和通用性,可根據不同的功能要求編寫相應的VHDL語言程序。系統所使用的Windows CE操作系統可以任意裁剪,這對于功能的轉換很有幫助。本系統已研制完畢,現處于現場實驗階段。隨著計算機技術和網絡技術的發展,嵌入式微處理器的性能的提高,嵌入式系統將在工業控制領域得到更廣泛的應用。

電子發燒友App

電子發燒友App

評論