?1 系統總體設計

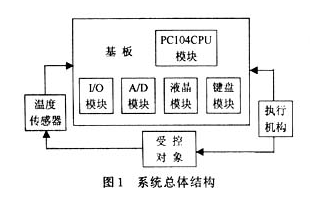

?????? CPLD是一種復雜的用戶可編程邏輯器件,由于采用連續連接結構,易于預測延時,從而使電路仿真更加準確。再加上使用方便的開發工具,如MAX+PLUSII、Quartus等,使用CPLD器件可以極大地縮短產品開發周期,給設計修改帶來很大方便。本論文描述了利用開發工具MAX+PLUS II實現CPLD處理ARINC429數據通信。系統設計方案如圖1所示。

?

??????? ARINC429收發電路部分,由兩組3282和3l82芯片構成,其中每組芯片實現二路接收、一路發送,其中的控制信號均有CPLD編程產生:在CPLD部分,D[0...15]為16位雙向數據總線,實現AR1NC429收發電路與PC104總線接口之間的數據通信,IO16為16位芯片選擇信號;在PC104總線接口部分,XD[0...15]為16位雙向數據總線,XA[1...9]為地址總線,連接CPLD,進行選片操作,XIOR和XIOW 為IO讀寫信號,XAEN 是允許DMA控制地址總線、數據總線和讀寫命令線進行DMA傳輸以及對存儲器和I/O設備的讀寫。

?????? 2 系統硬件組成

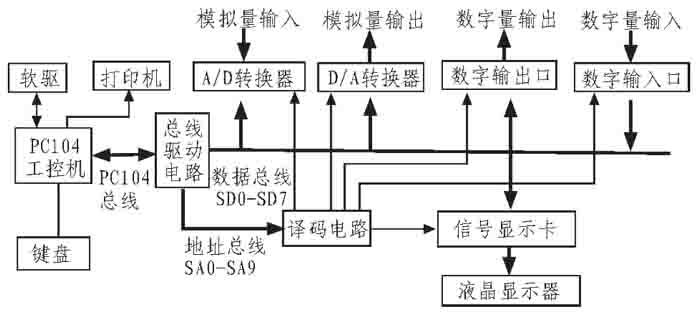

??????? 429的PC104總線接口板的硬件組成框圖如圖2所示,主要包括AR1NC429收發電路(HS3282和HS3l82芯片組)、CPLD、429板與PC 機的接口總線PC104總線、與外部的429接口IDC16插座、中斷控制開關等,其關系如圖2所示。

本接口板元器件布局如圖3所示。

? 3 CPLD內部功能及實現

????? 3.1 開發流程描述

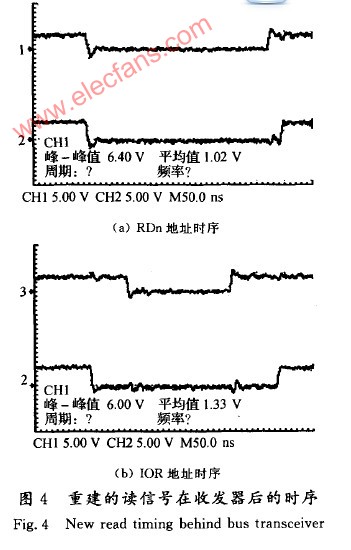

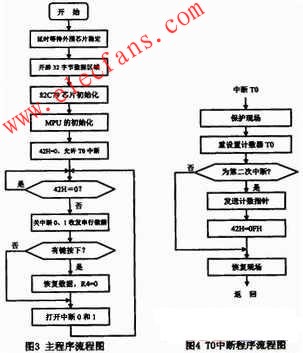

??????? 本系統中的CPLD使用Altera公司的MAX7000S系列可編程邏輯器件中的EPM7128SQC100-6型號,從最初的電路設計思想到MAX+PLUSII的波形仿真,再到CPLD芯片編程結束要經過的一般開發流程如圖4所示。

??????? 3.2 CPLD中的模塊設計

??????? 本設計中CPLD 的功能是實現ARINC429收發電路與接口板的接口總線PC104總線的數據通信。其功能模塊可以分為6部分,以下逐一介紹各模塊的功能及其實現的方法。

??????? (1)產生AR1NC429控制器HS3282所需的TTCLK時鐘信號模塊

???????? TTCLK即發射器時鐘信號,本設計中該信號有480 KHZ和1 MHZ兩種可選頻率,是由一個48 MHZ的晶振提供信號給CPLD,然后由CPLD編程產生480KHZ和1MHZ兩種信號以備選擇。該模塊用圖形編輯的方式實現。要產生3282所需要的480KHZ信號需要對輸入48MHZ信號進行兩次10分頻,要產生1 MHZ信號需要對輸入信號進行6分頻再8分頻。6分頻電路采用3個JK觸發器實現,8分頻電路采用74393實現,10分頻電路采用7490實現。

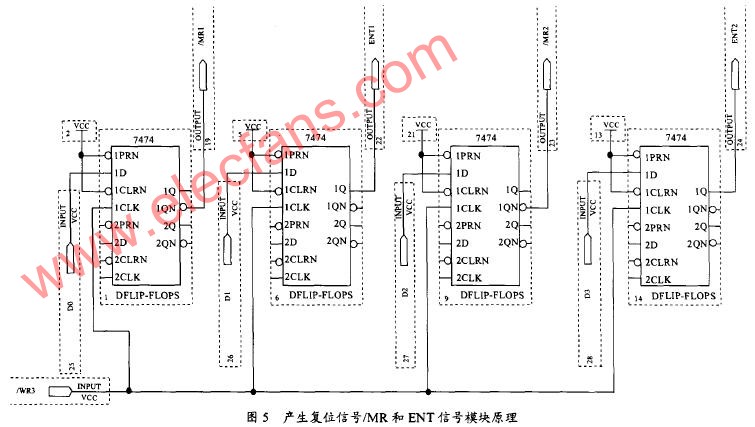

??????? (2)產生復位信號/MR和控制發射器使能信號ENTX的信號ENT模塊

/MR是對3282的主復位信號,/MR將直接送到HS3282,而ENT將送到另一模塊中,用于控制發射器使能信號ENTX的產生,ENTX=ENT*/TXR,其中TXR為發送緩沖區空標志。該模塊也采用電路設計輸入方式。其電路主要由4個D型觸發器74LS74芯片來完成。輸入為總線驅動器的前4個輸出,即D0~D3,時鐘脈沖為產生HS3282讀寫信號模塊的一個輸出信號/WR3,輸出為兩個HS3282的復位信號/MR1和/MR2以及ENT1和ENT2。本模塊具體實現電路如圖5所示。

????? (3)產生片選信號/MCS的模塊

??????? 本模塊產生的/MCS信號用于驅動雙向總線驅動器,進行數據傳輸,并用于選片對HS3282進行讀寫。此模塊用一片8位判決電路74LS688來實現其功能。其中P5-P1接一組基址選擇開關,Q5~Q1分別接PC104總線的地址總線的XA7、XA9、XA8、XA6和XA5,G接PC104總線的地址使能信號端XAEN。只有當XAEN輸入為低時,并且P5~Pl與Q5-Q1的對應端相等時,輸出為低,才有效。

??????? (4)雙向總線驅動器模塊

??????? 該模塊實現AR1NC429收發電路與接口板的接口總線PC104總線的16位數據傳輸。該模塊設計過程為,先用VHDL設計輸入方式設計兩個單向三態數據收發器,然后用電路設計輸入方式,將兩個單向數據收發器合成為一個雙向數據收發器。雙向總線驅動器模塊的功能表如表1所示。

表1 雙向總線驅動器模塊的功能表 使能信號E 方向DIR 操作

雙向總線驅動器模塊產生其一個單向三態數據收發器(TRI_GATE1)的VHDL語言設計如下

library ieee;

use ieee.std_logic_1164.all;

entity tri_gate1 is

port(a0,al,a2,a3:in std_ logic;

a:in std_logic_vector(15 downto 4);

en:in std_logic;

b0,b1,b2,b3:out std_logic;

b:out std_logic_vector(15 downto 4):

D0,D1,D2,D3:out std_logic);

--向模塊2中送數據的4個輸出端

end tri_gatel;

architecture behav of tri_gate1 is

begin

process

begin

if en='1' then --EN為高電平時收發器有效

b0<=a0;b1<=a1;b2<=a2;b3<=a3;b<=a;

D0<=a0;D1<=a1;D2<=a2;D3<=a3;

else --EN為低時高阻狀態

b0<=一Z;b1<=-Z;b2<=-Z ;b3<='Z';b<="ZZZZZZZZZZZZ";

end if

end process;

end behav;

?????? 產生另一個單向三態數據收發器(TRI_GATE)的VHDL語言與此類似,只是少了D0~D3的輸出部分。兩個單向三態數據收發器構成雙向總線驅動器的電路設計如圖6所示(D0_out~D3_out作為圖5中的D0-D3輸入)

(5)產生HS3282讀信號與寫信號和ENTX使能信號模塊

本模塊要實現的功能是產生HS3282的讀寫信號和發送使能信號及一個送入PC104總線的輸入輸出16位芯片選擇信號/IO16。該模塊用VHDL語言輸入,其相應的VHDL語言如下

library ieee;

use ieee.std logic_1164.all;

entity gal4243 is

port(MCS,XIOW,XIOR,A1,A2,A3,A4,ENT1,

ENT2,TXR1,TXR2: in std_logic;

WR0,W Rl,WR2,W R3,WR4,W R5,W R6:

out std_logic;

RD0,RD1,RD2,RD3,RD4:out std_logic;

IO16,ENTX1,ENTX2:out std_logic);

end gal4243;

architecture behav of gal4243 is

begin

process

begin

WR6<=XIOW or MCS or A4 or(not A3) or(not A2)or A1;

WR5<=XIOW or MCS or A4 or(not A3) or A2 or(not A1);

WR4<=XIOW or MCS or A4 or(not A3) or A2 or A1;

WR3<=XIOW or MCS or A4 or A3 or(not A2)or(not A1);

WR2<=XIOW or MCS or A4 or A3 or(not A2)or A1;

WR1<=XIOW or MCS or A4 or A3 or A2 or(not A1);

WR0<=XIOW or MCS or A4 orA3 or A2 or A1; --產生寫信號

if MCS='0' then

IO16<=MCS;

else

IO16<='Z';

endif;

RD4<=XIOR or MCS or(notA4)orA3 or A2;

RD3<=XIOR or MCS or A4 or(not A3)or(not A2);

RD2<=XIOR or MCS or A4 or(not A3)or A2;

RDI<=XIOR or MCS or A4 or A3 or(not A2)

RD0<=XIOR or MCS or A4 or A3 orA2;--產生讀信號

ENTX1<=ENT1 and(not TXR1);

ENTX2<=ENT2 and(not TXR2);--產生發送使能信號

end process;

end behav;

?????? (6)中斷控制模塊

??????? 本模塊用于實現中斷控制操作,有一個接收器滿便產生中斷,產生中斷時亦能判斷出中斷源。該模塊是用VHDL輸入方式產生的,其相應的VHDL程序如下

library ieee;

use ieee.std logic_1164.all;

entity U32 is

port(TXR1,DR11,DR12,TXR2,DR21,DR22,RD4:in std_logic;

D0,D1,D2,D3,D4,D5,INT:out std_logic);

end U32;

architecture behav of U32 is

begin

process

begin

if RD4='0' then

D0<=not DR11:

D1<=not DR12;

D2<=not DR21;

D3<=not DR22;

--產生中斷時用來判斷哪個接收器滿

D4<=TXR1;

D5<=TXR2;

--用來判斷哪一個發送緩沖區空

else

D0<='Z';D1<'Z';D2<='Z';D3<='Z';D4<='Z';D5<='Z';

endif;

INT<=not(DR11 and DR12 and DR21 and DR22); --有一個接收器滿便產生中斷

end process;

end behav;

?????? 3.3 CPLD程序的下載

??????? 各輸入模塊經過編譯處理,根據其相互關系連結,再通過功能仿真和時序仿真確認無誤后,對各輸入輸出端口進行管腳分配。當整個設計完成時,MAX+PLUSII將生成一個文件(.pof),該文件通過下載電纜從JTAG口傳送到PC104板上的CPLD芯片內部。這樣就可將CPLD構造成自己的專用芯片,由此便可以對設計的PC104板卡進行調試。調試過程中CPLD的設計部分還可根據需要進行修改,只是修改后要重新產生.pof文件,重新將文件加載到芯片中。

?????? 4 結束語

??????? 針對PC104接口板的尺寸小的特點,本論文介紹了用CPLD實現基于PC104總線的429接口板,CPLD大大節省了硬件資源,同時也節省了板卡上的可利用空間,徹底解決了PC104 板卡的小尺寸給設計帶來的困難。且CPLD修改簡單,給調試工作帶來了方便。該板卡經過調試后實驗,可穩定工作。實驗結果表明:應用CPLD簡化了系統結構,縮短了設計周期,提高了系統的可靠性。

電子發燒友App

電子發燒友App

評論