本文介紹了一種基于FPGA的用于高分辨率視頻圖像處理的SDRAM控制器的設計方法。通過設置SDRAM的工作狀態,使其工作在猝發模式。在視頻時序信號控制下,用多行連續的SDRAM存儲空間,存取視頻數據。并在數據接口部分增加FIFO,緩存一行視頻,在像素時鐘控制下,實現視頻數據實時的存儲和讀取。通過改變相關參數,能對所有VESA分辨率視頻流進行操作。具有通用性強、系統復雜度低、可靠性高、可擴展等特點。在某型號的機載大屏顯示器系統中,用該SDRAM控制器實現了圖像的翻轉等功能,也驗證了該控制器的實用性。

0引言

隨著人們對視頻圖像的清晰度和細節顯示要求的不斷提高,高分辨率、高bit位的視頻標準相繼被推出。

造成了數據處理速度和數據處理量極大的增加,也給數據緩存的容量和控制提出較高的要求。在常用的存儲器中,SDRAM具有大容量和高速度的特點,并且價格也比較便宜,在視頻圖像處理中被廣泛的用于圖像緩存。在基于FPGA的高分辨率視頻圖像處理系統中,不可避免地會涉及到用FPGA實現SDRAM控制器的方法。但由于SDRAM的操作方式較復雜,常見的控制器支持的視頻分辨率普遍都不高。在高分辨率的視頻圖像已經普及的今天,支持高分辨率的SDRAM控制器的設計也已經被越來越多的視頻圖像處理人士關注。本文介紹的這種控制器,采用的是Micron公司的MT48LC4M32B2TG(1M×32×4 banks)SDR SDRAM,在Altera的StratixⅡ系列FPGA EP2S60F1020I4上進行的開發。

在此平臺上采用VHDL語言開發了SDRAM的控制器。

該控制器實現了最高分辨率為1 600×1 200@60 Hz的視頻流的緩存和圖像翻轉的功能。

1 SDRAM基本操作

SDRAM主要包括初始化、讀/寫操作、刷新、激活、預充電等操作。以MICRON公司的MT48LC4M32B2TG型號SDRAM為例分別介紹。

1.1初始化

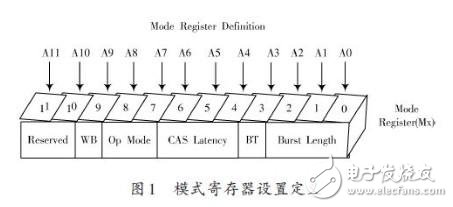

SDRAM在上電后必須執行初始化操作,主要流程為:首先在電源電壓和時鐘穩定后,經過100μs的延時,執行一次空操作;然后進行預充電操作,使所有 BANK都進入空閑狀態;再然后執行兩個自動刷新命令;執行完自動刷新后進入模式設置狀態,通過地址總線A[11:0]發送數據來設置模式寄存器。模式寄存器設置定義如圖1所示。

1.2讀/寫操作

首先激活具體的BANK和行;然后發出讀或寫命令,和所要訪問的起始列。在讀命令發出后,要等待CAS延遲時間,有效數據才會出現在數據總線上。在寫命令發出后,有效數據立即出現在數據總線上。讀寫命令可分為單個模式和猝發模式,猝發模式根據猝發長度分為1,2,4,8和全頁模式。猝發操作可用猝發終止命令(BURST TERMINATE)結束。

1.3刷新

由于SDRAM的內部電路特點,必須執行刷新命令,以防止數據丟失。要求64 ms內至少刷新4 096次。

1.4激活

在讀/寫命令之前都要發出激活命令,激活特定BANK中的某一行。激活后此行一直處于有效狀態,直到接收到預充電命令。

1.5預充電

預充電命令用于關閉特定BANK中的某一行,或者所有BANK.

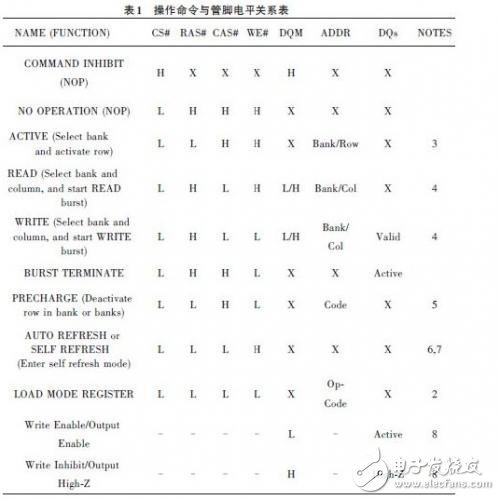

各種操作命令對應的SDRAM管腳電平狀態如表1所示。

2 SDRAM控制器的設計

在視頻圖像處理中SDRAM主要用作數據緩存,也就是FPGA對SDRAM操作最頻繁的為讀命令、寫命令,在這兩個命令中間插著激活、預充電、猝發終止、刷新等命令。對于高分辨率的視頻流,分辨率都在1 280×1 024以上,也就是每行的點像素都要大于1 280個,數據量非常的龐大。

為了降低SDRAM的操作時鐘的頻率和提高視頻處理的實時性,采用猝發的模式對SDRAM進行操作。對于SDRAM MT48LC4M32B2TG地址為A[7:0],猝發操作的最大長度為256.也就是說為了存儲和讀出一行的視頻數據要對SDRAM的多行進行操作。如 1 280×1 024分辨率,需要5行SDRAM空間(256×5=1 280)。

對于不能被256整除的列數如1 600,就要采用控制猝發長度的方式,為了控制方便采用8行SDRAM空間存儲一行視頻數據(200×8=1 600)。標準的VESA分辨率都可以用此方式存儲。在SDRAM控制器中設置了SDRAM的猝發長度的選擇功能,只要修改需要的猝發長度即可,不要重新設計代碼。

為了保證SDRAM的刷新要求,在每一行的SDRAM操作完成后就進行一次刷新操作,此操作經由輸入的視頻行同步信號(HSY)的觸發,如果外部視頻信號突然無輸入,為了保證最后存儲的數據不丟失,進入自刷新模式。一當控制器檢測到HSY無變化就會啟用自刷新模式,周期對SDRAM刷新。

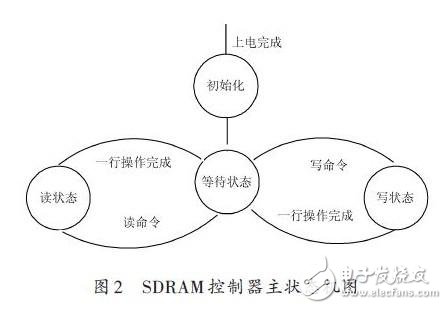

SDRAM控制器主狀態機如圖2所示。

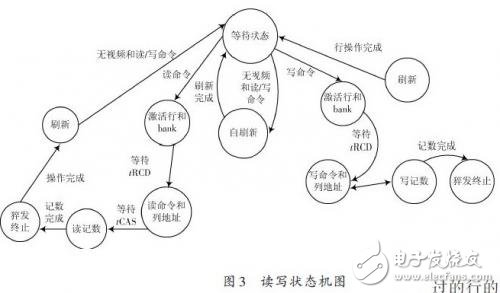

在主狀態機完成初始化狀態,進入等待狀態后,等待讀/寫命令和視頻數據輸入信號。如果無視頻輸入,狀態機始終在等待狀態,并周期性的對SDRAM進行刷新,直到有視頻和讀/寫命令輸入。這部分的狀態圖如圖3所示。

由于猝發的最大長度為256,在每兩行操作之間都要進行激活、讀/寫命令、猝發終止、刷新等操作。由于讀/寫數據都使用的是像素時鐘的頻率,這樣總個 FPGA系統只有一個時鐘域,能保證整個系統完全按照同步系統來設計,能提高整個系統的可靠性。這樣會帶來一個問題,要想僅僅在視頻的有效時間,即DEN 高電平部分完成一行視頻數據的讀/寫工作,這是不能滿足要求的。為了解決這個問題,需要借用行同步、前廊和后廊的時間,但是DEN無效后不傳輸視頻數據的,為了解決這個矛盾在SDRAM控制器和數據流輸入/輸出接口之間要分別設計兩個FIFO,深度大于一行的視頻數據,采用乒乓操作保證視頻流的流暢。

3 SDRAM控制器應用實例

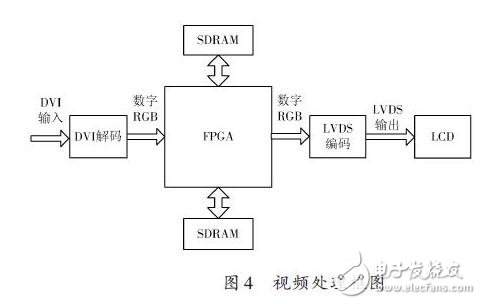

在某型號的機載大屏顯示器系統中,視頻圖像處理系統中使用該SDRAM控制器進行了調試,實現FPGA對SDRAM的控制,完成相應的視頻處理算法和實現了圖像的翻轉功能。此部分系統簡要框圖如圖4所示。

該系統輸入的為多路DVI信號,輸入視頻分辨率均為1 280×1 024,DVI信號經過DVI解碼后輸入FPGA.

為了完成FPGA內部的視頻處理算法和圖像翻轉的功能,在FPGA外部掛了兩組SDRAM,實現了乒乓操作,保證了系統的處理速度。處理后的視頻經過LVDS信號轉化,輸出到液晶屏上顯示。

對于左右翻轉在FPGA內部采用雙口RAM進行操作能夠輕易實現。而圖像的上下翻轉,由于涉及到一幀數據的處理,需要經過外部緩存SDRAM實現。在采用上述SDRAM控制器的基礎上,控制SDRAM的讀方式就能實現,在將視頻數據寫入SDRAM的時候,寫地址從第一行按順序寫入。讀的過程相反,要從最后行開始讀。

由于SDRAM的一行容量不能裝下整行的視頻信息,所以讀的行地址要求每次從讀過的行的地址減去存一行視頻需要的SDRAM的物理行數,在一行視頻數據沒有讀完前要從當前行不斷的自增。如1 280×1 024的視頻數據,共需要5 120(5×1 024)SDRAM行存一幀數據。要上下翻轉輸出圖像,首先要輸出視頻數據的第1 024行,也就是要從SDRAM的5 115行開始按順序讀出,讀完第5 120行后,SDRAM地址轉到5 110行讀視頻流的第1 023行,如此類推,直到讀完整幀的視頻數據。該視頻處理系統與顯示效果如圖5所示。

4結論

該設計針對高分辨率視頻圖像處理的SDR SDRAM控制器的設計,采用統一像素時鐘進行系統操作,降低系統的復雜度,提高系統的可靠性;通過寫修改相關參數,能夠適應所有VESA分辨率的視頻處理,通用性強;具有自刷新功能,在無外部信號輸入情況下能夠自動刷新,保證最后存儲數據不會丟失;能夠通過增加外部模塊,控制讀寫地址,實現圖像翻轉功能。此控制器在Al-tera的StratixⅡ系列FPGA EP2S60F1020I4平臺上,成功實現各種視頻處理功能,驗證了此控制器的實用性。

電子發燒友App

電子發燒友App

評論