小米生態鏈公司之間的產品類別互有重疊的現象已經不稀奇了,這次輪到的是ZMI持續同時朝多面向快速進展的晶圓代工大廠臺積電(TSMC),于美國硅谷舉行的年度技術研討會上宣布其7納米制程進入量產,并將有一個采用極紫外光微影(EUV)的版本于明年初量產;此物該公司也透露了5納米節點的首個時間表,以及數種新的封裝技術選項。

臺積電也繼續將低功耗、低泄漏電流制程技術往更主流的22/12納米節點推進,提供多種特殊制程以及一系列嵌入式內存選項;在此同時該公司也積極探索未來的晶體管結構與材料。整體看來,這家***晶圓代工龍頭預計今年可生產1,200萬片晶圓,研發與資本支出都有所增加;臺積電也將于今年開始在中國南京的據點生產16納米FinFET制程芯片。

唯一的壞消息是,臺積電的新制程節點是不完全步驟,因此帶來的優勢也越來越薄;而新的常態是當性能增加,功耗下降幅度通常在10~20%左右,這使得新的封裝技術與特殊制程重要性越來越高。

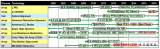

臺積電已經開始量產的7納米制程,預期今年將有50個以上的設計案投片(tap out),包括CPU、GPU、AI加速器芯片、加密貨幣采礦ASIC、網絡芯片、游戲機芯片、5G芯片以及車用IC。該制程節點與兩個世代前的16FF+制程相較,能提供35%的速度提升或節省65%耗電,閘極密度則能提升三倍。

將采用EUV微影的N7+節點,則能將閘極密度再提升20%、功耗再降10%,不過在速度上顯然沒有提升──而且這些進展需要使用新的標準單元(standard cells)。臺積電已經將所謂的N7+節點基礎IP進行硅驗證,不過數個關鍵功能區塊還得等到今年底或明年初才能準備就緒,包括28-112G serdes、嵌入式FPGA、HBM2與DDR 5界面。

臺積電研究發展/設計暨技術平臺副總經理侯永清(Cliff Hou)預期,該EUV制程在布局IP方面需要多花10%~20%的力氣:“我們開發了一種實用方法以漸進方式來轉移IP。”他表示,經過完整認證的N7+節點EDA流程將在8月份完成;在此同時,該節點的256Mbit測試SRAM良率已經與初期版本的7納米節點相當。

展望未來,臺積電預計在2019上半年展開5納米制程風險試產,鎖定手機與高性能運算芯片應用;相較于第一版不采用EUV的7納米制程,5納米節點的密度號稱可達1.8倍,不過功耗預期只降低20%、速度約增加15%,采用極低閾值電壓(Extremely Low Threshold Voltage, ELTV)技術則或許能提升25%;臺積電并未提供ELTV技術的細節。

EUV功率水平順利朝明年初量產發展

“沒有EUV,他們就無法提供與過去節點相同的微縮優勢;”市場研究機構The Linley Group的分析師Mike Demler表示:“如果你看N7+制程,號稱比N7制程再微縮20%,因此EUV還是更接近傳統摩爾定律(Moore’s Law)微縮水平所需的,而N7到N5節點的微縮效果只會更糟。”

臺積電顯然擁有能在明年初以EUV微影進行量產的好運氣,該公司擁有的系統在4月份以250W維持生產數周,預期明年可達到300W,這是大量生產所需的功率水平。不過要維持每日平均145W的功率,臺積電還需要加把勁;對此該公司研究發展/技術發展資深副總經理米玉杰(Y.J. Mii)表示:“生產量正朝向滿足量產所需發展。”

除了透露在功率以及生產量方面的顯著進步,米玉杰表示,盡管仍超出三分之一,光阻劑量(resist dosage)的減少幅度也朝著該公司在2019年第一季量產的目標邁進;此外EUV光源的光罩護膜(protective pellicle的穿透率目前達到83%,明年應該可以達到90%。

米玉杰以數個案例為證明,表示EUV持續提供比浸潤式步進機更佳的關鍵尺寸(critical dimensions)均勻度;臺積電預期會同時在N7+以及5納米節點的多個層采用EUV,并積極安裝ASML的NXE3400微影設備。

看來臺積電的EUV量產計劃與三星(Samsung)的量產時程差距在六個月之內,后者表示將于今年導入量產,更多相關訊息可望在本月稍晚三星自家活動上曝光。而臺積電與三星的EUV量產時程差距,看來并不足以讓Apple或Qualcomm等大客戶更換代工伙伴;市場研究機構VLSI Research執行長G. Dan Hutcheson表示,只有幾個月的領先在長期看來是微不足道。

仍在萌芽階段的臺積電5納米節點,則預計在6月份釋出0.5版的EDA流程,以及在7月份推出0.5版的設計工具套件;該節點還有許多IP功能區塊要到明年才會完成驗證,包括PCIe 4.0、DDR 4以及USB 3.1接口。

臺積電的目標是在2019年讓10/7納米節點產量增加三倍,達到一年110萬片晶圓;該公司的Fab 18已經在***的臺南科學園區興建中,預計在2020年開始5納米制程量產。

多種封裝技術選項

臺積電已經為GPU與其他處理器打造CoWoS 2.5D封裝技術,還有智能型手機芯片適用的晶圓級扇出式封裝InFO,除了繼續推廣這兩種技術,該公司還將添加其他新技術選項。

從明年初開始,CoWoS技術將提供具備倍縮光罩(reticle)兩倍尺寸的硅中介層選項,以因應該領域的需求;而具備130微米凸塊間距的版本則將在今年通過質量認證。InFO技術則會有四種衍生技術,其中內存基板應用的InFO-MS,將在1x倍縮光罩的基板上封裝SoC與HBM,具備2x2微米的重分布層(redistribution layer),將在9月通過驗證。

InFO-oS則擁有與DRAM更匹配的背向RDL間距,而且已經準備就緒;一種名為MUST的多堆棧選項,將1~2顆芯片放在另一顆比較大的芯片頂部,然后以位于堆棧底部的硅中介層來連結。最后還有一種InFO-AIP就是封裝天線(antenna-in-package)技術,號稱外觀尺寸可縮小10%,天線增益則提高40%,鎖定5G基頻芯片的前端模塊應用等設計。

市場研究機構TechSearch International總裁暨資深封裝技術分析師Jan Vardaman表示:“InFO是重要的平臺,臺積電的以PoP形式整合內存與基頻/調制解調器的InFO封裝令人印象深刻──高度較低、尺寸較小而且性能更佳;基板上InFO技術則會在市場上大受歡迎,因為2微米線寬與間距適合多種應用。”

不只如此,臺積電還發表兩種全新的封裝技術選項。其中在4月底問世的WoW (wafer-on-wafer)封裝直接以打線堆棧三顆裸晶,不過使用者還需要確定其EDA流程是否支持這種打線(bonding)技術;該技術還將在6月推出支持EMI的版本。

最后臺積電還大略描述了一種被稱為“整合芯片系統”(system-on-integrated-chips,SoICs)的技術,采用10納米以下的互連來連結兩顆裸晶,但技術細節還要到明年才會透露;該技術鎖定的應用從行動通訊到高性能運算,而且能鏈接采用不同制程節點生產的裸晶,看來是某種形式的系統級封裝(SiP)。

一位分析師在臺積電技術研討會的休息時間表示:“日月光(ASE)一直是封裝技術領域的領導者,但現在我得說臺積電才是。”臺積電的動機很明顯,隨著CMOS制程微縮的優勢漸退,封裝技術能有助于性能表現,一部份是透過更快的內存存取。

在過去幾年,擁有三種后段制程生產線的臺積電拿到了Apple的大訂單,部份是因為InFO與Xilinx還有Nvidia,也有部份是因為CoWoS。而The Linley Groupe的Demler表示,新的封裝技術選項“看來是在摩爾定律終結之后具備長期潛力的替代方案,但成本相當昂貴,也仍有許多問題待克服。”

填滿主流制程選項

臺積電有超過三分之一的營收來自于28納米以上節點,因此該公司除了提及在特殊制程方面的進展,也有比尖端制程舊一至兩個世代的制程節點新進展。

舉例來說,臺積電正在開發22納米平面制程與12納米FinFET制程的超低功耗與超低漏電版本,號稱能與Globalfoundries和Samsung的FD-SOI制程分庭抗禮。新版本的22納米制程采用28納米設計規則,提供10%的光學微縮(optical shrink)與速度增益,或者能降低20%功耗;該制程與相關IP將于今年底準備就緒,鎖定先進MCU、物聯網與5G毫米波芯片等應用。

12納米版本的低功耗/低漏電制程則采用FinFET架構以及更小巧的單元庫(cell libraries),可提供比臺積電16FFC 制程高16%的速度,高速Serdes等少數幾個IP則要到明年才問世。

內存方面,40納米的電阻式RAM已經準備好取代物聯網芯片中的閃存,只需要添加兩層光罩,并支持10年的儲存時間以及1萬次讀寫周期。將于今年問世的22納米嵌入式MRAM支持高于閃存的速度與更長的儲存期限,鎖定汽車、手機、高性能運算等設計;該技術到目前為止號稱在測試芯片上皆具備高良率。

此外,臺積電也提供小型化的微機電系統(MEMS)制程,預期在今年秋天可提供整合10V與650V驅動器的硅基氮化鎵(GaN-on-silicon)制程,明年則可完成蜂巢式通訊功率放大器采用的100V D-HEMT制程驗證。

臺積電也具備車用16FFC制程的經驗證EDA流程以及IP,計劃今年底可提供7納米車用制程,將于2019年第二級通過完整認證。

中國市場與晶體管研發進展

除了宣布其位于中國南京的晶圓廠比預期提早數個月展開16納米FinFET制程生產,臺積電也透露了長期研發計劃,以及在制程自動化方面采用機器學習的進度。

臺積電南京廠的第一階段建筑包括媲美Apple美國新總部但規模沒那么大、外觀像宇宙飛船的員工餐廳以及管狀的辦公大樓,以及月產量2萬片晶圓的廠房;而該廠區若完成所有建設,月產量最高可達到8萬片晶圓。

臺積電南京廠外觀設計圖

在此同時,臺積電的研究員在適合2納米以下制程節點應用的下一代晶體管所需之堆棧納米線(nanowires)、納米片(nanosheets)設計上取得了進展,號稱能支持比FinFET更佳的靜電(electrostatics)特性,而且可以藉由調整組件寬度達到功耗與性能的優化。

臺積電認為鍺(germanium)是具備潛力的硅替代材料,因為在相同速度下功耗較低;該公司已經在與CMOS兼容之介電質中利用該材料,達到了創紀錄的低接觸電阻。臺積電也正在研究各種2D后段材料,包括具備原子級光滑表面的二硫化鉬(molybdenum disulfide)。

此外臺積電也在實驗新方法來放大銅晶粒(copper grain),以降低互連中的電阻;并正在研發選擇性介電質上介電質(selective dielectric-on-dielectric)沉積制程,以實現銅通孔的(vias)的自動對準(self-aligning)。

在內存技術方面,22納米以下節點應用的嵌入式MRAM技術是重點研發項目之一,有可能具備替代性磁結構;在40納米以下電阻式隨機存取內存(ReRAM)部份,高密度的縱橫閂(crossbar)被視為具能源效益的方案,特別是應用于AI加速度芯片。

在制程自動化部份,臺積電正采用機器學習技術系統化分析大量晶圓制程數據,并已經針對特定工具與產品調整了制程參數(recipe);此外該公司也針對制程變異進行追蹤與分類,以實現找出工具、制程或材料中問題所在的自動化。

臺積電擁有具備超過5萬種制程參數與上千萬制程管制圖(control charts)的數據庫,不過該公司將如何把機器學習運用于自動化任務,以及將運用于何種產品在線,目前并不清楚──毫無疑問,仍有某項工作正在進行中,或許其中也有一些不為外人道的秘方。

電子發燒友App

電子發燒友App

評論