美普思科技公司(MIPS Technologies, Inc)宣布,將推出業界首款 64 位處理器架構和多核、多線程(simultaneous multi-threading,SMT)技術相結合的 IP 內核

2011-04-01 10:31:08 1257

1257 本文探究的嵌入式多核處理器采用同構結構,實現同一段代碼在不同處理器上的并行執行。##緩存優化(Cache friendly)的目標是減少數據在內存和緩存之間的拷貝。

2014-12-16 14:43:44 1377

1377 嵌人式多核處理器的結構包括同構(SymmetrIC)和異構(Asymmetric)兩種。同構是指內部核的結構是相同的,這種結構目前廣泛應用在PC多核處理器;而異構是指內部核的結構是不同的,這種結構

2018-10-17 07:55:00 3708

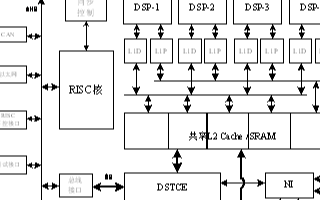

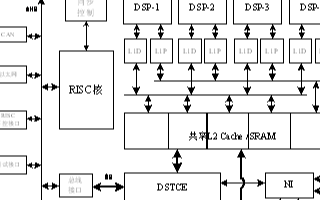

3708 多核數字信號處理器(DSP)是近年來針對高性能嵌入式應用而出現的一類多核微處理器(CMP)。相比傳統的單核處理器,多核處理器在提高并行處理能力的同時也需要更高的存儲帶寬和更靈活的存儲結構。便箋存儲器(SPM)是一種小容量的片上存儲器,具有全局地址空間,可以由訪存指令直接訪問。

2020-08-20 14:38:19 1311

1311

其實“多核”這個詞已經流行很多年了,世界上第一款商用的非嵌入式多核處理器是2002年IBM推出的POWER4。

2023-11-16 16:25:50 706

706

嵌入式系統以各種類型的嵌入式處理器為核心,而隨著技術的發展,對于嵌入式處理器的性能及功耗的要求愈加嚴苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩定

2019-07-19 08:29:10

32位處理器可以裝64位系統嗎?從技術角度看,32位處理器是不能裝64位系統的,因為不支持,不確定的用戶可以使用下面的兩種方法來檢查32位處理器是否能裝64位系統。方法:通過計算機評分查看1、以

2020-06-28 09:57:16

Imagination Technologies 宣布,該公司的64位MIPS架構已獲得面向下一代企業、數據中心與服務提供商基礎架構等應用的Cavium新款低功耗OCTEON? III SoC處理器的采用。

2020-05-14 07:21:46

多核處理器,在每個多核處理器芯片內部的L2和L3可以采用共享緩存或SMP方式,而在多個芯片間采用DSM結構互連。原作者:老秦談芯

2022-06-07 16:46:44

情況下會采用分層結構,對于多核處理器,一般L1緩存是獨享的,最后一級緩存是共享的。不管單核處理器系統還是多核處理器系統,都要對所有層級的緩存做初始化。接下來就是內存的初始化了,在此步驟之前的代碼執行要么

2022-06-07 16:41:29

、會經常修改,后面發布的為準。為與虛擬內存頁的概念一致,修改為:1c(簇cluster)= 8kp頁(page) = 64ks(扇區sector),1p頁(page)= 8s(扇區sector)=4kb。多核處理器則是指在單個芯片上包含任意多個(如2、4、8、..

2021-09-10 06:06:50

多內核是指在一枚處理器中集成兩個或多個完整的計算引擎(內核),多核處理器是單枚芯片(也稱為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統會利用所有相關的資源,將它的每個執行內核作為分立的邏輯

2019-06-20 06:47:01

機)節點集成到同一芯片內,各個處理器并行執行不同的線程或進程。在基于SMP結構的單芯片多處理機中,處理器之間通過片外Cache或者是片外的共享存儲器來進行通信。而基于DSM結構的單芯片多處理器中,處理器間

2011-04-13 09:48:17

輸出異常呢?接下來,小編就以飛凌嵌入式OKMX8MP-C開發板為例,將多核異構處理器對共享外設和資源的調配方法介紹給大家。飛凌嵌入式OKMX8MP-C開發板所搭載的NXP i.MX8M Plus處理器

2023-03-10 11:54:37

(Point of Unification):在此處確保PE的指令和數據緩存以及地址轉換表遍歷能夠看到相同副本。對于單核處理器來說,PoU就是系統內存;對于多核處理器,PoU取決于共享域

2023-02-16 13:55:52

和數據緩存,包括具有

未命中(HUM)

?兩個緩存的64位接口

?可旁路寫入緩沖區

?一級緊密耦合存儲器(TCM),可用作本地RAM

?矢量浮點(VFP)協處理器

?跟蹤支持

?基于JTAG的調試

2023-08-02 09:15:45

簡單的總線接口,允許您圍繞它設計自己的緩存和內存系統。ARM9TDMI系列微處理器支持32位ARM和16位Thumb指令集,允許您在高性能和高代碼密度之間進行權衡。ARM920T處理器是一款哈佛

2023-08-02 13:05:00

ARM920T 高緩存處理器是 ARM9 Thumb 系列中高性能的 32 位系統處理器。而 ARM920T 系列微處理器包含如下幾種類型的內核。ARM9TDMI:只有內核。ARM940T:由內核

2019-09-26 09:43:55

)?ARM922T(核心加8K和8K緩存以及MMU)。ARM9TDMI處理器核心是哈佛體系結構的設備,使用由Fetch、Decode、Execute、Memory和Write階段組成的五階段流水線。它可

2023-08-02 15:44:14

處理器的啟動,僅此而已,所以,現在社區幾乎很少使用spin-table這種方式,取而代之的是psci,他不僅可以啟動從處理器,還可以關閉,掛起等其他核操作,現在基本上arm64平臺上使用多核啟動方式都是

2022-06-06 17:11:43

和 Cortex-A53 處理器是基于 ARMv8 體系結構的第一種處理器,它們擴展了 32 位處理的性能并引入了世界上能效最高的 64 位技術。突破性的 Cortex-A50 系列提供一個可擴展的靈活

2014-03-07 15:27:25

體系結構是64位R-Profile ARM?體系結構,僅具有AArch64執行狀態。

因此,Cortex?-R82處理器不支持AArch32執行狀態。

Cortex?-R82處理器支持ARM?v8.4架構

2023-08-17 07:45:14

的Cortex-A9MPCoreTM多核處理器或較為傳統的Cortex-A9單核處理器。Cortex-A9分為可擴展的多核處理器和單核處理器(兩款不同的獨立產品)支持16、32或64KB四路組相聯一級緩存的配置,在

2014-11-03 17:02:32

。 對TCM的未緩存訪問Hexagon處理器擁有一個全功能的MMU,用于將虛擬地址翻譯為物理地址。每個頁包含一系列的緩存屬性位。為了使用未緩存的方法去訪問緊耦合存儲器,下面的要求必須滿足: 虛擬頁必須被設置為

2018-09-20 16:50:09

Intel 64x86_64IA-32x86處理器基本執行環境 (1) - 32位執行環境概述

2019-05-22 15:11:47

Intel 64x86_64IA-32x86處理器基本執行環境 (2) - 64位執行環境

2019-06-06 06:54:30

/G2L系列以及TI的AM62x系列等等。雖然這些處理器的品牌及性能有所不同,但多核通信原理基本一致,都是基于寄存器和中斷傳遞消息,基于共享內存傳輸數據。以配電終端產品為例,A核負責通訊和顯示等人

2022-11-21 09:45:10

RK3566四核64位處理器有哪些特點及其功能呢?

2022-03-02 06:00:59

STM32MP1多核微處理器有哪些性能呢?

2021-12-15 06:13:14

arm為什么是32位微處理器呢?所以ARM體系結構所支持的最大尋址空間為4GB嘍?

2023-03-15 10:27:53

iMX8M Mini多核應用處理器有哪些功能及應用?iMX8M Mini多核應用處理器底板接口是如何構成的?

2021-11-04 07:32:37

stm32mp157是什么?stm32mp157多核異構處理器有哪些功能呢?

2022-02-28 06:58:34

心的處理器,故而要嘗試并測試這個開發板與三星的四核A9處理器。學習處理器各核心間的通訊、公共資源爭用與協調工作、共享內存使用的問題。多核心處理器必然成為當前的主流,多核心處理器的學習使用對自己的職業發展

2015-11-11 11:00:26

輸出異常呢?接下來,小編就以飛凌嵌入式OKMX8MP-C開發板為例,將多核異構處理器對共享外設和資源的調配方法介紹給大家。飛凌嵌入式OKMX8MP-C開發板所搭載的NXP i.MX8MPlus處理器

2023-02-07 15:46:18

本文主要介紹TMS320C6678處理器開發中比較常用的多核通信方式:OpenMP,主要基于創龍科技TL6678-EasyEVM評估板進行演示。?圖1 TL6678-EasyEVM評估板

2021-01-28 20:14:28

32位處理器首先處理器都是8的倍數:8/16/32/64。表示一個時鐘周期里,處理器處理的代碼數。8位機有8條線路,每個時鐘周期有8個電信號,組成一個字節。8-32,則每個時鐘周期從傳輸1個字節到8

2021-07-13 08:41:21

嵌入式系統以各種類型的嵌入式處理器為核心,而隨著技術的發展,對于嵌入式處理器的性能及功耗的要求愈加嚴苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩定

2019-07-05 07:52:22

運行中更換或重新啟動幾乎所有的模塊,甚至是設備驅動程序。QNX對多核處理器的支持基于其微內核結構,通信被集成到QNX消息傳遞原語,本地的IPC和遠端節點間的IPC一樣。在單CPU上運行的進程分布到多

2019-06-29 08:30:00

進行控制操作和多媒體顯示;DSP天生為數字信號處理而生,擅長進行專用算法運算;FPGA擅長高速、多通道數據采集和信號傳輸。同時,異構多核SoC處理器核間通過各種通信方式,快速進行數據的傳輸和共享,可完美實現

2020-09-08 09:39:19

基于RK3399處理器的64位6核服務器級處理器具有哪些功能呢?

2022-03-04 10:02:37

如何用TMS320C6678處理器進行TI-IPC多核通信案例本文基于創龍科技TL6678-EasyEVM評估板進行演示。?圖1TL6678-EasyEVM評估板TL6678-EasyEVM是一款

2021-01-25 19:49:47

多核處理器環境下的編程挑戰是什么如何通過LabVIEW圖形化開發平臺有效優化多核處理器環境下的信號處理性能

2021-04-26 06:40:29

包括同構(Symmetric)和異構(Asymmetric)兩種。同構是指內部核的結構是相同的,這種結構目前廣泛應用在PC多核處理器;而異構是指內部核的結構是不同的,這種結構常常在嵌入式領域

2021-12-14 07:47:01

嵌入式多核處理器結構OpenMP并行化優化

2021-03-02 06:59:00

處理器DSP4、嵌入式片上系統SOC(System-on-a-Chip)三、多核處理器四、嵌入式操作系統EOS五、嵌入式實時操作系統RTOS六、嵌入式系統設計七、嵌入式系統的軟件一、嵌入式微處理器體系結構1、馮諾依曼體系結構(1)程序和控制共用一個存儲

2021-11-08 06:57:02

、嵌入式微處理器的結構和類型:嵌入式微處理器的分類、典型的8位微處理器的結構和特點、典型的16位微處理器的結構和特點、典型的32位微處理器的結構和特點、DSP處理器的結構和特點、多核處理器的結構和特點

2017-10-30 14:33:10

的結構和類型:嵌入式微處理器的分類、典型的8位微處理器的結構和特點、典型的16位微處理器的結構和特點、典型的32位微處理器的結構和特點、DSP處理器的結構和特點、多核處理器的結構和特點。 2、 嵌入式

2017-06-28 13:55:53

于中央的高性能ARM? Cortex?-A15,該處理器系列為工業市場提供了一個擁有高性能和高靈活性的解決方案。多核處理器是很多工業應用的理想選擇,其中就包括可編程邏輯控制器(PLC)。PLC上的工業

2018-09-04 10:07:50

中的多核處理器設計。這些處理器的目標應用可以被很好地劃分為適合DSP的信號處理任務和適合RISC CPU的控制任務,從而使得劃分相當簡單。一個例外是ADI的Blackfin BF561雙核DSP。該

2009-04-09 23:14:41

協議用于維護由于多個處理器共享數據引發的多處理器數據一致性問題。論述了一個適用于64位多核處理器的共享緩存設計,包括如何實現多處理器緩存一致性及其全定制后端實現。本文介紹了一種共享高速存儲器模塊

2021-02-23 07:12:38

目錄PC/XT機的系統板32位微型機的典型結構64位微型機多核處理器技術PC/XT機的系統板CPU子系統接口部件子系統存儲器子系統32位微型機的典型結構主板的組成PentiumⅡ主板集成型主板64位

2021-09-10 06:48:42

情況下會采用分層結構,對于多核處理器,一般L1緩存是獨享的,最后一級緩存是共享的。不管單核處理器系統還是多核處理器系統,都要對所有層級的緩存做初始化。接下來就是內存的初始化了,在此步驟之前的代碼執行要么

2022-07-19 15:00:47

硬之城要給大家說說了,恩智浦半導體已推出了QorIQLS1012A處理器,采用非常小的封裝尺寸,為消費和網絡應用提供企業級性能和安全性,這芯片是一款64位ARMv8處理器,具有與網絡分組加速性能

2016-03-14 14:59:53

調節多核處理器硬件適應軟件設計方法 典型的嵌入式系統設計人員在硬件平臺上進行編程,他們最關注的一點就是硬件平臺的穩定性。如果硬件沒有設置好,會帶來重新編寫代碼的麻煩。但是一個完全

2008-09-25 17:17:55

面向多核處理器的低級并行程序驗證要 隨著多核處理器的廣泛使用以及人們對軟件提出了更高的可靠性要求,多核并行程序驗證的重要性日益凸顯。本文提出了一個完整的基于多核的并行程序驗證框架,該驗證框架包括抽象

2009-10-06 09:56:26

針對共享緩存式交換機能提供理想的吞吐量、延時性能和對于一定的丟失率共享緩存交換機需要的內存較其他交換機小的特點,結合現有的共享緩存式以太網交換機芯片,對該交

2009-04-19 19:17:20 24

24 多核數字信號處理器 DSP 3 C64x+ DSP MHz (Max) 850, 1000, 1200 CPU 32-/64-bit Operating

2022-12-14 14:40:55

隨著片上晶體管資源的增多和互連線延遲的加大,分片式多核微處理器已成為多核處理器設計的新方向.為了對這種新型處理器進行體系結構的深入研究和設計空間的探索,設計并實

2009-10-06 08:49:50 6

6 Spinlock 在 Linux 中被廣泛應用于解決多核處理器之間訪問共享資源的互斥問題,本文以MIPS 多核處理器為例,介紹了 Spinlock 的設計與實現,以及 Spinlock 的不足與擴展。

2009-12-04 11:59:40 18

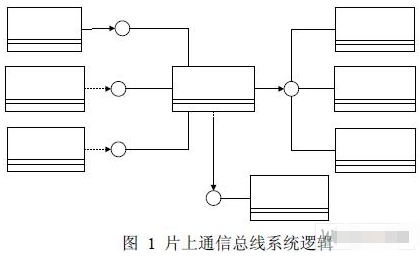

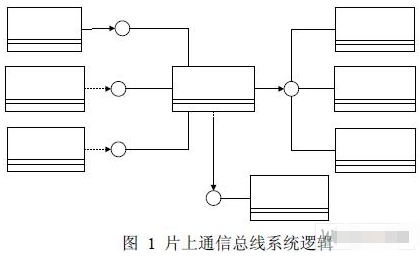

18 多核處理器是處理器領域發展的必然趨勢。多核之間的通信可以利用基于總線的共享cache實現,也可以通過片上互連技術實現。在采用共享總線的多核體系結構中,如何解決多個處

2010-01-16 13:26:26 16

16 摘要:為了提高基于虛擬存儲技術的嵌入式處理器的性能,本文提出了一種用于高效加速地址轉換的TLB電路結構該電路采用64-entries的全關聯結構,硬件支持基于段及不同大小頁的轉

2010-05-12 10:01:39 18

18 管理和服務質量優化的數據路徑加速。這種先進的16核64位Arm處理器非常適合5G數據包處理、網絡功能虛擬化(NFV)、白盒交換、高處理工業計算機、機器學習和智能網

2023-12-11 16:57:16

處理器緩存 緩存(Cache)大小是CPU的重要指標之一,其結構與大小對CPU速度的影響非常大。簡單地講,緩

2009-12-17 11:06:25 344

344 什么是處理器緩存 緩存是指可以進行高速數據交換的存儲器,它先于內存與CPU交換數據,因此速度很快

2009-12-17 16:03:57 586

586 什么是處理器緩存處理器緩存:

Cache(高速緩沖存儲器)是位于CPU與主內存間的一種容量較小但速度很高的存儲器。由于CPU的速度遠

2010-02-04 12:02:26 767

767 Intel 64位處理器,Intel 64位處理器結構原理

現在人們廣泛使用的是由32位微處理器構成的計算系統,但是32位的計算和操作系統不能支持

2010-03-26 15:07:53 3145

3145 什么是AMD64位處理器

Opteron和Athlon64微處理器

AMD公司在2000年公布了54位微處理器X86-64指令結構的全部技術規

2010-03-26 15:15:23 1257

1257 AMD雙核處理器,AMD雙核處理器結構原理分析

AMD Athlon 64 X2處理器架構及產品 Athlon 64 X2 的大多數技術特征、功能與目前市售的基于AMD64

2010-03-26 15:17:22 813

813 認識多核基本架構

多核處理器在同一個芯片中植入了多個處理器引擎,這就可以提供更高的CPU性能、功能特性和分區能力。一般說來,多核有兩種實現形式。

2010-08-26 18:08:00 1242

1242 摘要:多核技術成為當今處理器技術發展的重要方向,已經是計算機系統設計者必須直面的現實。從計算機系統結構的角度探討了同構與異構、通用與多用等多核處理器類型,分析了典型多核處理器的微結構、工藝等結構特點,討論了多核處理器對計算機系統結構設計帶

2011-02-27 16:03:11 38

38 多核處理器以其高性能、低功耗、設計周期短等諸多優勢成為未來高性能處理器的發展趨勢。由于應用對計算能力的需求是無限的,隨著芯片上晶體管數目的進一步增多,多核處理器將

2011-05-30 10:06:35 52

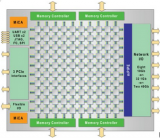

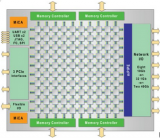

52 多核處理器的新貴Tilera在幾年前才開始嶄露頭角,該公司多核架構的關鍵優勢是協調具備基本CPU功能的高度可擴展的核心數量,單獨的緩存,非阻塞的路由用于核心之間的通信,還包括快

2012-02-02 09:33:14 954

954 多核密碼處理器中的片上網絡互連結構研究_杜怡然

2017-01-03 18:00:37 0

0 多核處理器中的超越函數協處理器設計_黃小康

2017-01-07 18:39:17 2

2 多核密碼處理器數據緩存機制研究_陳曉鋼

2017-01-07 18:39:17 0

0 有人認為諸如圖形處理器(GPU)和Tilera處理器等多核處理器在某些應用中正逐步替代現場可編程門陳列(FPGA)。理由是這些多核處理器的處理性能要高很多,例如,由于GPU起初主要負責圖形繪制,因此,其尤其善于處理單精度(SP)及(某種情況下)雙精度(DP)浮點(FP)運算。

2017-02-11 11:15:11 896

896

多核處理器基礎,介紹了嵌入式的多核的信息

2017-04-11 14:17:49 2

2 與單核處理器相比,多核處理器在體系結構、軟件、功耗和安全性設計等方面面臨著巨大的挑戰,但也蘊含著巨大的潛能。

2017-04-24 08:53:01 1701

1701 少,另外,嵌入式多核處理器與PC平臺多核處理器有很大不同,因此不能直接將PC平臺的并行化優化方法應用到嵌人式平臺。本文分別從任務并行和緩存優化兩方面進行并行化優化的研究,探索在嵌人式多核處理器上對程序進行并行化優化

2017-10-16 10:01:55 1

1 CMP和SMT一樣,致力于發掘計算的粗粒度并行性。CMP可以看做是隨著大規模集成電路技術的發展,在芯片容量足夠大時,就可以將大規模并行處理機結構中的SMP(對稱多處理機)或DSM(分布共享處理

2017-10-26 16:24:14 0

0 眾核處理器設計在芯片面積上受到了巨大挑戰,如何將有限的芯片面積投入到運算能力中,是眾核處理器體系結構研究的熱點。聚焦眾核處理器的指令緩存結構設計,研究通過在多核核心之間共享一級指令緩存,以獲取

2017-11-21 14:03:06 12

12 為了能夠靈活地驗證和實現自主設計的基于NoC的多核處理器,縮短NoC多核處理器的設計周期,提出了設計集成4片Virtex-6—550T FPGA的NoC多核處理器原型芯片設計/驗證平臺。分析和評估

2017-11-22 09:15:01 4137

4137 CMP和SMT一樣,致力于發掘計算的粗粒度并行性。CMP可以看做是隨著大規模集成電路技術的發展,在芯片容量足夠大時,就可以將大規模并行處理機結構中的SMP(對稱多處理機)或DSM(分布共享處理

2017-11-30 12:35:19 548

548 隨著計算機硬件技術的發展,如今我們已經邁入了多核CPU時代.然而,作為軟件核心的數據結構仍然是按照單核CPU和順序型準則來設計的.在基于共享內存的多核時代,大量并發運行的線程會交替地修改數據,產生

2018-01-15 11:34:12 0

0 嵌人式多核處理器的結構包括同構(Symmetric)和異構(Asymmetric)兩種。同構是指內部核的結構是相同的,這種結構目前廣泛應用在PC多核處理器;而異構是指內部核的結構是不同的,這種結構

2018-11-19 09:57:00 2393

2393

根據WCCFTECH的報道,早在Skylake微架構發布時,英特爾就開始在HEDT系列處理器中調整其CPU的緩存結構。現在根據Geekbench的說法,英特爾即將發布的10nm Tiger Lake移動處理器也將進行類似的緩存結構調整。

2019-12-02 11:41:14 2149

2149 多核處理器以其高性能、低功耗優勢正逐步取代傳統的單處理器成為市場的主流。隨著應用需求的擴大和技術的不斷進步,多核必將展示出其強大的性能優勢。但目前多核處理器技術還面臨著諸多挑戰,本文主要介紹了多核處理器發展的關鍵技術并對多核處理器技術的發展趨勢進行簡要分析。

2021-03-29 10:47:31 8

8 如今,隨著集成電路工藝發展到深亞微米的階段,處理器體系結構的設計研究正朝著多 核的方向發展。Intel、IBM、SUN 等主流芯片產商已經在市場上發布了自己的多核處理器。 目前多核處理器的發展尚處于起步階段,有很多問題還有待解決。其中,一個十分重要的方 面就是設計高效的片上通信架構。

2021-06-08 15:21:46 3830

3830

CPU核數的增多給處理器的設計帶來了很多新的挑戰,包括我在前面文章中介紹的cache一致性,內存一致性等,既然多核的引入使系統變得如此復雜,那為什么我們還需要發展多核處理器,并且核數還越來越龐大,而不是專注于提升單核的計算能力?

2022-12-05 15:12:22 592

592 什么是多核處理器?多核處理器是包含兩個或多個處理器的芯片。每個處理器能夠同時執行不同的任務。例如,如果一個處理器被分配了數據處理的任務,另一個處理器將負責數據存儲。 為什么使用多核處理器?該設置

2023-07-13 17:08:47 1438

1438

電子發燒友App

電子發燒友App

評論