1、背景介紹

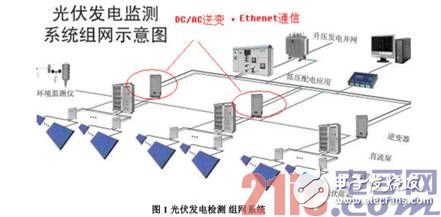

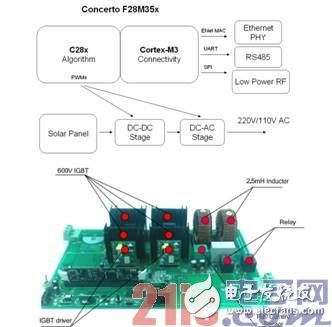

隨著各個行業朝著智能化方向的發展,嵌入式產品對能耗和效率的要求越來越苛刻。特別是在智能電網、工業和醫療等領域,一個產品的核心 MCU 處理器面臨多重挑戰。比如,一個自動化的馬達系統或者分布式工業系統,一方面需要更多的數字信號處理能力來更精確地控制馬達,另一方面也需要更多和更高級的網絡接口(CAN,Ethernet 或者 Wireless 等)來實現實時的分布式監控或控制功能。再比如圖 1,一個太陽能逆變系統,一方面需要 DSP 引擎來實現 DC/AC 或者 DC/DC 的算法,另一方面也需要將多個逆變器通過 Wireless 或者以太網 Ethernet 組成網絡,從而實現智能診斷和監控。

面對這些需求,有兩種傳統的方案可以解決。一種方案是采用兩顆單獨的 MCU/DSP,其中一顆 MCU或者 DSP 用于實現數字信號處理或者控制算法,另外一顆 MCU 實現網絡協議棧或者圖形顯示界面等。這類方案的存在諸多缺點,首先兩顆 MCU 增加了 PCB 的面積,而且雙 MCU 之間的通訊的可靠性和數據吞吐率受到限制,另外,功耗也將顯著增加,程序開發者甚至需要維護多個軟硬件開發環境。另外一種方案是采用更高主頻和更多片內資源的單核 MCU/DSP,分時地完成數據處理和輔助通信或顯示功能,這種方案顯著增加了系統成本和功耗,最致命的是,當客戶的產品需要增加新的功能的時候,工程師需要重新計算 MCU 內核的資源和不同任務所需要的運行時間,需要更多的測試時間,因此不利于擴展和產品維護。

面對種種不足,異構雙核架構應運而生,可以很好解決上述問題。事實上,非對稱雙核架構 MCU 可以將不同的系統任務分配于不同的 MCU 內核,分工精細,并且可以最佳地平衡性能、功耗和成本。兩個MCU 內核間的通信可以通過不同的方式來實現,比如分享內存區和消息區,非常簡單和易于實現。在下面的章節,本文將以 TI 最新的 Concerto 系列產品 TMS320F28M35H52C 為例,詳細闡述非對稱異構雙核 MCU 的優勢,及其為系統帶來的性能提升。

2、C2000 Concerto 雙核 MCU 的特點

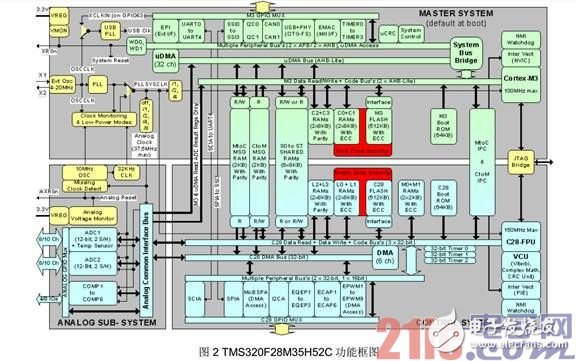

C2000 Concerto 系列 MCU 是 TI 推出的創新性的異構雙核產品。Concerto 混合架構通過將業界最好的實時控制功能和通訊功能集成在一個芯片內,提供高性能、高效率和可靠性,從而實現實時控制環路和低延時的快速通訊響應[1]。以下從內核、存儲器架構、通訊外設等方面闡述其特點。Concerto 系列 TMS320F28M35H52C 功能框圖如下圖 2 所示。

首先是高性能的內核。Concerto 系列 MCU 包含 Cortex-M3 和 C28x 兩個內核。Cortex-M3 內核是Concerto 的主系統 Master 子系統內核,主頻最高可運行于 125 MHz。Cortex-M3 內核是 32 位的ARM 核,超高的性價比,已經被業界廣泛使用,其性能和穩定性也已被用戶所廣泛接受,非常適用于通訊和事件控制。C28x 是新一代的 32 位 DSP 內核,是 TI 大多數現有的 C2000 產品的內核,最高可運行于 150 MHz,Concerto 中的 C28x 帶浮點運算單元(Floating-Point Unit),VCU 協處理器等,性能超強,非常適用于大吞吐量的數據處理。C28x 作為 Control 子系統,宏觀上受控于 Cortex-M3 Master 子系統。

其次是優化的存儲器架構。如圖 2 所示,TMS320F28M35H52C 的 C28x 可支配 512KB 帶 ECC 校驗的 Flash 存儲器,64KB ROM,36KB 帶 ECC 校驗的 RAM;Cortex-M3 可支配 512KB 帶 ECC 校驗的Flash 存儲器,64KB ROM,32KB 帶 ECC 校驗的 RAM [3]。在兩個內核之間,是共享的外設和存儲區。總共 64K 字節的共享 RAM,4K 的消息 RAM。

再次是外設。如圖 2 所示,TMS320F28M35H52C 的 C28x 內核可支配 DMA、高速 ADC(3MSPS)、多路高精度的 PWM(24 路 PWM和 16 路高精度 HRPWM)、eCAP、eQEP 等為閉環控制所優化的控制外設;Cortex-M3 內核可支配多個串行接口、以太網、CAN 等工業通訊外設。同時,兩個內核還可共享 ADC 等外設,增強整個系統的靈活性。

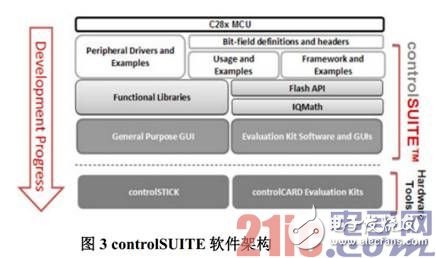

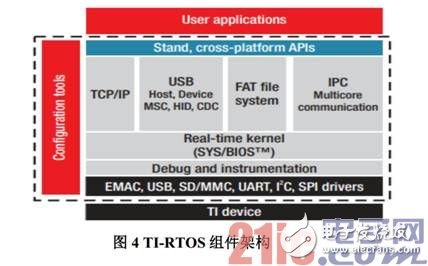

最后是軟件架構。如圖 3 所示,controlSUITE 是一個集成所有 C2000 MCU 的開發資源和軟件包和開發平臺,它為 TMS320F28M35H52C 的開發者提供了外設例程、DSP 庫、文檔、開發板資料。ControlSUITE 還提供免費的全功能實時操作系統 TI-RTOS 平臺,如圖 4 所示,TI-RTOS 是基于SYS/BIOS 實時內核,集成了穩定的中間件,例如 TCP/IP 協議棧、USB 協議棧、FAT 文件系統、IPC多核通訊組件等。

3、IPC 內核間通信

Cortex-M3 和 C28x 內核之間的通信主要完成兩大功能,一是數據通信,二是傳遞狀態和控制信息。IPC(內核間通訊)的數據通信需要較大的 RAM 來支持,而傳遞狀態和控制等信息只需要一系列狀態標志位即可。此外,Cortex-M3 側的 UART4 與 C28x 側的 SCIA;以及 Cortex-M3 側的 SSI3 與 C28x側的 SPIA 在 Concerto 內部實現互聯,不需要在芯片外部硬件連接,而是否使能這類功能則有 CortexM3 系統配置。

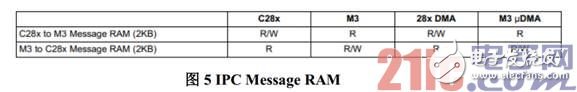

3.1 Message RAM 內存區

TMS320F28M35H52C 使用 Message RAM 實現 IPC 的數據通信。如圖 5 所示,2K 字節的 MTOC Message RAM 用于從 Master (Cortex-M3)子系統向 Control(C28x)子系統傳遞消息;2K 字節的CTOM Message RAM 用于從 Control 子系統向 Master 子系統傳遞消息。由于兩個子系統都配有 DMA外設,因此,DMA 也可以讀寫 Message RAM,從而提高系統效率。Message RAM 區通過 RAM 內存的讀寫權限保證了 Message 的互斥訪問,例如,C28x CPU 與 DMA 可以讀寫訪問 CTOM Message RAM 區,而 Cortex-M3 CPU 和 uDMA 只能讀訪問 CTOM Message RAM。同樣,兩個內核對于MTOC Message RAM 區的讀寫訪問權限則正好相反。

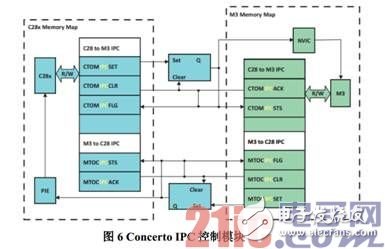

Message RAM 僅僅作為 IPC 的數據緩存,IPC 還需借助于特定的控制邏輯電路來完成。如圖 6 所示,Master 子系統和 Control 子系統都是通過 5 個寄存器來實現 IPC 的邏輯流程控制:IPCACK、IPCSTS、IPCFLG、IPCCLR、IPCSET。這 5 個寄存器都是 32 位,每一個 bit 對應于 IPC 的一個通道,因此最多可實現 32 個通道的握手通信。Bit0 到 Bit3 總共 4 個通道可以觸發消息接收方的 IPC 中斷,Bit4 到Bit31 共 28 個通道則需要消息接收方的軟件查詢來獲取 Message RAM 中是否收到數據。如果兩個內核之間僅僅傳遞狀態和控制信息(例如 RTOS 中的 Semaphore),僅通過以上寄存器便可以實現,而無需 Message RAM 的參與。

以下通過舉例 Master 子系統往 Control 子系統發送一幀數據,來簡單介紹 IPC 模塊的操作流程。

1. Cortex-M3 先在 MTOC Message RAM 中寫入一幀數據;

2. Cortex-M3 置位 MTOCIPCSET(CM3 映射存儲器區)的 Bit9,如圖 6 所示,此時 MTOCIPCSTS(C28x 映射存儲器區)的 Bit9 也將置位;

3. C28x 輪詢 MTOCIPCSTS 的 Bit9,查詢到 Bit9 已置位;(如果之前的操作是 Bit0 到 Bit3 其中之一, 則將觸發 C28x 產生一個 IPC 中斷)

4. C28x 讀 MTOC Message RAM 中的數據,此時,Cortex-M3 成功將一幀數據發送至 C28x。

3.2 Shared RAM 內存區

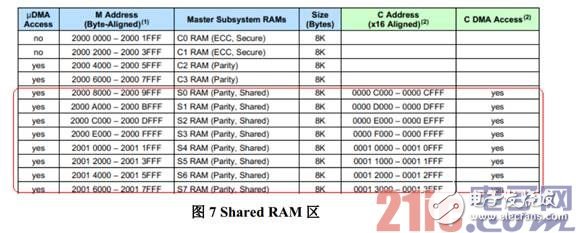

大部分情況下,2K 字節的 IPC Message RAM 區能夠滿足 C28x 和 M3 子系統之間的數據通信,配合DMA,通信效率也可以進一步提高。如果用戶希望一次性在兩個子系統傳遞更大塊的數據,另一種方法是通過 Shared RAM 內存。

TMS320F28M35H52C 有一個 64K 字節大小的 Shared RAM 區,總共 8 塊 S0-S7,每塊 8K 字節大小,如圖 7 所示。Cortex-M3 可以設置讓任何一塊 Shared RAM 區由 C28x 或 M3 主控,比如,映射 S0 至C28x 側以后,C28x CPU 和 DMA 可以讀寫 S0,而 M3 和 uDMA 將只能讀 S0,不能寫入和預取。

假如 Cortex-M3 需要一次性發送 6K 字節的數據到 C28x 側,它可以先將 Shared RAM 區 S0 映射到本地存儲器空間,接著通過 IPC 發送一個標志位給 C28x 來通知其可以將數據取走。

3.3 IPC 的軟件驅動

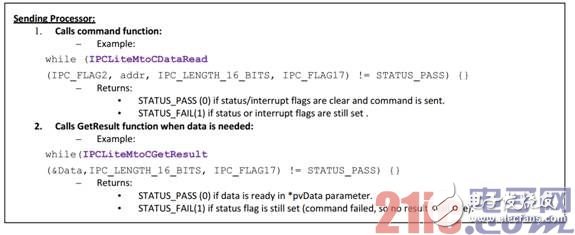

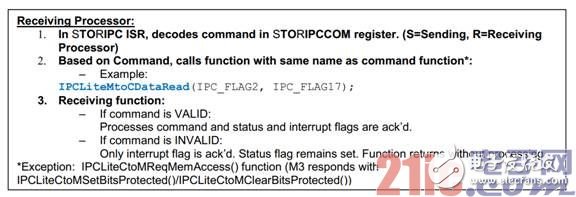

controlSUITE 軟件開發包中提供 2 種 IPC 的軟件驅動庫,IPC Driver 和 IPC_Lite Driver。IPC_Lite Driver 僅使用 IPC 寄存器來實現通信,不需要額外的 RAM,但是用戶只能支持一個 IPC 中斷服務 ISR,且不支持以隊列形式來處理 IPC 請求。IPC_Lite Driver 使用方式如下:

1,主動發起數據請求的內核會首先調用 IPC_Lite Driver 提供的名函數。在這個例子匯總,M3 是發送數據的內核并執行“IPCLiteMtoCDataRead” 函數。

? IPC_FLAG2 是 C28 中斷標志,指示 C28 內核一個消息到來。

? IPC_FLAG17 是響應標志,C28 用其指示 M3 核一個命令已經被處理。

? 需要讀取數據的 C28 的地址也被作為一個參數傳遞給 C28 內核。

? 這個函數在 while 循環中被調用的原因是,它可能返回 STATUS_FAIL 并且不會發送信息給C28 直至 MtoC IPC 中斷 2 和標志 17 可用, 之后,該函數返回 STATUS_PASS.

2,被動接收數據請求的內核會在 ISR 中解析其 IPCCOM寄存器的命令。這個例子中,C28 MtoCIPCINT2 ISR 知道標志置位,解析 MTOCIPCCOM寄存器的命令,識別出是讀數據命令。

3,被動接收數據請求的內核會調用與主動發起數據請求的內核相同的函數名。這個例子中,C28 執行 IPCLiteMtoCDataRead, IPC_FLAG2 作為中斷標志參數, IPC_FLAG17 作為狀態標志參數。

4,如果接收到命令有效,IPC_Lite 的驅動函數會處理讀命令并確認(acknowledges)狀態和中斷標志。如果接收到的命令無效,則只有中斷標志被確認(acknowledged)用來釋放中斷給后續的命令,而狀態標志仍然置位。

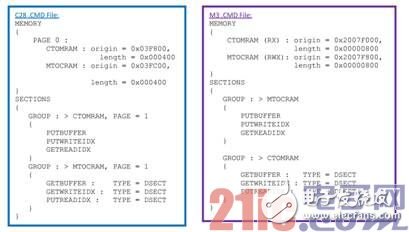

IPC Driver 通過在 Message RAM 中建立環形緩沖區,使得多個 IPC 通信命令可以以隊列的形式被緩沖,然后逐個處理,并且可以同時支持多個 IPC 中斷服務程序 ISR,當然,IPC Driver 需要更多的RAM 來支持。和 IPC-Lite 不同,為了使用 IPC 驅動,需要在 M3 和 C28 的項目中增加一些設置。

第一步是在 M3 和 C28 的鏈接定位文件(.cmd)中添加 IPC 循環緩沖區和指針段到 CTOM和 MTOC message RAM。如下所示:

第二步,應用程序源碼中必須定義并且初始化至少一個 volatile global tIpcController 變量 (為 C28 –M3 IPC 中斷使用),如下所示:

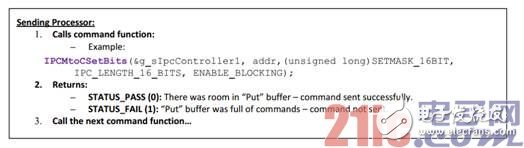

1. 主動發起數據請求的內核會首先調用 IPC Driver 提供的一個命令函數。這個例子中,M3 是發起數據請求的內核,執行“IPCMtoCSetBits”函數。

? g_sIpcController1 是 tIpcController 類型的變量,控制 M3 和 C28 IPC 中斷通道之間的通信。

? SETMASK_16BIT 是 16-bit 掩碼,指示應該被置位的位域。IPC_LENGTH_16_BITS 指示命令操作的數據對象是 16-bits。

? 函數被配置成允許阻塞 “ENABLE BLOCKING”, 意味著函數會一直等待直到 M3 PutBuffer 有空的緩沖區。如果函數被配置成不許阻塞 “DISABLE BLOCKING”, 一旦”Put”緩沖區滿,它會立即返回STATUS_FAIL 并且不會發送消息到 C28。如果”Put”緩沖區有空余,函數會返回 STATUS_PASS,

消息被成功發送到 C28.

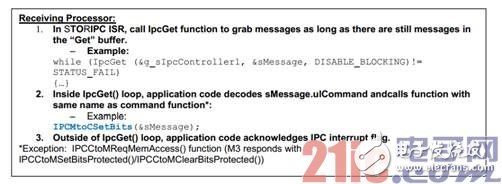

2. 被動接受數據請求的內核會連續調用 IpcGet 函數來讀取 sMessage 結構體里的消息,只要有消息在”Get”緩沖區。在 ISR 中 IpcGet 函數被調用,C28 側的 tIpcController 變量被用來綁定兩個相同的M3 和 C28 的 IPC 中斷通道(和 M3 側用來發送命令的 tIpcController 相同)。

3. 即使被動接收數據的內核沒有確認(acknowledged)IPC 中斷標志,主動請求數據的內核仍然可以連續發送消息,因為 tIpcController 變量會把消息排隊放到”Put”緩沖區(與被動接收數據請求的內核的”Get”緩沖區相同)。被動接收數據請求的內核的 ISR 會連續獲取并處理消息,直至”Get”緩沖區為

空。

4、Cortex M3 和 C28x 核的任務分工

Cortex-M3 子系統的優勢在于處理事務和管理通訊外設的能力,C28x 內核子系統在實時控制和數據處理方面性能優越。因此,在一個系統中,合理地分配兩個子系統的所處理的事務,優化資源的配置是至關重要的。基于 Concerto 的系統,一方面應當最大化地使用 C28x 的 DSP 和實時控制優勢,發揮ADC、PWM、C28x 組成的閉環系統的優勢;另一方面應將人機界面、通訊協議棧、文件系統等盡可能運行在 Cortex-M3 子系統一側。下面通過兩個應用案例來討論如何通過合理任務分工來提高系統效率。

4.1 光伏逆變器網絡節點

光伏逆變器的主要功能是把光伏面板輸出的 DC 直流電逆變為 110V/220V 的 AC 交流電,最終接入電網或者離網輸電至用電設備。在一個大功率的光伏發電網絡拓撲中,往往有許多個光伏逆變器,這些逆變器需要被監測,控制中心需要實時觀測各個光伏逆變器的工作狀態。因此,光伏逆變器網絡節點的功能主要包括 DC/AC 逆變器和網絡連接。如圖 9 所示,C28x 子系統(運行于 100MHz)完成MPPT 和 DC/AC 逆變算法。網絡連接可以有多種方式,常用的方式包括 Ethernet 以太網、RS485 或CAN 等,TMS320F28M35H52C 的 Cortex-M3 子系統(100 MHz)帶 Ethernet、RS485 和 CAN 等接口,支持多種有線和無線連接功能。

圖 8 Solar HV DC-AC Kit

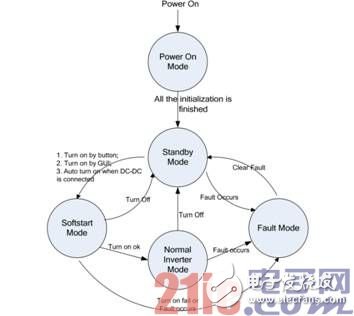

對于 C28x 子系統,采用狀態機的設計思路來區別不同的系統狀態。不同的狀態代表著不同的運行模式,其它的任務能夠根據特定的運行模式采取相應的行動。例如,可以采用下面 5 種不同的運行模式。

? Power On Mode: 系統上電后進入 Power On Mode,系統上電后,F28M35H52C1 中的 Cortex-M3內核 boot 程序首先啟動,此時 C28x 控制子系統和模擬子系統處于復位狀態,需要 M3 主子系統將其從復位狀態解除。M3 主子系統設定 M3 和 C28x 內核的時鐘頻率,由于 M3 和 C28x 的主頻之比必須

為整數比,因此 M3 和 C28x 的主頻設定只能為 60/60MHz、75/150MHz、100/100MHz。在 M3 和C28x 的主頻設定完成之后,需要由 M3 主子系統對整個芯片的外設資源以及 GPIO 進行配置,來決定哪些 GPIO 可以由 C28x 控制子系統進行配置。本系統中 M3 和 C28x 主頻設定為 75/150MHz。當所有的初始化操作完成后,系統自動轉入到 Standby Mode。

? Standby Mode:所有的 PWM 和繼電器被關閉。系統等待啟動命令,也檢測是否發生錯誤。

? Soft Start Mode: 接收到啟動命令,系統進入軟啟動模式,PWM 和繼電器開啟。如果啟動成功而且沒有錯誤發生,系統自動進入正常逆變模式。

? Normal Inverter Mode: 該模式下系統輸出功率,如果沒有錯誤發生也沒有收到關閉命令,系統會一直處于這個模式。

? Fault Mode: 如果發生錯誤,例如母線過壓,系統立即進入 Fault Mode。所有 PWM 輸出被封鎖,輸出繼電器被斷開。Fault 狀態可以被按鍵或者 GUI清除。清除后,系統會返回到Standby Mode

圖 90 C28x 端程序系統狀態機

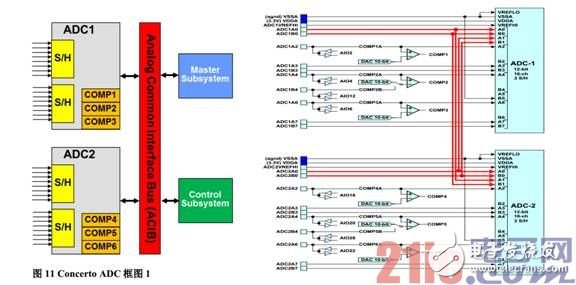

圖 101 Concerto ADC 框圖

Concerto 系列有兩個 12-bit ADC 模塊,每個 ADC 模塊包含兩個采樣保持電路,支持同步或者順序采樣模式,3 個帶 10-bitDAC 的模擬比較器,模擬信號的輸入范圍 0V~3.3V( 內部參考)或者VREFHI/VREFLO 比例關系(外部參考)。

圖 11 給出了詳細的 ADC 配置,TMS320F28M35H52C 的 Cortex-M3 和 C28x 內核都能夠訪問 ADC的結果寄存器,而且 2 個 ADC 模塊共享 4 個模擬輸入, Concerto ADC 模塊的這個特性允許對關鍵信號進行安全性驗證,提高系統的可靠性。

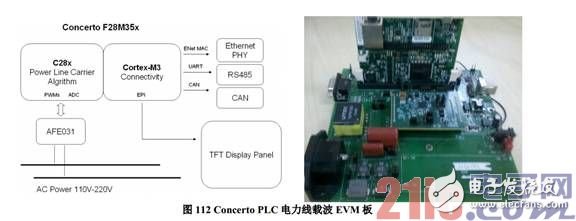

智能家居網關能夠將房間內的智能電器以有線或者無線的方式組成網絡,集中進行管理。如圖 10 所示,TMS320F28M35H52C 的 C28x(運行于 150MHz)主要完成電力線載波通信(Power Line CarrierCommunication)PLC 的 OFDM 物理層算法。Cortex-M3(75MHz)的運行 TCP/IP 協議接入以太網,其次,可選地通過 UART 接口外接 GPRS 模塊或者通過 EBI 外擴總線連接 TFT 彩屏用戶界面。

5、總結

Concerto C2000 異構雙核 MCU 將 C28x DSP 內核與 ARM 公司的 Cortex-M3 內核融合在一起,展示出高效的數據處理、數據通訊和事件管理的強大性能。C28x 和 Cortex-M3 兩個子系統分工明確,又通過 IPC 模塊巧妙實現了實時高效地核間通訊。在軟件方面,controlSUITE 開發平臺提供多種組件,包括 TCP/IP 協議棧、IPC 驅動、USB 協議棧、FAT 文件系統等,可幫助用戶更快地開發出創新性的產品。

電子發燒友App

電子發燒友App

評論