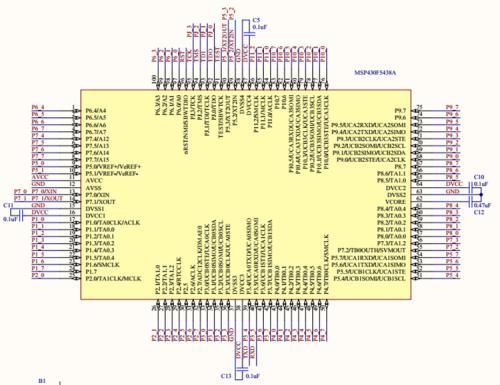

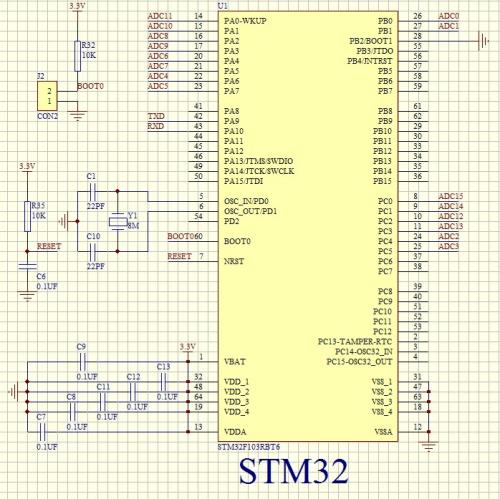

一、GPIO的綜合描述

stm32每一個(gè)GPIO端口擁有2個(gè)32bits的configuration寄存器(GPIOx_CRL,GPIOx_CRH),2個(gè)32bits的數(shù)據(jù)寄存器(GPIOx_IDR,GPIOx_ODR),1個(gè)32bits的set/reset寄存器(GPIOx_BSRR),1個(gè)16bits的reset寄存器(GPIOx_BRR)和1個(gè)32bits的Lock寄存器(GPIOx_LCKR)。

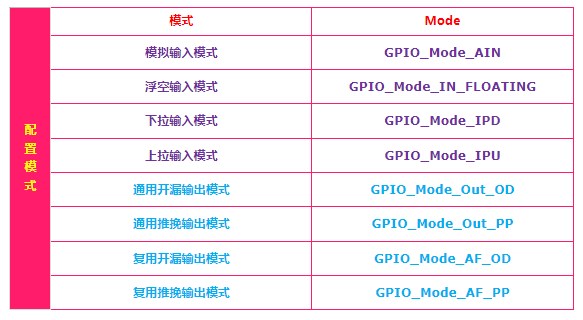

(一)每一個(gè)IO引腳都可以使用軟件配置為以下幾種模式:

1. 浮空輸入

2. 帶上拉輸入

3. 帶下拉輸入

4. 模擬輸入

5. 開漏輸出——(此模式可實(shí)現(xiàn)hotpower說的真雙向IO)

6. 推挽輸出

7. 復(fù)用功能的推挽輸出

8. 復(fù)用功能的開漏輸出

模式7和模式8需根據(jù)具體的復(fù)用功能決定。

每一個(gè)IO引腳都可以單獨(dú)編程,但是每一個(gè)IO寄存器只能32bits訪問(半字或者字節(jié)訪問都被禁止)。

(二)專門的寄存器(GPIOx_BSRR和GPIOx_BRR)實(shí)現(xiàn)對GPIO口的原子操作,即回避了設(shè)置或清除I/O端口時(shí)的“讀-修改-寫”操作,使得設(shè)置或清除I/O端口的操作不會被中斷處理打斷而造成誤動(dòng)作。

(三)每個(gè)GPIO口都可以作為外部中斷的輸入,便于系統(tǒng)靈活設(shè)計(jì)。

(四)I/O口的輸出模式下,有3種輸出速度可選(2MHz、10MHz和50MHz),這有利于噪聲控制。

(五)所有I/O口兼容CMOS和TTL,多數(shù)I/O口兼容5V電平。

(六)大電流驅(qū)動(dòng)能力:GPIO口在高低電平分別為0.4V和VDD-0.4V時(shí),可以提供或吸收8mA電流;如果把輸入輸出電平分別放寬到1.3V和VDD-1.3V時(shí),可以提供或吸收20mA電流。

(七)具有獨(dú)立的喚醒I/O口。

(八)很多I/O口的復(fù)用功能可以重新映射。

(九)GPIO口的配置具有上鎖功能,當(dāng)配置好GPIO口后,可以通過程序鎖住配置組合,直到下次芯片復(fù)位才能解鎖。此功能非常有利于在程序跑飛的情況下保護(hù)系統(tǒng)中其他的設(shè)備,不會因?yàn)槟承㊣/O口的配置被改變而損壞——如一個(gè)輸入口變成輸出口并輸出電流。

二、GPIO的配置

(一) GPIO模式選擇和速度匹配

(1) 浮空輸入_IN_FLOATING ——浮空輸入,可以做KEY識別,RX1。

(2)帶上拉輸入_IPU——IO內(nèi)部上拉電阻輸入。

(3)帶下拉輸入_IPD—— IO內(nèi)部下拉電阻輸入。

(4) 模擬輸入_AIN ——應(yīng)用ADC模擬輸入,或者低功耗下省電。

(5)開漏輸出_OUT_OD ——IO輸出0接GND,IO輸出1,懸空,需要外接上拉電阻,才能實(shí)現(xiàn)輸出高電平。當(dāng)輸出為1時(shí),IO口的狀態(tài)由上拉電阻拉高電平,但由于是開漏輸出模式,這樣IO口也就可以由外部電路改變?yōu)榈碗娖交虿蛔儭?梢宰xIO輸入電平變化,實(shí)現(xiàn)C51的IO雙向功能。

(6)推挽輸出_OUT_PP ——IO輸出0-接GND, IO輸出1 -接VCC,讀輸入值是未知的。

(7)復(fù)用功能的推挽輸出_AF_PP ——片內(nèi)外設(shè)功能(I 2C的SCL,SDA)

(8)復(fù)用功能的開漏輸出_AF_OD——片內(nèi)外設(shè)功能(TX1,MOSI,MISO.SCK)

GPIO輸出的速度匹配:

GPIO_Speed_10MHz 最高輸出速率10MHz

GPIO_Speed_2MHz 最高輸出速率2MHz

GPIO_Speed_50MHz 最高輸出速率50MHz

I/O口的輸出模式下,有3種輸出速度可選(2MHz、10MHz和50MHz),這個(gè)速度是指I/O口驅(qū)動(dòng)電路的響應(yīng)速度而不是輸出信號的速度,輸出信號的速度與程序有關(guān)(芯片內(nèi)部在I/O口的輸出部分安排了多個(gè)不同響應(yīng)速度的輸出驅(qū)動(dòng)電路,用戶可以根據(jù)自己的需要選擇合適的驅(qū)動(dòng)電路)。通過選擇速度來選擇不同的輸出驅(qū)動(dòng)模塊,達(dá)到最佳的噪聲控制和降低功耗的目的。高頻的驅(qū)動(dòng)電路,噪聲也高,當(dāng)不需要高的輸出頻率時(shí),請選用低頻驅(qū)動(dòng)電路,這樣非常有利于提高系統(tǒng)的EMI性能。當(dāng)然如果要輸出較高頻率的信號,但卻選用了較低頻率的驅(qū)動(dòng)模塊,很可能會得到失真的輸出信號。

有一點(diǎn)是關(guān)鍵,即GPIO的引腳速度跟應(yīng)用匹配(推薦10倍以上)。比如:

1) 對于串口,假如最大波特率只需115.2k,那么用2M的GPIO的引腳速度就夠了,既省電也噪聲小。

2 )對于I2C接口,假如使用400k波特率,若想把余量留大些,那么用2M的GPIO的引腳速度或許不夠,這時(shí)可以選用10M的GPIO引腳速度。

3 )對于SPI接口,假如使用18M或9M波特率,用10M的GPIO的引腳速度顯然不夠了,需要選用50M的GPIO的引腳速度。

(二) 在STM32中如何配置片內(nèi)外設(shè)使用的IO端口

①配置輸入的時(shí)鐘;②初始化后即被激活(開啟);③如果使用該外設(shè)的輸入輸出管腳,則需要配置相應(yīng)的GPIO端口(否則該外設(shè)對應(yīng)的輸入輸出管腳可以做普通GPIO管腳使用);④再對外設(shè)進(jìn)行詳細(xì)配置。

對應(yīng)到外設(shè)的輸入輸出功能有下述三種情況:

①外設(shè)對應(yīng)的管腳為輸出:需要根據(jù)外圍電路的配置選擇對應(yīng)的管腳為復(fù)用功能的推挽輸出或復(fù)用功能的開漏輸出。

②外設(shè)對應(yīng)的管腳為輸入:則根據(jù)外圍電路的配置可以選擇浮空輸入、帶上拉輸入或帶下拉輸入。

③ADC對應(yīng)的管腳:配置管腳為模擬輸入。

如果把端口配置成復(fù)用輸出功能,則引腳和輸出寄存器斷開,并和片上外設(shè)的輸出信號連接。將管腳配置成復(fù)用輸出功能后,如果外設(shè)沒有被激活,那么它的輸出將不確定。

(三) 通用IO端口(GPIO)初始化:

1、 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | B | C, ENABLE):使能APB2總線外設(shè)時(shí)鐘;

2 、RCC_ APB2PeriphResetCmd (RCC_APB2Periph_GPIOA | B | C, DISABLE):釋放GPIO復(fù)位;

3、配置各個(gè)PIN端口(模擬輸入_AIN、輸入浮空_IN_FLOATING、輸入上拉_IPU、輸入下拉_IPD、開漏輸出_OUT_OD、推挽式輸出_OUT_PP、推挽式復(fù)用輸出_AF_PP、開漏復(fù)用輸出_AF_OD)和匹配速度。

4 、GPIO初始化完成

附注1:PLL(Phase Locked Loop): 為鎖相回路或鎖相環(huán),用來統(tǒng)一整合時(shí)脈訊號,使內(nèi)存能正確的存取資料。PLL用于振蕩器中的反饋技術(shù)。許多電子設(shè)備要正常工作,通常需要外部的輸入信號與內(nèi)部的振蕩信號同步,利用鎖相環(huán)路就可以實(shí)現(xiàn)這個(gè)目的。

附注2:STM32的GPIO口的輸出:開漏輸出和推挽輸出

1、推挽輸出與開漏輸出的區(qū)別:

》》推挽輸出:可以輸出高,低電平,連接數(shù)字器件

》》開漏輸出:輸出端相當(dāng)于三極管的集電極。 要得到高電平狀態(tài)需要上拉電阻才行。 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對強(qiáng)(一般20ma以內(nèi))。

推挽結(jié)構(gòu)一般是指兩個(gè)三極管分別受兩互補(bǔ)信號的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止。

要實(shí)現(xiàn) 線與 需要用OC(open collector)門電路。是兩個(gè)參數(shù)相同的三極管或MOSFET,以推挽方式存在于電路中,各負(fù)責(zé)正負(fù)半周的波形放大任務(wù),電路工作時(shí),兩只對稱的功率開關(guān)管每次只有一個(gè)導(dǎo)通,所以導(dǎo)通損耗小,效率高。輸出既可以向負(fù)載灌電流,也可以從負(fù)載抽取電流。

當(dāng)端口配置為輸出時(shí):

開漏模式:輸出 0 時(shí),N-MOS 導(dǎo)通,P-MOS 不被激活,輸出0。

輸出 1 時(shí),N-MOS 高阻, P-MOS 不被激活,輸出1(需要外部上拉電路),也就是說此模式下只有 N-MOS對輸出起作用;此模式可以把端口作為雙向IO使用。

推挽模式:輸出 0 時(shí),N-MOS 導(dǎo)通,P-MOS 高阻,輸出0。

輸出 1 時(shí),N-MOS 高阻,P-MOS 導(dǎo)通,輸出1(不需要外部上拉電路)。

簡單來說,開漏是0的時(shí)候接GND ,1的時(shí)候浮空;推挽是0的時(shí)候接GND ,1的時(shí)候接VCC。

2、開漏電路特點(diǎn)及應(yīng)用

在電路設(shè)計(jì)時(shí)我們常常遇到開漏(open drain)和開集(open collector)的概念。所謂開漏電路概念中提到的“漏”就是指MOSFET的漏極。同理,開集電路中的“集”就是指三極管的集電極。開漏電路就是指以MOSFET的漏極為輸出的電路。一般的用法是會在漏極外部的電路添加上拉電阻。完整的開漏電路應(yīng)該由開漏器件和開漏上拉電阻組成。

組成開漏形式的電路有以下幾個(gè)特點(diǎn):

1) 利用 外部電路的驅(qū)動(dòng)能力,減少IC內(nèi)部的驅(qū)動(dòng)。當(dāng)IC內(nèi)部MOSFET導(dǎo)通時(shí),驅(qū)動(dòng)電流是從外部的VCC流經(jīng)R pull-up ,MOSFET到GND。IC內(nèi)部僅需很下的柵極驅(qū)動(dòng)電流。

2) 可以將多個(gè)開漏輸出的Pin,連接到一條線上。形成 “與邏輯” 關(guān)系。當(dāng)PIN_A、PIN_B、PIN_C任意一個(gè)變低后,開漏線上的邏輯就為0了。這也是I2C,SMBus等總線判斷總線占用狀態(tài)的原理。

3)可以利用改變上拉電源的電壓,改變傳輸電平。IC的邏輯電平由電源Vcc1決定,而輸出高電平則由Vcc2決定。這樣我們就可以用低電平邏輯控制輸出高電平邏輯了。

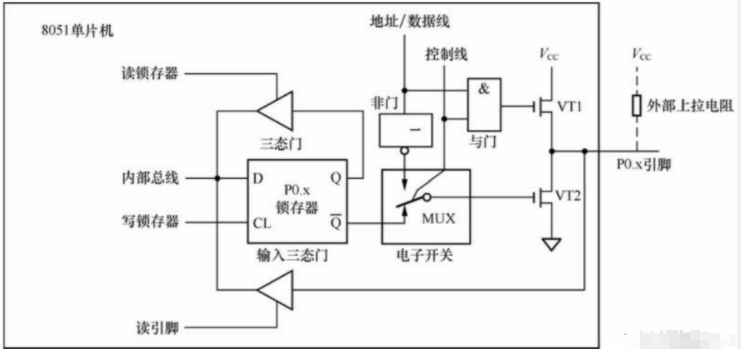

4)開漏Pin不連接外部的上拉電阻,則只能輸出低電平(因此對于經(jīng)典的51單片機(jī)的P0口而言,要想做輸入輸出功能必須加外部上拉電阻,否則無法輸出高電平邏輯)。

5)標(biāo)準(zhǔn)的開漏腳一般只有輸出的能力。添加其它的判斷電路,才能具備雙向輸入、輸出的能力。

應(yīng)用中需注意:

1) 開漏和開集的原理類似,在許多應(yīng)用中我們利用開集電路代替開漏電路。例如,某輸入Pin要求由開漏電路驅(qū)動(dòng)。則我們常見的驅(qū)動(dòng)方式是利用一個(gè)三極管組成開集電路來驅(qū)動(dòng)它,即方便又節(jié)省成本。

2)上拉電阻R pull-up的 阻值 決定了 邏輯電平轉(zhuǎn)換的沿的速度 。阻值越大,速度越低功耗越小。反之亦然。

責(zé)任編輯;zl

電子發(fā)燒友App

電子發(fā)燒友App

評論