0 引言

隨著智能化的發(fā)展以及物聯(lián)網(wǎng)的興起,微控制器(Micro Control Unit,MCU)主控芯片得到了越來越多的應(yīng)用。當(dāng)前MCU主控芯片一般都用NOR Flash作為片上系統(tǒng)存儲(chǔ)器,進(jìn)行指令和數(shù)據(jù)存取,根據(jù)應(yīng)用,用戶可以對(duì)片上Flash的指定區(qū)域進(jìn)行擦寫。在工業(yè)電力控制的應(yīng)用中,在線升級(jí)(In Application Programming,IAP)是一種常用的操作,意思是“在應(yīng)用編程”,即在程序運(yùn)行時(shí),程序存儲(chǔ)器可由程序自身進(jìn)行擦寫。具體來說,就是將片上Flash存儲(chǔ)器分為bootloader(IAP)程序和USER APP程序兩部分,當(dāng)需要在線升級(jí)時(shí),bootloader中的IAP程序通過外部通信接口接收數(shù)據(jù),然后擦除和寫入U(xiǎn)SER APP部分,同時(shí)寫入更新標(biāo)志,然后系統(tǒng)重新啟動(dòng)執(zhí)行USER APP程序,達(dá)到在線升級(jí)的目的。

通常有些主控芯片會(huì)要求IAP程序調(diào)用的Flash擦寫程序要在SRAM中執(zhí)行,IAP程序到USER APP程序跳轉(zhuǎn)需要進(jìn)行中斷向量表重映射。擦寫Flash USER APP程序區(qū)域過程中,要求CPU不能對(duì)Flash發(fā)起讀操作,如果發(fā)生,則不能正確返回讀取結(jié)果。

本文給出了一種支持IAP流程的兩片F(xiàn)lash拼接的Flash控制器方案,IAP程序直接在Flash執(zhí)行,IAP程序到USER APP程序跳轉(zhuǎn)提供一種快速方法,通過硬件直接完成地址映射。IAP程序執(zhí)行過程中,CPU可以對(duì)Flash發(fā)起讀指令操作,擦寫結(jié)束能正確返回讀結(jié)果。

1 NOR Flash器件

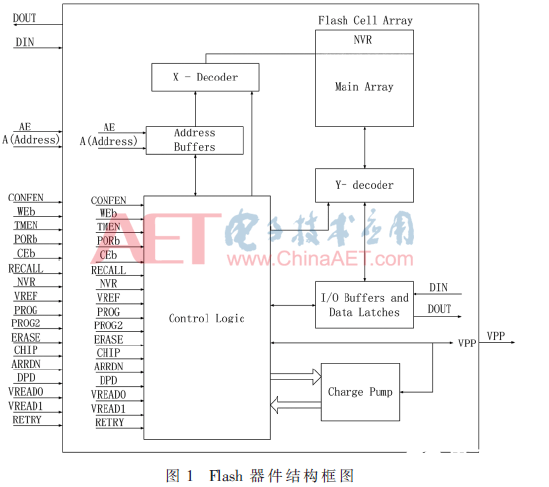

本文采用的NOR Flash IP基于UMC55 nm工藝,型號(hào)是UM055EFLLP128KX032CBA,讀寫位寬32 bit,地址線17 bit。main區(qū)總?cè)萘? Mb(1 K×128×32 bit),1 K個(gè)扇區(qū);NVR區(qū)總?cè)萘?6 Kb(4×128×32 bit),4個(gè)扇區(qū)。每個(gè)扇區(qū)容量為128×32 bit=4 Kb,每個(gè)扇區(qū)包含2個(gè)頁,每個(gè)頁包含64個(gè)word(1個(gè)word為32 bit)。結(jié)構(gòu)框圖如圖1所示。

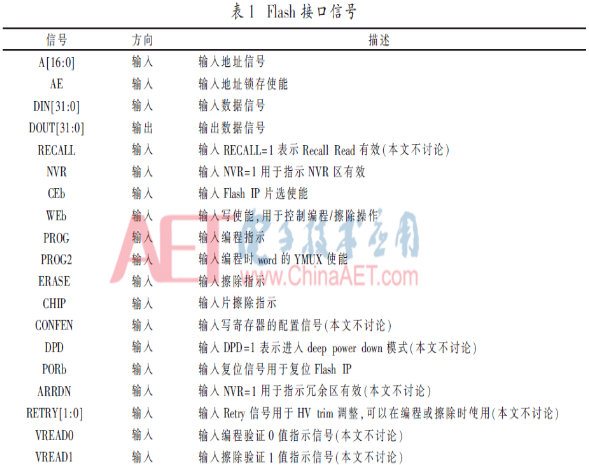

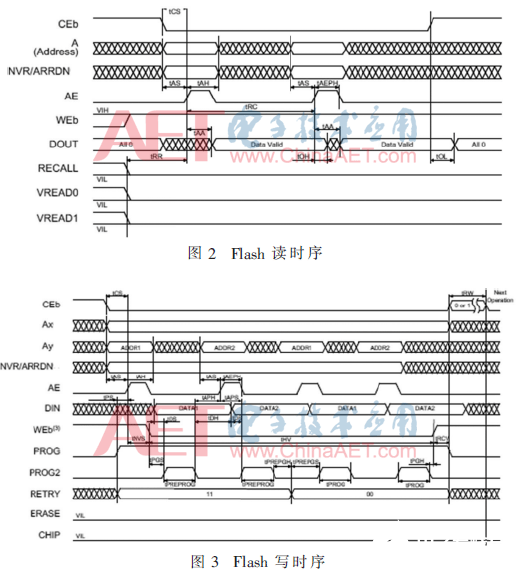

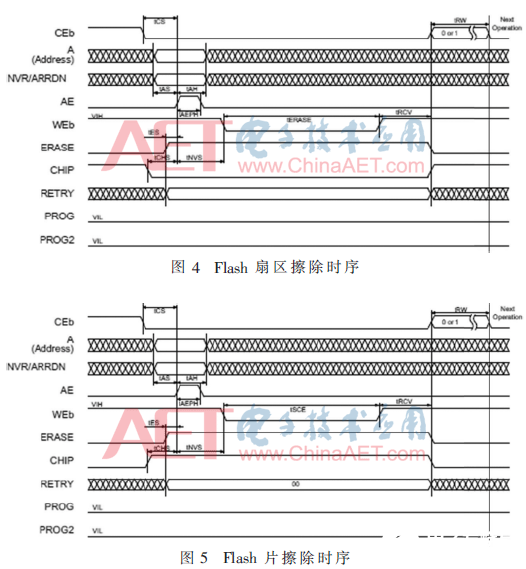

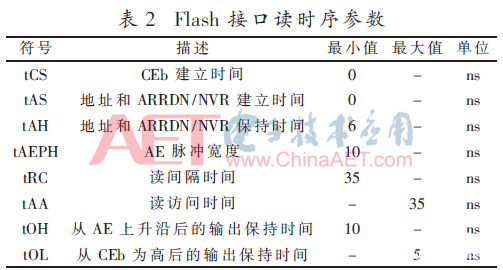

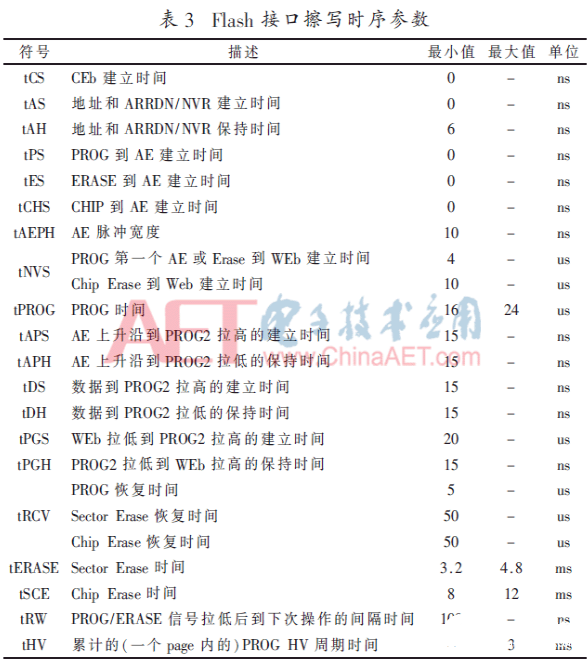

NOR Flash器件的操作分為讀、寫、扇區(qū)擦除、片擦除操作。時(shí)序圖如圖2~圖5所示。

Flash讀時(shí)序,發(fā)起AE脈沖鎖定地址,tAA時(shí)間之后讀出數(shù)據(jù)有效。

Flash寫時(shí)序,先拉高PROG信號(hào),然后AE脈沖鎖定地址,產(chǎn)生PROG2脈沖寫入對(duì)應(yīng)數(shù)據(jù)。PROG拉高持續(xù)時(shí)間是tHV,也就是說寫入時(shí)間是用戶自己控制的。根據(jù)tHV的時(shí)間不同,可寫入的word個(gè)數(shù)也不同。本文只討論單個(gè)word的寫入。

Flash扇區(qū)擦除時(shí)序,扇區(qū)擦除起始要用AE鎖定扇區(qū)地址,拉起ERASE信號(hào),執(zhí)行擦除時(shí)序。ERASE時(shí)間由tERASE時(shí)間參數(shù)控制。

Flash片擦除時(shí)序,擦除起始要用AE鎖定任意地址,片擦除除了拉高ERASE信號(hào),還要拉起CHIP信號(hào)。ERASE時(shí)間由tSCE時(shí)間參數(shù)控制。

2 控制器方案

2.1 結(jié)構(gòu)框圖

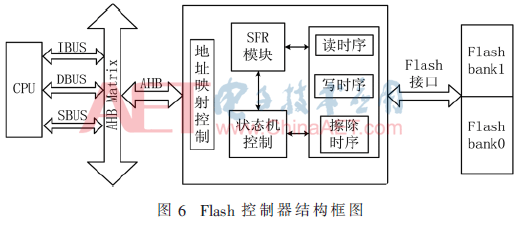

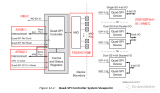

Flash控制器模塊在SoC系統(tǒng)中位于AHB matrix總線矩陣和Flash器件之間,CPU為ARM Cortex M4,總線為哈佛結(jié)構(gòu)。CPU可以通過IBUS和DBUS對(duì)Flash器件進(jìn)行訪問。Flash控制器結(jié)構(gòu)框圖如圖6所示。

Flash控制器實(shí)現(xiàn)了CPU對(duì)Flash器件的讀、寫和擦除。支持CPU在Flash中執(zhí)行程序的同時(shí)可以對(duì)Flash其他區(qū)域進(jìn)行擦寫。Flash支持在大于1 MHz的多種頻率下能對(duì)Flash器件進(jìn)行擦寫。

Flash控制器包含地址映射控制模塊、SFR模塊、狀態(tài)機(jī)控制模塊、時(shí)序轉(zhuǎn)化模塊。地址映射控制模塊用于在線升級(jí)時(shí)對(duì)AHB訪問地址進(jìn)行映射;SFR模塊用于Flash控制器的模式控制選擇,配置和狀態(tài)寄存器寄存等;狀態(tài)機(jī)控制模塊用于Flash控制器對(duì)各種模式的工作狀態(tài)控制;時(shí)序轉(zhuǎn)換模塊用于根據(jù)狀態(tài)機(jī)的當(dāng)前狀態(tài)來產(chǎn)生對(duì)應(yīng)的Flash器件的時(shí)序。

2.2 狀態(tài)機(jī)設(shè)計(jì)

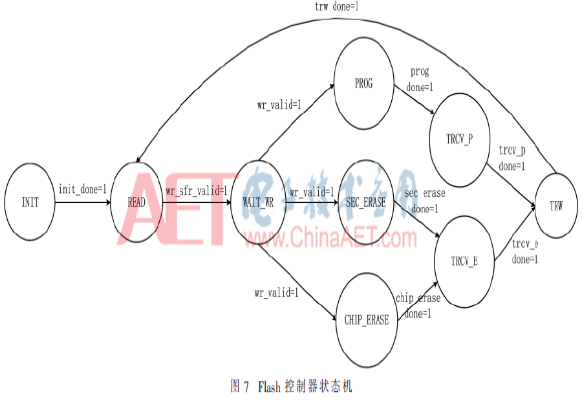

Flash控制器的狀態(tài)機(jī)如圖7所示,包含9個(gè)狀態(tài),INIT狀態(tài)完成Flash上電啟動(dòng),init_done之后進(jìn)入READ狀態(tài)。READ狀態(tài)下支持AHB總線讀操作。

如果要執(zhí)行擦寫,第一步則在READ狀態(tài)下配置SFR模塊的模式寄存器(PROG或者SEC_ERASE或者CHIP_ERASE),然后狀態(tài)機(jī)跳轉(zhuǎn)至WAIT_WR狀態(tài)(注:在WAIT_WR狀態(tài)也支持AHB總線讀操作)。

第二步當(dāng)AHB總線有寫操作,則狀態(tài)機(jī)跳轉(zhuǎn)至對(duì)應(yīng)的PROG或SEC_ERASE或CHIP_ERASE狀態(tài),開始對(duì)應(yīng)的擦寫時(shí)序轉(zhuǎn)化。時(shí)序轉(zhuǎn)化結(jié)束后,PROG跳轉(zhuǎn)到TRCV_P,SEC_ERASE和CHIP_ERASE跳轉(zhuǎn)到TRCV_E。之后跳轉(zhuǎn)到TRW狀態(tài),結(jié)束后返回READ狀態(tài)。

3 控制器實(shí)現(xiàn)分析

3.1 AHB總線數(shù)據(jù)相位擴(kuò)展原理

AMBA AHB總線的寫數(shù)據(jù)總線用來將數(shù)據(jù)從主機(jī)傳輸?shù)綇臋C(jī)上,而讀數(shù)據(jù)總線用來將數(shù)據(jù)從從機(jī)傳輸?shù)街鳈C(jī)上。

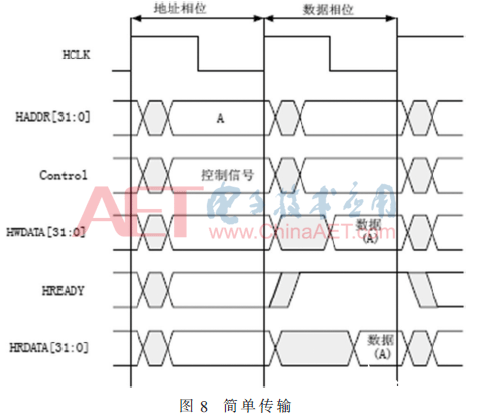

AHB總線基本傳輸包含兩個(gè)截然不同的部分:地址相位,只持續(xù)單個(gè)周期;數(shù)據(jù)相位,可能需要多個(gè)周期,這通過使用hready信號(hào)實(shí)現(xiàn)。

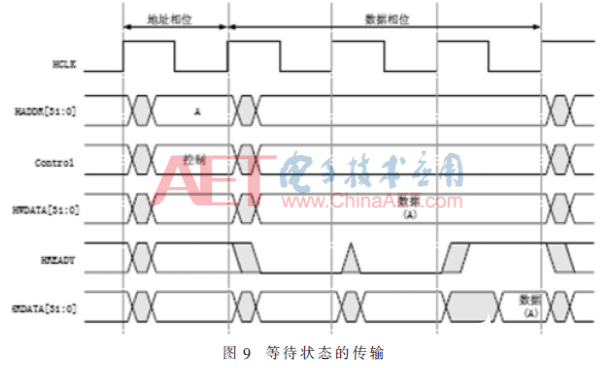

地址不長期有效,所以所有從機(jī)必須在這個(gè)時(shí)段(傳輸?shù)刂窌r(shí))采樣地址。然而,通過hready信號(hào)可以延長數(shù)據(jù)。當(dāng)該信號(hào)為低時(shí)導(dǎo)致在傳輸中插入等待狀態(tài)同時(shí)允許從機(jī)有額外的時(shí)間提供或者采樣數(shù)據(jù)。

圖8表示最簡單的傳輸,沒有等待狀態(tài)。在這個(gè)沒有等待狀態(tài)的簡單傳輸中,主機(jī)在HCLK的上升沿之后將地址和控制信號(hào)驅(qū)動(dòng)到總線上;然后在時(shí)鐘的下一個(gè)上升沿從機(jī)采樣地址和控制信息;在從機(jī)采樣了地址和控制信號(hào)后能夠開始驅(qū)動(dòng)適當(dāng)?shù)捻憫?yīng)并且該響應(yīng)被總線主機(jī)在第三個(gè)時(shí)鐘的上升沿采樣。

圖9為具有等待狀態(tài)的傳輸。從機(jī)插入等待周期(HREADY拉低)到任意傳輸中,這樣擴(kuò)展了傳輸完成允許的附加時(shí)間。對(duì)寫操作而言,總線主機(jī)必須保持?jǐn)?shù)據(jù)在整個(gè)擴(kuò)展周期中穩(wěn)定。

Flash控制器設(shè)計(jì)的擦寫模式狀態(tài)跳轉(zhuǎn)利用了數(shù)據(jù)相位擴(kuò)展階段數(shù)據(jù)保持的原理。

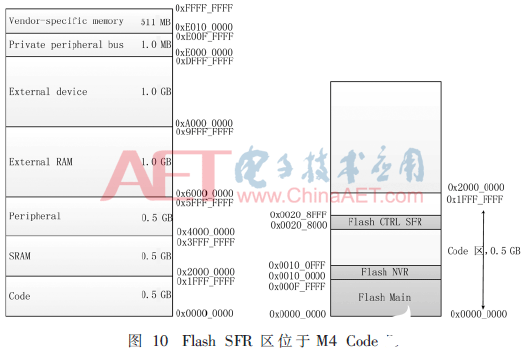

3.2 SFR區(qū)的位置

如圖10所示,F(xiàn)lash擦寫模式寄存器SFR區(qū)放在ARM cortex M4的Code區(qū),Code區(qū)指0.5 GB以下,即小于0x2000_0000地址的空間,Code區(qū)只能IBus/DBus總線通過AHB接口進(jìn)行訪問。不放在Peripheral區(qū)APB總線訪問,是為了避免IBus/DBus和SBus操作Flash的沖突。

以Flash寫操作為例,如果模式寄存器放在Peripheral區(qū)APB總線訪問,則CPU SBus配置完P(guān)ROG模式寄存器(訪問Peripheral區(qū)),準(zhǔn)備開始PROG時(shí)序轉(zhuǎn)換時(shí),CPU IBus/DBus可能還在讀取Flash操作中(訪問Code區(qū)),這樣控制器狀態(tài)機(jī)需要等待判斷讀結(jié)束才能跳轉(zhuǎn),控制不好可能Flash的PROG寫操作和讀操作會(huì)沖突。

如果模式寄存器放在Code區(qū),則會(huì)避免這種情況。配置寫模式寄存器的總線是CPU DBus(訪問Code區(qū)),配置同時(shí)必然不會(huì)有讀Flash(IBus/DBus訪問Code區(qū))的操作,因此下一刻即可以開始進(jìn)行狀態(tài)機(jī)從READ到WAIT_WR或WAIT_WR到PROG的跳轉(zhuǎn),WAIT_WR跳轉(zhuǎn)到PROG后會(huì)開始Flash PROG時(shí)序轉(zhuǎn)化。

3.3 Flash讀操作

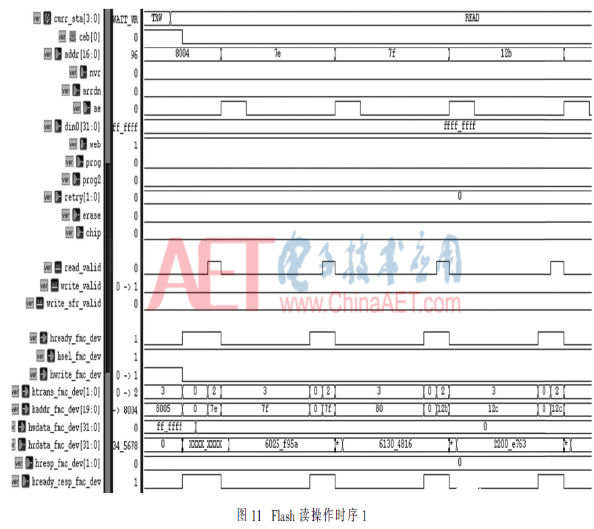

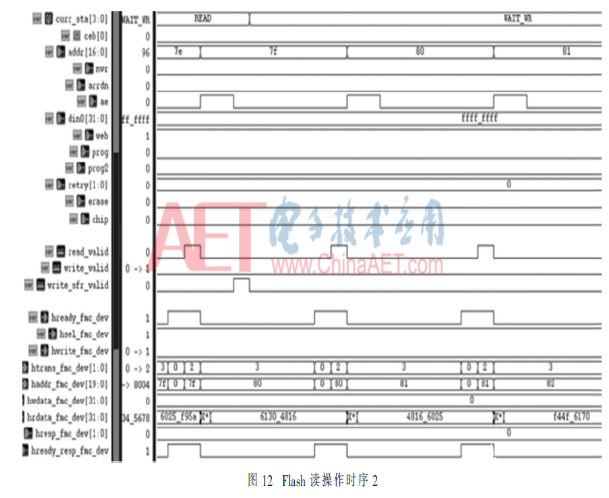

Flash讀操作,控制器可以直接將AHB總線讀操作進(jìn)行Flash讀時(shí)序轉(zhuǎn)換。Flash控制器的READ狀態(tài)和WAIT_WR狀態(tài)都支持AHB總線讀操作。

READ狀態(tài)的讀操作時(shí)序圖如圖11所示。

WAIT_WR狀態(tài)的讀操作時(shí)序圖如圖12所示。

3.4 Flash寫操作

控制器在PROG狀態(tài)可以完成Flash寫操作的時(shí)序轉(zhuǎn)化,采用hready拉總線方式。

進(jìn)入PROG狀態(tài)需要CPU執(zhí)行兩步總線寫操作,第一步,總線配置寫模式,第二步,總線寫操作給出寫地址,寫數(shù)據(jù)的采樣利用的就是AHB總線寫操作的數(shù)據(jù)在擴(kuò)展周期穩(wěn)定的原理。

詳細(xì)的Flash寫操作的步驟是:

(1)配置寫模式,READ狀態(tài)跳轉(zhuǎn)到WAIT_WR狀態(tài);

(2)在WAIT_WR狀態(tài),向目的地址發(fā)起AHB總線寫,狀態(tài)機(jī)跳轉(zhuǎn)到PROG狀態(tài),同時(shí)鎖定總線的寫地址,然后利用hready拉低時(shí)數(shù)據(jù)保持的原理,鎖定總線的寫數(shù)據(jù),然后進(jìn)行PROG時(shí)序轉(zhuǎn)化;

(3)在PROG狀態(tài),PROG信號(hào)拉高,PROG2產(chǎn)生寫脈沖,完成word的寫入。之后hready信號(hào)被釋放拉高,狀態(tài)機(jī)跳到TRCV_P,之后TRW,返回READ態(tài)。

注:如果在PROG狀態(tài)有AHB總線讀操作,hready會(huì)被拉低,讀控制信號(hào)和讀地址被鎖存,持續(xù)到編程時(shí)間結(jié)束,直到返回READ態(tài),正確返回讀結(jié)果。

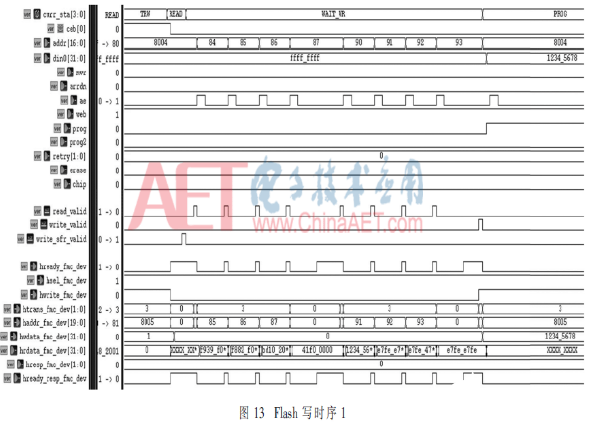

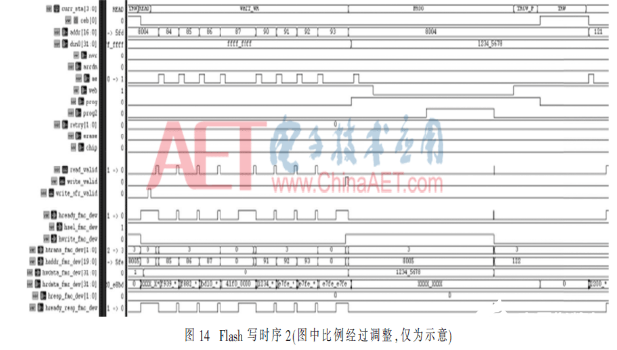

舉例:以圖13、圖14為例說明Flash寫操作時(shí)序。比如向0x00_8004地址(CPU地址0x0002_0010)寫入0x1234_5678數(shù)據(jù)。write_sfr_valid信號(hào)(配置PROG模式脈沖)觸發(fā)READ狀態(tài)跳到WAIT_WR狀態(tài),然后write_valid信號(hào)(AHB總線寫0x0002_0010地址,數(shù)據(jù)為0x1234_5678)觸發(fā)WAIT_WR狀態(tài)跳到PROG,開始時(shí)序轉(zhuǎn)化。

READ-》WAIT_WR-》PROG寫操作時(shí)序圖如圖13所示。

完整的寫操作PROG時(shí)序示意圖如圖14所示。

3.5 Flash擦除操作

Flash在SEC_ERASE和CHIP_ERASE狀態(tài)可以完成擦除操作的時(shí)序轉(zhuǎn)化。

進(jìn)入擦除操作需要CPU執(zhí)行兩步總線寫操作,第一步,配置擦除模式,第二步,總線寫操作給出擦除地址,對(duì)于扇區(qū)擦除,總線寫操作地址即是擦除地址,片擦除可以是任意地址。

以扇區(qū)擦除為例,詳細(xì)的步驟是:

(1)配置扇區(qū)擦除模式,READ狀態(tài)跳轉(zhuǎn)到WAIT_WR狀態(tài);

(2)在WAIT_WR狀態(tài),向目的扇區(qū)地址發(fā)起AHB總線寫,狀態(tài)機(jī)跳轉(zhuǎn)到SEC_ERASE狀態(tài),同時(shí)鎖定總線的寫地址,提取待擦除的扇區(qū)地址,然后hready信號(hào)拉低,進(jìn)行扇區(qū)擦除時(shí)序轉(zhuǎn)化;

(3)在SEC_ERASE狀態(tài),ERASE信號(hào)拉高,WEB信號(hào)拉低,ERASE信號(hào)持續(xù)時(shí)間達(dá)到配置Thv的值時(shí),狀態(tài)機(jī)跳到TRCV_E,之后TRW,返回READ態(tài)。

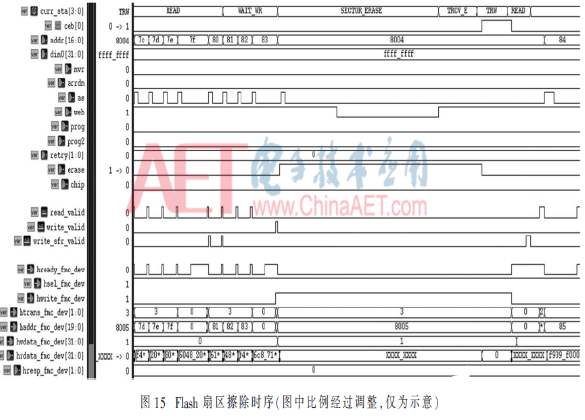

舉例:以圖15為例說明Flash扇區(qū)擦除時(shí)序。比如擦除0x00_8004扇區(qū)(CPU地址為0x0002_0010)。write_sfr_valid信號(hào)(配置SEC_ERASE模式脈沖)觸發(fā)READ狀態(tài)跳到WAIT_WR狀態(tài),然后write_valid 信號(hào)(AHB總線寫0x0002_0010地址)觸發(fā)WAIT_WR狀態(tài)跳到SEC_ERASE,開始時(shí)序轉(zhuǎn)化。

3.6 Flash自編程操作

Flash自編程操作即是Flash寫程序在Flash內(nèi)部執(zhí)行,同時(shí)對(duì)Flash其他區(qū)域進(jìn)行扇區(qū)擦除和寫操作的過程。

CPU每執(zhí)行一條指令的操作一般分為取指令、分析指令、執(zhí)行指令。轉(zhuǎn)化為對(duì)Flash的操作就是讀或?qū)憽@脤慒lash操作之后hready拉低,鎖定總線,進(jìn)行Flash讀寫時(shí)序轉(zhuǎn)化。

扇區(qū)擦除操作的分解步驟如下:

(1)(READ狀態(tài))讀Flash操作取指令;

(2)發(fā)起總線寫操作,配置扇區(qū)擦除模式寄存器(從READ跳轉(zhuǎn)到WAIT_WR);

(3)(WAIT_WR狀態(tài))讀Flash操作取指令;

(4)發(fā)起總線寫操作(從WAIT_WR跳轉(zhuǎn)到PROG);

(5)hready拉低,鎖定總線,同時(shí)從總線寫地址高bit提取Flash扇區(qū)地址(當(dāng)前總線寫數(shù)據(jù)不必關(guān)心),然后發(fā)起扇區(qū)擦除時(shí)序轉(zhuǎn)化;

(6)(從PROG跳轉(zhuǎn)到TRCV_E,然后TRW,返回READ)hready拉高,釋放總線,返回步驟(1)。

寫操作的分解步驟如下:

(1)(READ狀態(tài))讀Flash操作取指令;

(2)發(fā)起總線寫操作,配置寫模式寄存器(從READ跳轉(zhuǎn)到WAIT_WR);

(3)(WAIT_WR狀態(tài))讀Flash操作取指令;

(4)發(fā)起總線寫操作(從WAIT_WR跳轉(zhuǎn)到PROG);

(5)hready拉低,鎖定總線,同時(shí)鎖定總線當(dāng)前地址作為寫地址,利用hready拉低AHB總線數(shù)據(jù)擴(kuò)展周期期間寫數(shù)據(jù)不變原理鎖定當(dāng)前寫數(shù)據(jù),發(fā)起word寫時(shí)序轉(zhuǎn)化;

(6)(從PROG跳轉(zhuǎn)到TRCV_P,然后TRW,返回READ)hready拉高,釋放總線,返回步驟(1)。

3.7 IAP硬件地址映射

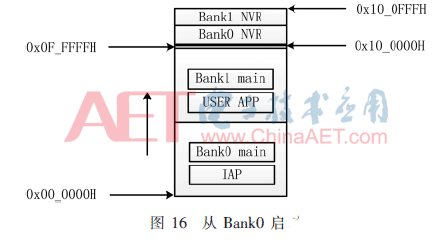

Flash控制器支持兩片F(xiàn)lash器件工作,F(xiàn)lash器件為UM055EFLLP128KX032CBA型號(hào),深度方向拼接,統(tǒng)一編址,main區(qū)(CPU地址)范圍從0x00_0000H~0x0F_FFFFH,NVR區(qū)(CPU地址)從0x10_0000~0x10_0FFFH。

正常情況下Flash Bank0位于低地址區(qū)域,F(xiàn)lashBank1位于高地址區(qū)域。正常啟動(dòng)時(shí)CPU從Bank0低地址區(qū)域開始執(zhí)行程序,如圖16所示。

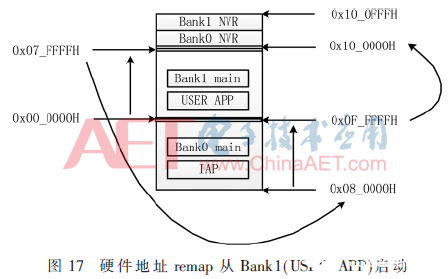

在IAP流程中,如果判斷待升級(jí)程序容量小于一個(gè)Bank容量,則可以使用這種快速在線升級(jí)方法,Boot-loader IAP程序放在Flash Bank0,將用戶程序USER APP程序?qū)懭隖lash Bank1中,然后寫入更新標(biāo)志位(標(biāo)志位放在Flash NVR區(qū))。發(fā)起系統(tǒng)軟復(fù)位,硬件將地址重映射,系統(tǒng)從Bank1高地址區(qū)域開始執(zhí)行程序,如圖17所示。

該設(shè)計(jì)不需要做中斷向量重映射,減少了軟件的復(fù)雜度,方便用戶使用。

3.8 時(shí)序參數(shù)隨頻率變化

Flash器件要在系統(tǒng)中正常工作,讀寫擦除的時(shí)序參數(shù)要滿足器件要求。而Flash控制器根據(jù)系統(tǒng)的要求,必須能在多種頻率下進(jìn)行正常讀寫和擦除,這些時(shí)序參數(shù)值是內(nèi)部若干個(gè)counter計(jì)數(shù)器根據(jù)頻率產(chǎn)生的。如果在每個(gè)特定頻率下,用軟件進(jìn)行一一重新配置所有的時(shí)序參數(shù)是比較繁瑣的。

本控制器將時(shí)序參數(shù)分為了兩類考慮,做了如下設(shè)計(jì):

(1)讀時(shí)序參數(shù)

Flash讀操作的各時(shí)序參數(shù)設(shè)計(jì)上已經(jīng)給出默認(rèn)值,能保證系統(tǒng)啟動(dòng)正常工作。需要考慮的主要參數(shù)是tAA,表示AE有效到dout數(shù)據(jù)有效的選通時(shí)間,F(xiàn)lash器件要求必須大于35 ns。本控制器設(shè)計(jì)了讀延遲參數(shù)值read_latency_cnt,根據(jù)不同頻率可以配置不同值以滿足要求并得到最快訪問速度。比如在Flash控制器工作時(shí)鐘為100 MHz時(shí),周期為10 ns,為滿足大于35 ns的時(shí)間,read_latency_cnt最小值需要配置為4。讀時(shí)序參數(shù)如表2所示。

(2)擦寫時(shí)序參數(shù)

擦寫時(shí)序各時(shí)序參數(shù)值設(shè)計(jì)上已經(jīng)給出默認(rèn)值,能保證系統(tǒng)啟動(dòng)正常工作。當(dāng)系統(tǒng)工作頻率變化時(shí),擦寫的各時(shí)序參數(shù)值也要滿足器件要求。

本控制器設(shè)計(jì)了工作頻率寄存器T1US_REF,含義是1 μs需要多少個(gè)時(shí)鐘周期,如果為60 MHz,則配置該寄存器為60,如果為100 MHz,則配置該寄存器為100。內(nèi)部的微秒級(jí)的各時(shí)序參數(shù)會(huì)自動(dòng)以該寄存器為基準(zhǔn)同步變化,這樣就減少了軟件根據(jù)不同頻率頻繁修改多個(gè)時(shí)序參數(shù)寄存器的復(fù)雜度。擦寫時(shí)序參數(shù)如表3所示。

4 結(jié)論

本文給出了基于ARM cortex m4 SoC架構(gòu)下兩片UMC55 nm Flash macro IP拼接工作的NOR Flash控制器的設(shè)計(jì),介紹了NOR Flash的讀、寫、擦各種時(shí)序的設(shè)計(jì)流程。

本控制器的特點(diǎn)如下:

(1)利用AMBA AHB hready信號(hào)為低時(shí)數(shù)據(jù)相位擴(kuò)展的原理,支持Flash在線編程,執(zhí)行過程中支持Flash讀操作。

(2)在IAP程序跳轉(zhuǎn)USER APP程序時(shí)不需要中斷向量表重定向,直接硬件地址映射實(shí)現(xiàn)。

(3)通過設(shè)定1 μs工作頻率配置寄存器,硬件自動(dòng)計(jì)算滿足不同頻率下的正常擦寫時(shí)序參數(shù),減少了軟件逐個(gè)配置多個(gè)時(shí)序參數(shù)的復(fù)雜度。

含有該Flash控制器的MCU主控芯片已經(jīng)通過仿真和FPGA驗(yàn)證,且在UMC55 nm工藝上流片成功,芯片樣品經(jīng)過測試,F(xiàn)lash控制器功能良好,方便使用。

參考文獻(xiàn)

[1] 謝同同,李天陽。一種嵌入式NOR Flash 控制器IP的設(shè)計(jì)[J]。電子與封裝,2016(7):18-21,43.

[2] 田鵬,聶澤東,張正平,等。一種兼容AHB總線的Nor Flash控制器IP設(shè)計(jì)[J]。微電子學(xué)與計(jì)算機(jī),2013(6):88-91,96.

[3] 周芝梅,趙東艷,張海峰,等。基于IR46標(biāo)準(zhǔn)的雙芯電能表主控關(guān)鍵技術(shù)研究[J]。電子技術(shù)應(yīng)用,2017,43(10):7-11,19.

[4] 蔣勁松,黃凱,陳辰,等。基于預(yù)取和緩存原理的片上Flash加速控制器設(shè)計(jì)[J]。計(jì)算機(jī)工程與科學(xué),2016(12):2381-2391.

[5] ARM.AMBA Specification(Rev 2.0)[Z].1999.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論