0 引言

隨著空間探測領域的逐漸擴大,航天器上的載荷設備對系統的數據通信需求也相應的越來越高。同時星載電子設備產生和待處理的數據總量迅猛增長,對數據總線處理能力提出更高的要求。數據總線的速度、可靠性和靈活性直接影響航天器的整體性能。歐洲航天局(European Space Agency,ESA)為滿足航空航天應用提出了一種專門用于空間高速數據傳輸的點對點串行總線標準SpaceWire[1]。它具有數據率高,便于擴展,方便重復利用的特點,有利于航天器、衛星快速整合總裝,這為航天器和衛星載荷的設計帶來極大方便,應用前景廣闊。

本文研究該標準下節點控制器IP[2]的實現方法,通過FPGA進行原型驗證,最后在專用集成芯片龍芯1E300中實現了該節點控制器,實際測試信號傳輸率可達200 Mb/s~260 Mb/s。

1 系統總體設計

1.1 系統結構框圖

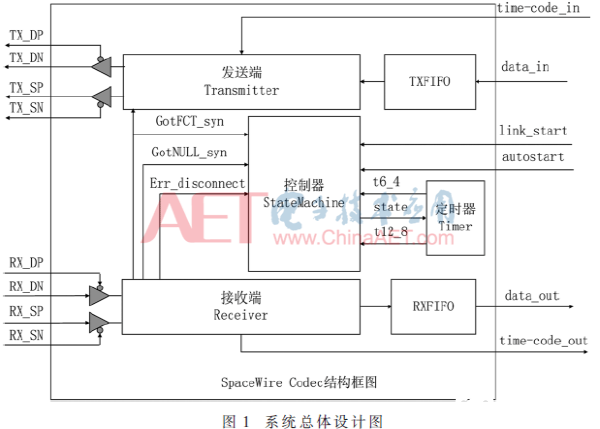

SpaceWire是一種點對點全雙工串行數據傳輸協議,節點控制器在協議中主要負責解決數據包點對點傳輸問題。本文設計的SpaceWire IP核使用FIFO作為用戶數據接口,并將數據發送和接收緩存包括在內。系統主要功能包括節點配置、鏈路狀態控制和數據收發功能,總體設計如圖1所示。

1.2 系統時鐘域劃分

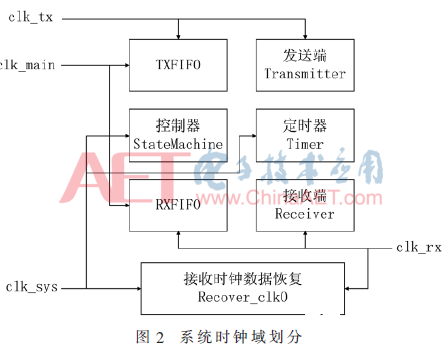

本設計必須使用到不同的時鐘,系統時鐘域的劃分[3]是設計的重點之一。如圖2所示,clk_sys是本設計中的頻率最高的時鐘域,同步系統控制器,并為系統提供定時功能。clk_main是來自上位機的時鐘,同步發送緩存的寫入和接收緩存的讀取操作。clk_tx指的是發送時鐘域,是同步發送端對發送數據的相關操作。clk_rx指的是恢復時鐘域,是由鏈路數據進行時鐘數據恢復所得到的時鐘,用來同步接收端對恢復數據的相關操作。根據SpaceWire協議,接收端在接收到首位數據以前還沒有產生恢復時鐘,而鏈路斷開檢測在首位數據接收時就已經開始,這里采用系統時鐘進行鏈路斷開檢測。

2 系統原理實現

2.1 系統狀態機

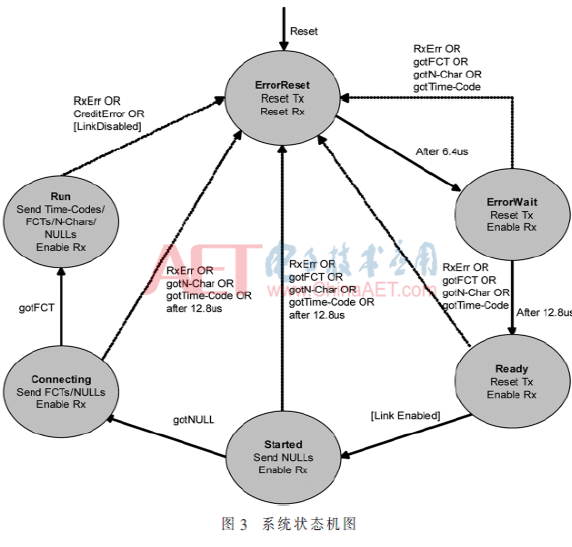

SpaceWire進行數據通信前要求兩端的節點先通過NULL字符和FCT字符交換完成鏈路建立過程,鏈路在運行過程中可能由于鏈路主動或被動斷開、數據傳輸錯誤等原因導致鏈路狀態變化。鏈路運行的狀態機如圖3所示,圖中實線表示鏈路初始化的過程,鏈路正確初始化后處于Run狀態。在應用中,鏈路兩端節點都可以被配置為主動或者被動模式[4],有如下條件:

Link_Enabled=(Not[Link_Disabled])And

([LinkStart] Or ([AutoStart] And gotNull))

2.2 發送端

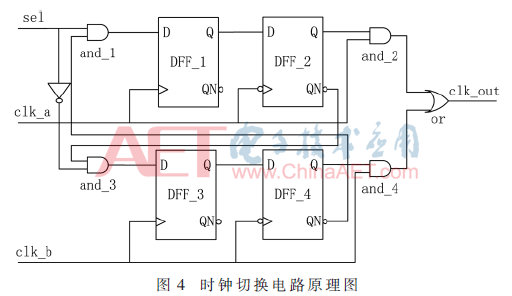

鏈路在初始化過程中,可能發送NULL字符和FCT字符,鏈路從初始化到運行的各個狀態轉換中,需要不間斷發送字符。SpaceWire協議規定的鏈路初始化速率為10 Mb/s,而運行速率可以是2 Mb/s~400 Mb/s,故要求發送時鐘速率可切換,發送端發送的比特流在數據發送頻率變化的時候保持不間斷,一種可用的時鐘切換[5]電路圖如圖4所示。

DFF_2和DFF_4保證clk_a和clk_b時鐘選擇輸出的變化都只發生在下降沿處,同時可以使得輸出變化為某一時鐘時,另一時鐘的輸出已經關閉,該方法可避免時鐘切換時候產生毛刺。DFF_1和DFF_3分別加到and_1和and_3后面,防止sel、DFF_2輸出和DFF_4輸出的信號同時變化可能造成的DFF_2和DFF_4輸出的亞穩態。

2.3 接收端

SpaceWire鏈路層采用DS編碼方案,選通信號伴隨著串行數據信號發送,接收端簡單地通過異或數據和選通信號可以提取出時鐘信號。該方法將接收偏差(skew)裕量從傳統的時鐘、數據方式的0.5比特時間提高到接近1比特時間,具有更好的抖動(jitter)容差。但由于接收數據的時鐘是由接收的DS編碼信號異或得到的,造成接收器的數據時鐘信號不同步,恢復困難。

為實現數據時鐘恢復,一種方法是基于Xilinx FPGA,選擇采用可編程絕對延遲單元iodelay實現對DS異或后的信號執行指定的延遲,可以正確地恢復出時鐘,根據圖5分析DS信號的特點[6]后,得到一種更通用的方法:

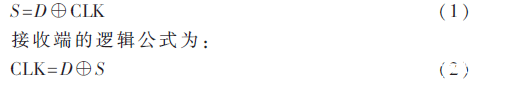

DS編碼如式(1)和式(2)定義:

發送端的邏輯公式為:

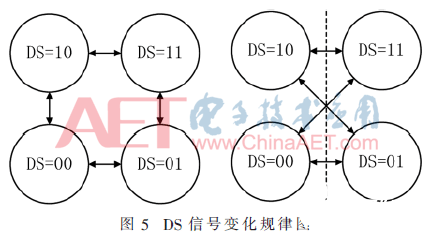

式中D為數據信號,S為選通信號,CLK為數據時鐘。根據DS信號變化的特點可以發現DS信號的每次轉換有且只變換其中的1位信號,通過2次變換后則DS數據都將發生翻轉,右圖能夠更清楚說明這一現象。

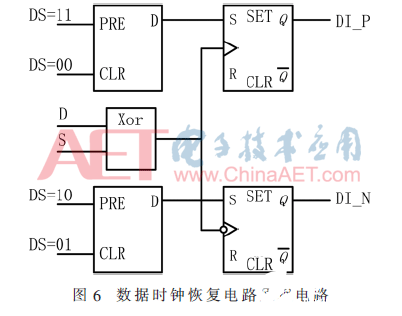

從圖5可知,當且僅當時鐘信號為上升沿時,data和strobe信號發生從同相至反相的跳變,如圖5右半部分中右象限;同理,當且僅當時鐘信號為下降沿時,data和strobe信號發生從反相至同相的跳變,如圖5右半部分中左象限。根據上述分析結論設計的DS數據時鐘恢復電路[7]如圖6所示。

圖6中電路由異或門、鎖存器、觸發器構成,當時鐘信號為上升沿時,同相狀態的data數據將保持不變,當時鐘信號為下降沿時,反相狀態的data數據將保持不變,從而保證了后級觸發器時鐘跳變時,觸發器數據信號的建立時間。觸發器輸出的2位數據即是同步接收的數據信號,輸出至后級接收模塊進行處理。

2.4 數據緩存

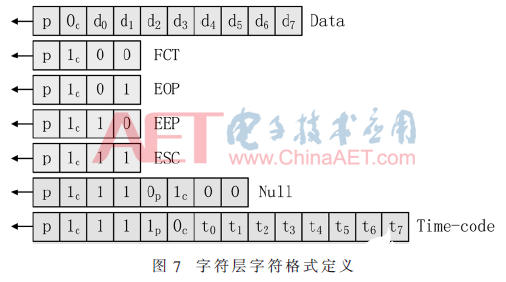

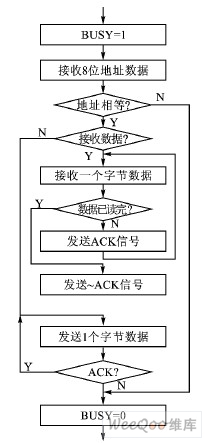

根據SpaceWire字符層定義,協議鏈路可能傳送5種字符和2種控制碼,其格式如圖7所示。

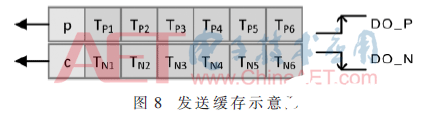

由于最長的時間控制碼字符包含14比特位,本設計中發送方采用2組7比特位數據緩存完成數據格式的轉換,采用DDR數據傳輸方式在時鐘的上升沿和下降沿分別發送其中的一組緩存數據,如圖8所示。在上次數據發送完成前的第二個時鐘周期計算校驗位,前一個時鐘周期向該發送緩存填充待發送字符后進行數據發送。接收方采用5對移位寄存器組,首先判定接收字符的起始位置,在進行奇偶校驗的同時,判別接收的字符類型,并保存至接收FIFO中。

圖7和圖8中標識為“p”或下標為“p”的比特位表示該位為字符的校驗位,標識為“c”或下標為“c”的比特位表示該位為字符的控制位,箭頭表示字符中比特位在鏈路上傳輸的先后順序。

2.5 流量控制機制

為避免因主機接收緩存溢出而導致的數據丟失,鏈路的一端(B端)向另一端(A端)發送FCT表示B端已經準備好,可以再接收一定量的數據。

2.5.1 信譽量計數值

發送端要維護一個授權它可發送的N-Char數量的信譽計數值(Credit Count),具體如下。

ErrorReset狀態下,信譽計數值為零,鏈路接口每接收到一個FCT,信譽量計數值就加8[8],每發送一個N-Char,信譽計數值就減1。信譽計數值為零時將停止發送N-Char,但可繼續發送L-Char,直到它再次接收到FCT使信譽計數增長到8。

信譽量計數最大值根據接收緩存的大小設置(1個FCT對應接收緩存中8個N-Char的存儲空間),不超過56(即7個FCT)。當信譽計數值達到或已經接近其最大值(即距最大值小于8)時又接收到一個FCT,那么信譽計數值不會再增長,同時會通過標志報信譽額度錯誤。

2.5.2 未償付計數值

鏈路接口要維護一個它預期接收但未償付的N-Char數量的計數值(Outstanding Count),即它通過發送FCT請求要發送的數量,具體如下。

復位時,初始未償付計數值為0,鏈路出錯時,未償付計數值被保存并在下次重啟時加載為初始值,每發送完一個FCT,未償付計數值就加8,每接收到一個N-Char,未償付計數值就減1。未償付計數值最大為56(即7個FCT)。除非未償付計數器有余量多計8個未償付N-Char,同時接收緩存有容納這8個N-Char的空間,否則發送器不能發送FCT。

3 測試與驗證

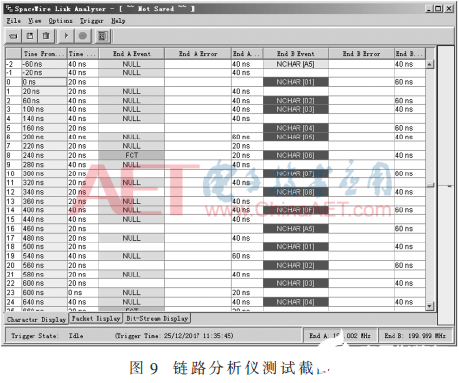

本系統FPGA選用Xilinx公司的Virtex 4系列 xc4vsx55作為主控芯片,使用Verilog語言編程[9]進行邏輯設計和驗證,在FPGA上同時例化兩個節點控制器,通過讀寫配置寄存器控制SpaceWire節點收發數據。從仿真結果可見,節點控制器實現了協議規定的鏈路初始化和數據傳輸功能,控制字符和數據在鏈路上的傳輸正確。

在專用集成芯片龍芯1E300中實現了該控制器,搭建測試環境,采用StarDundee公司的標準測試設備SpaceWire鏈路分析儀,與節點控制器芯片相互傳輸數據,驗證了數據傳輸過程中的同步性和準確性。鏈路分析儀測試結果如圖9所示,表明ASIC設計的節點控制器信號傳輸速率可達200 Mb/s,數據傳輸正常,滿足協議規定的功能。

4 結束語

SpaceWire作為航天領域新興的高速總線標準之一,具有數據率高、接口簡單、擴展方便等諸多優點。本文提出的一種SpaceWire節點控制器實現方法解決了設計中多時鐘域劃分、數據時鐘恢復、時鐘切換和流量控制方面的難點。該設計方法經FPGA仿真驗證正確,在專用集成芯片中成功實現,該節點控制器的研發設計具有較強的工程實用性。

參考文獻

[1] ECSS,ECSS-E-ST-50-12C.SpaceWire-links,nodes,routers and networks[S].Noordwijk,The Netherlands:ESA-ESTEC Requirements & Standards Division,2003.

[2] JULIUSSON D.The swift codec development[C].Space-Wire-2013 Proceedings of the 5th International SpaceWire Conference.Gothenburg,Sweden:Space Technology Centre,University of Dundee,2013:316-318.

[3] 唐萍,李慧軍.SpaceWire Codec接收端FPGA時序設計[J/OL]。微計算機信息,2009,25(2):178-179,198.

[4] CHRIS MCCLEMENTS,STEVE PARKES. SpaceWire standard:low speed signalling rates[C].SpaceWire-2008 Proceedings of the 2nd International SpaceWire Conference.Nara,Japan:Space Technology Centre,University of Dundee,2008:41-44.

[5] 魏家明.Verilog編程藝術[M]。北京:電子工業出版社,2014.

[6] NOMACHI M,ISHII S,KURODA Y,et al. Race condition free SpaceWire decoder for FPGA[C].SpaceWire-2010 Proceedings of the 3rd International SpaceWire Conference.St.Petersburg,Russia:Space Technology Centre,University of Dundee,2010:173-175.

[7] 閆夢婷,安軍社,龔泉銘。基于RMAP機制的SpaceWire星載高速總線設計與實現[J]。電子技術應用,2016,42(1):108-110,114.

[8] 趙云富,吳一帆,孫強,等.SpaceWire總線的流量控制機制研究[J/OL]。微電子學與計算機,2016,33(1):1-5.

[9] 夏宇聞.Verilog數字系統設計(第4版)[M]。北京:北京航空航天大學出版社,2017.

電子發燒友App

電子發燒友App

評論