描述此參考設(shè)計(jì)是基于 66AK2Gx DSP + ARM 處理器片上系統(tǒng) (SoC) 和配套 AIC3106 音頻編解碼器的參考平臺(tái),可提供實(shí)現(xiàn)音頻處理算法設(shè)計(jì)和演示的捷徑。該音頻解決方案設(shè)計(jì)包括

2018-10-19 15:35:45

DSP D 56371AF180 處理器是否包括 DSP B 56371AF180 的所有功能?也就是說(shuō),DSP D 56371 在其軟件代碼中有 Generic、mini-SA 和 PPP 作為其

2023-06-02 08:46:52

DSP處理器與通用處理器的比較1 對(duì)密集的乘法運(yùn)算的支持GPP不是設(shè)計(jì)來(lái)做密集乘法任務(wù)的,即使是一些現(xiàn)代的GPP,也要求多個(gè)指令周期來(lái)做一次乘法。而DSP處理器使用專門的硬件來(lái)實(shí)現(xiàn)單周期乘法。DSP

2021-09-03 08:12:55

對(duì)比項(xiàng)屬性/特征 硬件乘法器/累加器AUL 通用的MCU在執(zhí)行乘法操作時(shí)是通過(guò)軟件編程的方式的來(lái)實(shí)現(xiàn)的,通常需要幾十甚至上百個(gè)時(shí)鐘周期,而DSP處理器卻有自己的硬件乘法器,使用硬件的方式來(lái)執(zhí)行乘法

2021-11-03 08:41:44

怎樣根據(jù)某些條件選擇DSP處理器的類型?比如:要求數(shù)據(jù)輸出時(shí)間間隔為1ms,速度數(shù)據(jù)類型為1個(gè)浮點(diǎn)型類型數(shù)據(jù)。急求大神指導(dǎo)!謝謝了!我對(duì)DSP處理器不太了解,暫時(shí)會(huì)用到這個(gè)技術(shù)。求指導(dǎo)!

2013-06-08 23:33:51

處理器存貯器的帶寬加倍,更重要的是同時(shí)為處理器核提供數(shù)據(jù)與指令。在這種布局下,DSP得以實(shí)現(xiàn)單周期的MAC指令。 還有一個(gè)問(wèn)題,即現(xiàn)在典型的高性能GPP實(shí)際上已包含兩個(gè)片內(nèi)高速緩存,一個(gè)是數(shù)據(jù),一個(gè)

2011-01-07 15:34:45

指令。還有一個(gè)問(wèn)題,即現(xiàn)在典型的高性能GPP實(shí)際上已包含兩個(gè)片內(nèi)高速緩存,一個(gè)是數(shù)據(jù),一個(gè)是指令,它們直接連接到處理器核,以加快運(yùn)行時(shí)的訪問(wèn)速度。從物理上說(shuō),這種片內(nèi)的雙存儲(chǔ)器和總線的結(jié)構(gòu)幾乎與哈佛

2008-06-19 15:19:47

ADSP2106x的Link口組成多DSP互連并行系統(tǒng) 首先對(duì)ADSP2106x做一簡(jiǎn)單介紹。ADSP2106x是一種高性能的32 b數(shù)字信號(hào)處理器,采用超級(jí)哈佛結(jié)構(gòu)。內(nèi)有3條片內(nèi)總線,他們是PM總線(程序存貯器

2019-04-08 09:36:19

本帖最后由 tianyi223 于 2015-9-9 20:34 編輯

兩個(gè)dsp之間sci通信的話 數(shù)據(jù)會(huì)移位嗎,會(huì)的話怎么解決,如果不會(huì)為什么發(fā)送正確,接收到的卻是亂碼

2015-09-09 15:30:07

我沒(méi)有在當(dāng)前文檔中找到明確的答案:兩個(gè)內(nèi)核同時(shí)訪問(wèn) SRAM 是如何處理的??jī)?nèi)部 SRAM 是雙端口的(我的意思是兩個(gè)內(nèi)核可以在沒(méi)有額外等待狀態(tài)的情況下尋址和訪問(wèn)同一個(gè) SRAM),還是存在某種仲裁

2023-03-01 06:49:21

TI工程師,您好!我們計(jì)劃兩片DSP(28377)之間用SPI通信,還有一些DI和DO的信號(hào)交互。請(qǐng)問(wèn)是否可以將兩片DSP管腳直接連接在一起?是否中間需要串入電阻或者其他邏輯門器件?應(yīng)用中有什么需要注意的地方嗎?

2018-09-20 14:13:37

的是DSP133.33MHZ,當(dāng)時(shí)鐘上升沿來(lái)到的時(shí)候,讀取DSP地址線上的數(shù)據(jù),存入sram_wa中。lcd_sram1_d和lcd_sram2_d是從DSP的16根數(shù)據(jù)線上讀出來(lái)的數(shù)據(jù),通過(guò)原語(yǔ)存入這兩個(gè)

2014-03-26 10:14:48

ADSP-21xx處理器包括片內(nèi)振蕩器電路,因此也可以使用外部晶體。晶體應(yīng)通過(guò)CLKIN和XTAL引腳連接,兩個(gè)電容器如圖2所示連接。應(yīng)使用并聯(lián)諧振、基頻、微處理器級(jí)晶體。 時(shí)鐘輸出信號(hào)(CLKOUT

2020-07-17 14:23:24

顯示了運(yùn)行在200MHz的處理器的性能基準(zhǔn)。表2顯示了各個(gè)產(chǎn)品的特性。如第1頁(yè)圖1中的功能框圖所示,a DSP-2126x使用兩個(gè)計(jì)算單元,在一系列DSP算法上比以前的SHARC處理器性能提高5到10

2020-10-14 16:59:05

SRU)。如第1頁(yè)圖1所示,處理器使用兩個(gè)計(jì)算單元,在一系列DSP算法上比以前的SHARC處理器提供顯著的性能提升。使用SIMD計(jì)算硬件,處理器可以在450mhz下運(yùn)行2.7gflops,在

2020-10-12 17:17:43

性能要求同時(shí)保持足夠的靈活性以滿足多種應(yīng)用的需求)的特定需求。配備了多達(dá)兩個(gè)ARM?Cortex?-A15內(nèi)核、兩個(gè)C66x DSP內(nèi)核、若干視頻/圖形加速器、一個(gè)四核可編程實(shí)時(shí)單元(PRU)以及兩個(gè)ARM

2018-09-04 09:54:55

ARM946E-S? 是一個(gè)可合成的宏小區(qū),結(jié)合了ARM9E-S? 帶指令和數(shù)據(jù)高速緩存的處理器核心、帶保護(hù)單元的緊密耦合指令和數(shù)據(jù)SRAM存儲(chǔ)器、寫緩沖區(qū)和AMBA? (高級(jí)微處理器總線體系結(jié)構(gòu)

2023-08-02 17:50:31

ARM946E-S? 是一個(gè)可合成的宏小區(qū),結(jié)合了ARM9E-S? 加工機(jī)具有指令和數(shù)據(jù)緩存、緊密耦合的指令和數(shù)據(jù)SRAM的核心帶有保護(hù)單元、寫緩沖區(qū)和AMBA的存儲(chǔ)器? (高級(jí)微處理器總線體系結(jié)構(gòu)

2023-08-08 07:33:30

ARM966E-S是一個(gè)可合成的宏單元,將ARM處理器與緊密耦合的SRAM存儲(chǔ)器相結(jié)合。它是ARM9 Thumb系列高性能32位片上系統(tǒng)(SoC)處理器解決方案的一員,面向廣泛的嵌入式應(yīng)用,在這

2023-08-02 07:46:42

姚鋼,EDN China資深記者Blackfin和SHARC處理器是ADI兩大DSP產(chǎn)品線,目前一些在工控、測(cè)試測(cè)量的客戶正轉(zhuǎn)向超越MCU的DSP解決方案。例如,以太網(wǎng)(IEEE1588和802.3

2019-07-23 06:27:17

/Processor,數(shù)字信號(hào)處理),另外兩個(gè)是MCU(Micro Control Unit,微控制器單元)和MPU(Micro Processor Unit,微處理器單元)。MCU集成了片上外圍器件;MP...

2021-11-03 06:03:15

/Processor,數(shù)字信號(hào)處理),另外兩個(gè)是MCU(Micro Control Unit,微控制器單元)和MPU(Micro Processor Unit,微處理器單元)。MCU集成了片上外圍器件;MPU不帶外圍

2021-11-03 07:00:26

FPGA系統(tǒng)設(shè)計(jì)中,如果用兩個(gè)FPGA工作,應(yīng)該如何設(shè)計(jì)兩片之間的通信?從片的配置和時(shí)鐘輸入與主片有何不同?一個(gè)做主片用于數(shù)據(jù)處理和控制,一個(gè)做從片用于IO擴(kuò)展。硬件和軟件上應(yīng)該如何設(shè)計(jì)兩片之間

2023-05-08 17:18:25

SPI Flash中代碼搬到 SRAM中運(yùn)行,應(yīng)該如何操作?需要自行編程?

4. 看到有兩個(gè)文件 SRAM.mac 和 SPIROM.mac ,其功能是什么?

2023-06-16 08:18:54

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2019-09-24 07:09:13

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2020-03-05 07:01:34

種布局下,DSP得以實(shí)現(xiàn)單周期的MAC指令。 還有一個(gè)問(wèn)題,即現(xiàn)在典型的高性能GPP實(shí)際上已包含兩個(gè)片內(nèi)高速緩存,一個(gè)是數(shù)據(jù),一個(gè)是指令,它們直接連接到處理器核,以加快運(yùn)行時(shí)的訪問(wèn)速度。從物理

2014-04-17 10:45:08

分枝,一個(gè)是DSP(Digital Signal Processing/Processor,數(shù)字信號(hào)處理),另外兩個(gè)是MCU(Micro Control Unit,微控制器單元)和MPU(Micro

2017-06-29 11:37:24

用于SHARC處理器的ADZS-21489-EZLITE,ADSP-2148x EZ-KIT Lite評(píng)估系統(tǒng)。 SHARC處理器基于32位超級(jí)哈佛架構(gòu),包括一個(gè)獨(dú)特的內(nèi)存架構(gòu),由兩個(gè)大型片上雙端口

2020-03-16 10:19:26

SPC58EC 有一個(gè)中斷控制器,支持兩個(gè)處理器。您可以為每個(gè)核心提供不同的向量表。假設(shè)兩個(gè)內(nèi)核處于活動(dòng)狀態(tài)并且發(fā)生了一個(gè)外部中斷(ADC,定時(shí)器),這之后的過(guò)程是什么?哪個(gè)內(nèi)核將運(yùn)行中斷處理程序?

2022-12-12 08:10:22

2106x只具有SISD(單指令流單數(shù)據(jù)流)功能。為了充分利用這種新的功能,一些指令做了一些改變。ADSP21160包括1個(gè)100/150MHz的運(yùn)算核、雙端片內(nèi)SRAM、1個(gè)支持多處理器的集成在片內(nèi)

2019-04-03 09:40:03

應(yīng)用處理器與MCU“跨界”處理器—從性能差距到新解決方案領(lǐng)域降低成本—去除片內(nèi)閃存集高性能、低延遲、高能效和安全性于一體相關(guān)行業(yè)和應(yīng)用 i.MX RT跨界處理器

2021-02-19 06:06:39

通信的場(chǎng)合。特別適合于進(jìn)行數(shù)字信號(hào)處理運(yùn)算的微處理器,其主要應(yīng)用是實(shí)時(shí)快速地實(shí)現(xiàn)各種數(shù)字信號(hào)處理算法。根據(jù)數(shù)字信號(hào)處理的要求,DSP芯片一般具有如下主要特點(diǎn):(1)在一個(gè)指令周期內(nèi)可完成一次乘法和一次

2017-11-17 14:10:37

ADSP2106x SHARC是一個(gè)適用于語(yǔ)音、通信和圖像處理的高速32位數(shù)字信號(hào)處理器。該芯片是基于ADSP21000系列DSP芯片發(fā)展起來(lái)的一個(gè)完整的單片系統(tǒng),增加了一個(gè)雙口片內(nèi)SRAM,并集成

2019-07-19 08:16:35

為什么要片內(nèi)RAM大的DSP效率高?

2019-09-03 05:55:24

嗨,我有新的要求,我必須開發(fā)一臺(tái)有10個(gè)電極和12個(gè)引線的心電圖機(jī),它將通過(guò)USB向PC機(jī)發(fā)送數(shù)據(jù),PC機(jī)應(yīng)用程序?qū)@示心電信號(hào)。我對(duì)ECG系統(tǒng)設(shè)計(jì)是全新的,為什么需要DSP處理器?我需要開發(fā)哪個(gè)過(guò)濾器?問(wèn)候,Akshay

2020-03-13 07:13:48

舉例說(shuō)明FPGA作為協(xié)處理器在實(shí)時(shí)系統(tǒng)中有哪些應(yīng)用?FPGA用于協(xié)處理器有什么結(jié)構(gòu)特點(diǎn)和設(shè)計(jì)原則?

2021-04-08 06:48:20

1.微處理器的兩個(gè)發(fā)展趨勢(shì)?2.常用可編程處理器有哪三種?3.單片機(jī)的結(jié)構(gòu)特點(diǎn)和應(yīng)用特點(diǎn)是什么?4.什么叫混合信號(hào)處理器?5.什么是“單片”解決方案?6. MSP430的工作電壓多高?是多少位

2021-07-21 08:19:24

處理器,有TI的C66x系列、ADI的Blackfin系列。二、DSP處理器有什么特點(diǎn)?你可以把DSP處理器想象成一個(gè)科學(xué)計(jì)算器。它非常擅長(zhǎng)做運(yùn)算。1、并行性。某些型號(hào)的DSP處理器內(nèi)部有兩個(gè)獨(dú)立的乘法器

2020-09-04 10:31:13

SRAM是當(dāng)今處理器上最普遍的內(nèi)存。當(dāng)芯片制造商宣布他們已經(jīng)成功地將更多的電路封裝到芯片上時(shí),通常是較小的晶體管引起了人們的注意。但是連接晶體管形成電路的互連也必須收縮。IMEC的研究人員提出了一個(gè)

2020-05-11 15:40:48

本文提出了一個(gè)通用微處理器(ARM)與DSP的接口設(shè)計(jì)方案,以實(shí)現(xiàn)兩者的實(shí)時(shí)通信。

2021-06-08 06:36:41

端口SRAM(Dual-Port SRAM, DP-SRAM)憑借其兩個(gè)端口可以同時(shí)進(jìn)行讀寫的能力在SRAM 領(lǐng)域占有重要的一席之地,尤其在多核、實(shí)時(shí)信號(hào)處理系統(tǒng)中有著廣泛的應(yīng)用。 由于功耗的限制,片

2020-07-06 16:26:25

哪位大神關(guān)于《數(shù)字信號(hào)處理與數(shù)字信號(hào)處理器》的DSP論文,求分享。。。。

2014-05-27 16:25:52

視覺(jué)處理器(PVP),支持HD。像素合成器。全集成式DMA控制器,支持與所有片內(nèi)和片外存儲(chǔ)器和外設(shè)進(jìn)行DMA傳輸。3個(gè)增強(qiáng)型并行外設(shè)接口(ePPI),支持最高24位的數(shù)據(jù)寬度、ITU-R BT.656

2018-08-30 11:41:29

兩個(gè)方面的內(nèi)容:IP核生成和IP核復(fù)用。文中采用IP核復(fù)用方法和SOC技術(shù)基于AVR 8位微處理器AT90S1200IP Core設(shè)計(jì)專用PLC微處理器FSPLCSOC模塊。

2019-07-26 06:19:34

DSP并行系統(tǒng)。因?yàn)樵撓盗械?b class="flag-6" style="color: red">處理器在構(gòu)成并行處理系統(tǒng)時(shí)其本身就提供了實(shí)現(xiàn)互連所需的片內(nèi)總線仲裁控制和特有的鏈路口,可以以各種拓?fù)浣Y(jié)構(gòu)互連DSP,滿足大運(yùn)算量和片間通信靈活的要求。此外,選用ADSP

2019-05-21 05:00:19

,主機(jī)通過(guò)它可以直接訪問(wèn)DSP片內(nèi)的一段RAM。在早期的DSP中,這段公用的RAM是一段2K字的雙口RAM(對(duì)于TMSVC5402則可以訪問(wèn)所有的片內(nèi)RAM)。當(dāng)主機(jī)和DSP同時(shí)訪問(wèn)同一地址時(shí),主機(jī)優(yōu)先

2019-06-06 05:00:39

ADZS-21369-EZLITE,ADSP-21369用于SHARC處理器的EZ-KIT Lite評(píng)估系統(tǒng)。 SHARC處理器基于32位超級(jí)哈佛架構(gòu),包括一個(gè)獨(dú)特的內(nèi)存架構(gòu),由兩個(gè)大型片上雙端口

2020-03-16 10:19:26

內(nèi)的高速互聯(lián)總線和各個(gè)處理器交互數(shù)據(jù)。 和網(wǎng)絡(luò)相關(guān)的片內(nèi)設(shè)備如圖1右下角灰色模塊所示,主要包括兩個(gè)對(duì)外的SGMII接口、以太交換和網(wǎng)絡(luò)交換模塊,以及用于數(shù)據(jù)管理的安全加速器和包加速器,是為了快速檢測(cè)

2016-11-28 23:47:01

內(nèi)的高速互聯(lián)總線和各個(gè)處理器交互數(shù)據(jù)。 和網(wǎng)絡(luò)相關(guān)的片內(nèi)設(shè)備如圖1右下角灰色模塊所示,主要包括兩個(gè)對(duì)外的SGMII接口、以太交換和網(wǎng)絡(luò)交換模塊,以及用于數(shù)據(jù)管理的安全加速器和包加速器,是為了快速檢測(cè)

2016-10-15 22:43:53

,它連接到兩個(gè)SRAM。考慮到PCB布局的困難(因?yàn)槲覀兪褂玫氖?12k x 36個(gè)SRAM - 每個(gè)SRAM有36條數(shù)據(jù)線和19條地址線),建議兩個(gè)SRAM具有相同的時(shí)鐘頻率,但有兩個(gè)IO。請(qǐng)幫助我們繼續(xù)最近的方法。我需要輸入這些用于FPGA實(shí)現(xiàn)以及PCB上的布線。

2020-08-27 07:38:50

上的片內(nèi)FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來(lái)分擔(dān)FIR和IIR處理任務(wù),讓內(nèi)核去執(zhí)行其他處理任務(wù)。在本文中,我們將借助不同的使用模型以及實(shí)時(shí)測(cè)試示例來(lái)探討如何在實(shí)踐中利用這些加速器。

2020-12-28 06:26:54

我現(xiàn)在的板子上有兩片C6678dsp,請(qǐng)問(wèn),如何在一個(gè)打開的CCS5界面下面創(chuàng)建用于這兩個(gè)c6678DSP的工程,然后如何進(jìn)行l(wèi)oad和調(diào)試?還是說(shuō)要打開兩個(gè)CCS5界面?

另外,如果每個(gè)DSP我需要用兩個(gè)核(0核和1核),那該怎么創(chuàng)建工程呢?是不是要?jiǎng)?chuàng)建4個(gè)工程,寫4個(gè)main函數(shù)?

2018-06-21 05:21:59

如何去選擇數(shù)字信號(hào)處理器 (DSP)?

2021-05-25 07:20:05

你好,我打算建立通信以在兩個(gè)處理器之間讀寫。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9處理器,另一方面是FPGA(ZC7020)。我在FPGA端沒(méi)有任何PCIe硬端口。因此

2020-04-16 09:04:30

處理器DSP4、嵌入式片上系統(tǒng)SOC(System-on-a-Chip)三、多核處理器四、嵌入式操作系統(tǒng)EOS五、嵌入式實(shí)時(shí)操作系統(tǒng)RTOS六、嵌入式系統(tǒng)設(shè)計(jì)七、嵌入式系統(tǒng)的軟件一、嵌入式微處理器體系結(jié)構(gòu)1、馮諾依曼體系結(jié)構(gòu)(1)程序和控制共用一個(gè)存儲(chǔ)

2021-11-08 06:57:02

音頻和視頻通信的場(chǎng)合。特別適合于進(jìn)行數(shù)字信號(hào)處理運(yùn)算的微處理器,其主要應(yīng)用是實(shí)時(shí)快速地實(shí)現(xiàn)各種數(shù)字信號(hào)處理算法。根據(jù)數(shù)字信號(hào)處理的要求,DSP芯片一般具有如下主要特點(diǎn):(1)在一個(gè)指令周期內(nèi)可完成一次

2017-04-26 09:37:34

概述:MM58167B是美國(guó)國(guó)家半導(dǎo)體公司生產(chǎn)的一款微處理器實(shí)時(shí)時(shí)鐘芯片。作為總線型微處理系統(tǒng)中的實(shí)時(shí)時(shí)鐘源,其內(nèi)部包括一個(gè)可尋址的實(shí)時(shí)計(jì)數(shù)器、56bit片內(nèi)RAM和兩個(gè)輸出中斷,而且POWER DOWN引腳的有效信...

2021-04-20 06:53:56

微控制器:CPU + 片內(nèi)內(nèi)存 + 片內(nèi)外設(shè)微處理器:CPU處理器通常指微處理器、微控制器和數(shù)字信號(hào)處理器這三種類型的芯片。微處理器(MPU)通常代表一個(gè)功能強(qiáng)大的CPU,但不是為任何已有的特定

2022-02-09 07:48:39

的運(yùn)算,根據(jù)標(biāo)志位跳轉(zhuǎn)等。很少有微處理器具備這些強(qiáng)大的位操作能力,因?yàn)樵O(shè)計(jì)者在設(shè)計(jì)微處理器時(shí),僅考慮以字節(jié)或更大的單位來(lái)操作數(shù)據(jù)。講清楚了微處理器和微控制器的區(qū)別,還要補(bǔ)充一個(gè)概念,說(shuō)說(shuō)常用的DSP

2017-04-22 22:04:50

如題,本人在參與的一個(gè)項(xiàng)目,用到DSP TMS320C6472 六核處理器。準(zhǔn)備使用其中兩個(gè)核來(lái)相關(guān)處理。每個(gè)核的代碼我已經(jīng)寫好,但是本人是DSP新手,現(xiàn)在不知道怎么鏈接.out文件使其從Flash

2013-12-16 09:12:49

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2021-04-26 07:01:55

本帖最后由 luna 于 2011-3-3 13:12 編輯

不斷發(fā)展的DSP技術(shù)迅速地拓寬擴(kuò)展到了各應(yīng)用領(lǐng)域,但傳統(tǒng)的DSP處理器由于以順序方式工作而數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標(biāo)

2011-03-03 10:05:43

用于SHARC處理器的ADZS-21479-EZLITE,ADSP-2147x EZ-KIT Lite評(píng)估系統(tǒng)。 SHARC處理器基于32位超級(jí)哈佛架構(gòu),包括一個(gè)獨(dú)特的內(nèi)存架構(gòu),由兩個(gè)大型片上雙端口

2020-03-13 09:35:38

ADZS-21262-EZLITE,ADSP-21262 EZ-KIT Lite評(píng)估系統(tǒng),用于SHARC處理器。 SHARC處理器基于32位超級(jí)哈佛架構(gòu),包括一個(gè)獨(dú)特的存儲(chǔ)器架構(gòu),由兩個(gè)大型片上雙

2020-03-13 09:30:16

問(wèn)個(gè)問(wèn)題,能不能利用低成本前兩三代的arm處理器來(lái)搭架一個(gè)萬(wàn)元內(nèi)的超算?

2022-09-13 14:59:36

ADI 你好: 我想咨詢下ADI的DSP處理器,因?yàn)橐恢睕](méi)有使用過(guò)ADI的DSP的系列處理器,對(duì)此不熟悉。 我的應(yīng)用是DSP讀取ADC的信號(hào)(前端模擬電路都由ADI的模擬器件搭建并測(cè)試完成,目前

2018-11-02 09:18:18

等。很少有微處理器具備這些強(qiáng)大的位操作能力,因?yàn)樵O(shè)計(jì)者在設(shè)計(jì)微處理器時(shí),僅考慮以字節(jié)或更大的單位來(lái)操作數(shù)據(jù)。 DSP芯片分類以及特點(diǎn) 數(shù)字信號(hào)處理器里的CPU是專門設(shè)計(jì)用來(lái)極快地進(jìn)行離散時(shí)間信號(hào)

2017-10-27 15:51:04

做了一款基于arm處理器的SOC芯片,流片回來(lái)后測(cè)試發(fā)現(xiàn),ARM能正常和片內(nèi)SRAM和ROM通信,卻不能和片外SRAM進(jìn)行通信,請(qǐng)教高手,ARM不能和片外SRAM通信的可能的原因?

2022-06-10 15:50:38

請(qǐng)問(wèn)SRAM 存儲(chǔ)數(shù)據(jù)具體是怎么存儲(chǔ)的? 還有就是在處理器和SRAM之間用VERILOG實(shí)現(xiàn)一個(gè)總線仲裁器怎么實(shí)現(xiàn)?謝謝高手指教!

2008-08-28 20:31:21

AVR對(duì)片內(nèi)SRAM的訪問(wèn)需要多久?

2023-10-24 07:49:15

28027片內(nèi)有兩個(gè)比較器,想利用起來(lái)。從母線電流采集過(guò)來(lái)的信號(hào)輸入片內(nèi)比較器的一個(gè)腳,跟給定電壓信號(hào)比較,超過(guò)后就翻轉(zhuǎn)觸發(fā)保護(hù)。可以這樣做嗎?

2020-07-22 14:58:01

我是QorIQ處理器的SRAM存儲(chǔ)器接口(cy62167g18-55zxi)。我無(wú)法知道如何接口的#(Byte Low使)和他#(高字節(jié)使能)信號(hào)目前SRAM處理器。CY62167G18-5ZXI

2018-08-14 05:38:52

最近接觸到了DSP處理器,關(guān)于定點(diǎn)處理器處理浮點(diǎn)運(yùn)算有兩個(gè)疑問(wèn),我是用C語(yǔ)言開發(fā)的,16位處理器,兩個(gè)浮點(diǎn)數(shù)進(jìn)行加減乘除,定點(diǎn)處理器運(yùn)算出來(lái)結(jié)果的精度有多高,能保留幾位有效數(shù)字??另外,關(guān)于定點(diǎn)

2019-05-13 01:09:48

來(lái)實(shí)施軟件加密。相比傳統(tǒng) MCU,這是一個(gè)明顯的優(yōu)勢(shì)。6、大存儲(chǔ)容量在理想環(huán)境中,當(dāng)可執(zhí)行代碼和數(shù)據(jù)被存儲(chǔ)在片內(nèi) SRAM 中,并從此存儲(chǔ)中執(zhí)行 CPU內(nèi)核操作時(shí),嵌入式處理器的性能達(dá)到最高。即便在片內(nèi)

2018-10-30 11:17:45

信號(hào)處理器(DSP),信號(hào)處理器(DSP)是什么意思

DSP是(digital signal processor)的簡(jiǎn)稱,是一種專門用來(lái)實(shí)現(xiàn)信號(hào)處理算法的微處理器芯片

2010-03-26 14:53:54 15467

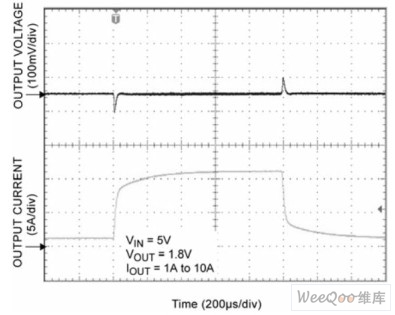

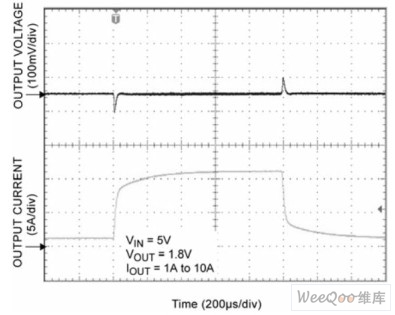

15467 為復(fù)雜的DSP處理器設(shè)計(jì)良好的電源是非常重要的。良好的電源應(yīng)有能力應(yīng)付動(dòng)態(tài)負(fù)載切換并可以控制在高速處理器設(shè)計(jì)中存在的噪聲和串?dāng)_。DSP處理器中的不斷變化的瞬態(tài)是

2010-07-02 11:56:12 1714

1714

如何選擇 DSP 處理器

2017-10-23 14:30:46 8

8

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論