引言

STM32U575/585 微控制器(MCU)基于具有 Arm TrustZone和 FPU 的高性能 Arm 32 位 Cortex?M33CPU。這些 MCU 采用新型結構制造,得益于其高度靈活性和高級外設集,實現了一流的超低功耗性能STM32U575/585 器件可為應用實現極高的能效。

帶有“Q”后綴的 STM32U575/585 器件(例如 STM32U5xxxxQ)支持在運行和低功耗模式下使用內部 SMPS,從而能夠設計出非常高效的低功耗應用

通過集成 ART 加速器 8 KB 指令緩存,STM32U575/585 MCU 可在高達 160MHz 的頻率下運行,實現 240 DMIPS 性能,同時保持極低的動態功耗。

STM32U575/585 器件嵌入了大量智能高性能外設,具有多種先進的超低功耗模擬功能。借助于 LPBAM(低功耗后臺自主模式),許多外設(包括通信、模擬、定時器和音頻)均可正常工作并自主進入停機模式,并直接訪問內存。超低功耗設計和處理性能的組合使這些器件能夠達到行業領先的 EEMBC ULPBench得分,最高達到 535 ULPMark。

STM32U575/585 MCU 集合了多種創新,能夠使不同模式下的功耗減到最小,同時保留大部分現有外設并很好地實現了引腳兼容,能夠很容易地從現有產品上進行移植。

得益于其內置內部穩壓器和電壓調節,無論外部供電電壓是多少,在活動模式下都能保持盡可能小的消耗。這使得這些器件非常適合電池供電的產品,所需供電電壓可低 至 1.71 V。

此外,它們具有多電壓域,允許產品以低壓供電,同時模數和數模轉換器可在高達 3.6V 的高電源電壓和參考電壓下工作。

STM32U575/585 器件可支持電池備份域以保持 RTC(實時時鐘)運行,并能支持 32 個寄存器(每個寄存器為 32 位寬)的組,該寄存器組在失去電源時能夠保持內容。該可選備份電池可在有主電源時充電。

這些器件支持多種主要的低功耗模式,其中每種都有多個子模式選項。這使得設計人員可以在低功耗性能、短啟動時間、可用外設集與喚醒源最大數量之間實現最佳折中。

1、概述

本應用說明適用于基于 Arm Cortex內核的 STM32U575/585 微控制器。

參考文檔

[1] 參考手冊:基于 Arm的 STM32U575xx 和 STM32U585xx 高級 32 位 MCU(RM0456)

[2] STM32U575xx(DS13737)和 STM32U585xx(DS13086)的數據表

[3] 應用筆記用于硬件設置和低功耗的 STM32 微控制器 GPIO 配置(AN4899)

[4] 應用筆記使用 LPBAM 進行的 STM32U575/585 功耗優化(AN5645)

[5] EEMBC 組織網址 http://www.eembc.org

2、高效能處理

由于使用了關聯到其存儲器接口的 Cortex?M33 核,因而在運行模式下獲得了很高的處理性能(以 DMIPS/MHz 表示)。為確保實現最大工作頻率下的高性能工作,STM32U575/585 器件嵌入了 ART 加速器指令緩存(ICACHE),通過其屏蔽 Flash 訪問等待狀態。無論系統時鐘頻率是多少,都可達到 1.5 DMIPS/MHz 的處理性能。

STM32U575/585 器件支持動態電壓調節,以便優化其在運行模式下的功耗。可根據系統的最高操作頻率,調節為邏輯(VCORE)供電的主穩壓器提供的電壓。更多詳細信息,請參見參考文檔[1]。

主調壓器在以下范圍內運行:

? Range 1(V 內核 = 1.2 V),其中 CPU 和外設運行頻率高達 160 MHz

? Range 2(V 內核 = 1.1 V),其中 CPU 和外設運行頻率高達 110 MHz

? Range 3(V 內核 = 1.0 V),其中 CPU 和外設運行頻率高達 55 MHz

? Range 4(V 內核 = 0.9 V),其中 CPU 和外設運行頻率高達 25 MHz

除非另有說明,否則本應用筆記中使用的所有功耗數據均基于從參考文檔[2]中提取的 TA = 25 ° C 且 VDD = 3.0 V

時的典型規格。

提示

使用低功耗調壓器時,根據軟件配置,系統時鐘可以是頻率高達 24MHz(默認為 4MHz)的 MSIS,也可以是HSI16。

2.1 內部調壓器效率

STM32U575/585 器件嵌入了兩個內部調壓器,可在應用運行時根據應用要求進行選擇:

? SMPS 降壓轉換器

? 線性調壓器(LDO)

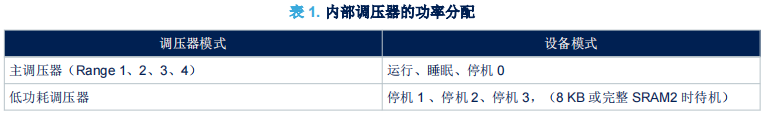

LDO 和 SMPS 穩壓器有兩種模式:

? 主調壓器(需要性能時使用)

? 低功耗調壓器

兩個調壓器都可以提供四個不同電壓(電壓調節),同時還能在停機模式下工作。

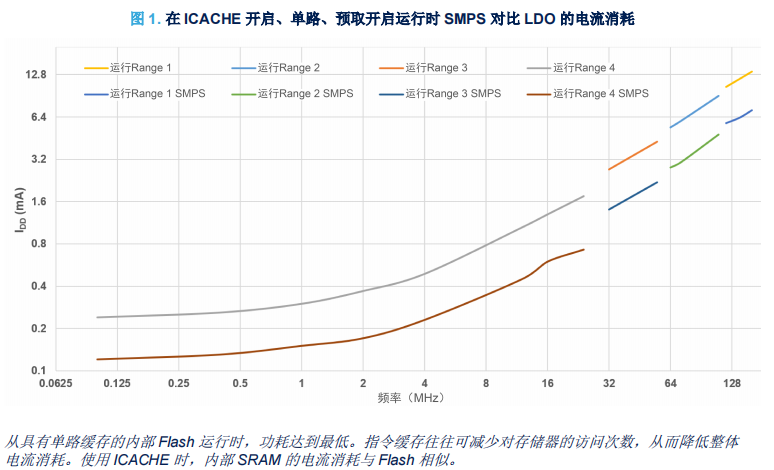

下圖顯示了 STM32U575/585 微控制器在運行模式下用于 SMPS 和 LDO 配置的典型電流消耗(作為系統頻率的函數)。

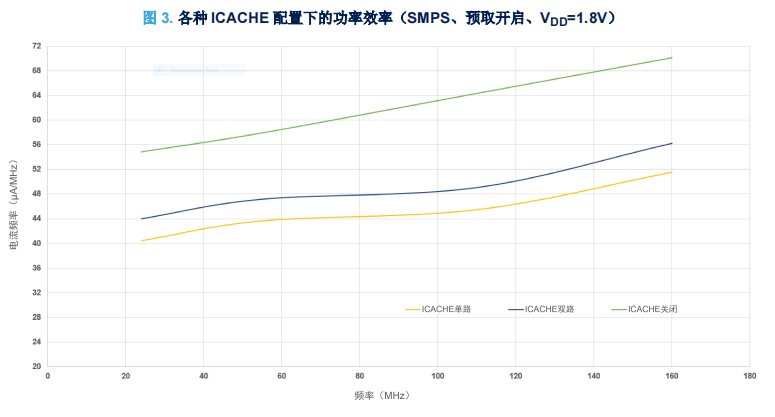

下圖顯示了該曲線在 CPU 頻率下轉化為功率效率(將其除以電流消耗、乘以電源電壓得到功率圖)。

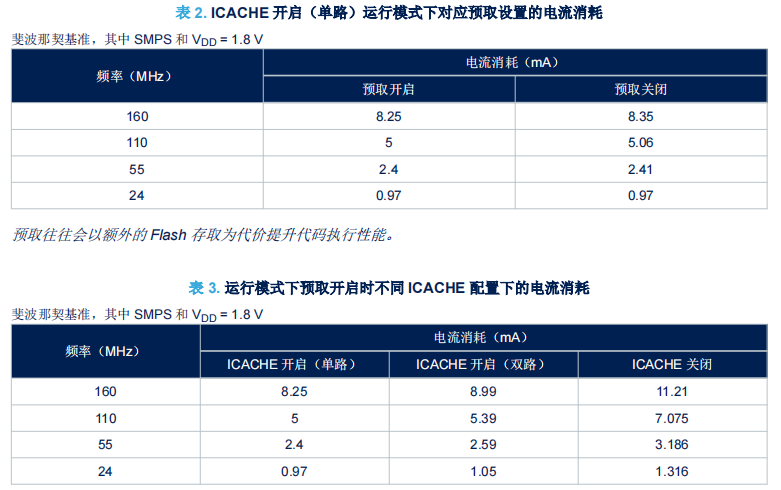

2.2 ICACHE效率

指令緩存(ICACHE)旨在緩存來自處理器的指令提取或指令存儲器負載。ICACHE 只管理讀事務,不管理寫事務。在大部分時間,ICACHE 通過從內部 ICACHE 提取指令來降低功耗,而不是從更大且功耗更大的主存儲器中獲取指令。

ICACHE 的默認配置(復位時)是雙路組相聯緩存。對于需要極低功耗配置文件的應用,ICACHE 可以配置為單路,即直接映射緩存。

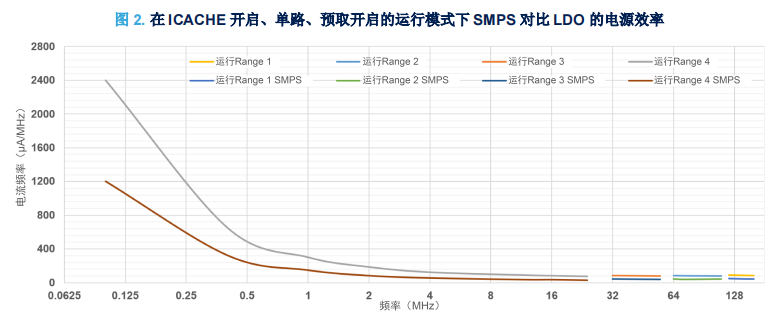

下圖顯示了 STM32U575/585 微控制器在運行模式下在不同 ICACHE 配置的斐波那契基準中的功率效率(作為系統頻率的函數),其中采用 SMPS 且 VDD = 1.8 V。

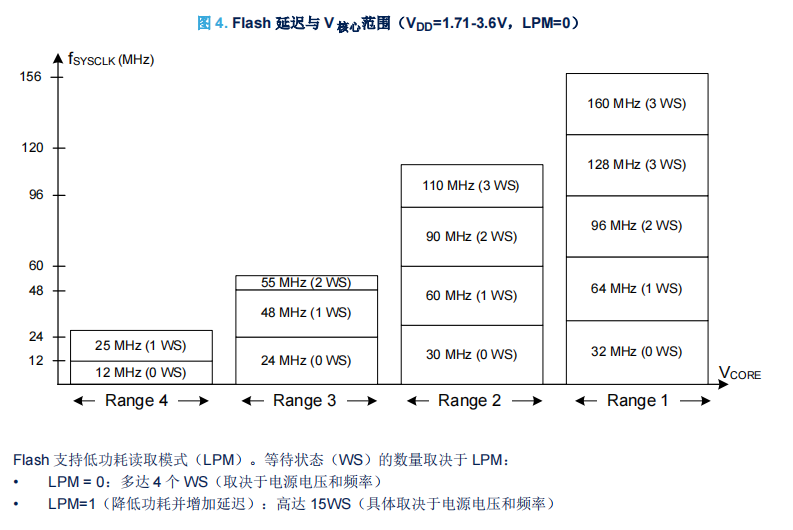

2.3 Flash效率

下圖顯示了 Flash 延遲(要被編程到 Flash 訪問控制寄存器中的等待狀態數值),具體取決于 STM32U575/585 穩壓器電壓調節范圍和系統時鐘頻率。

本應用說明適用于基于 Arm Cortex內核的 STM32U575/585 微控制器。

3、STM32U575/585 超低功耗特點

3.1 低功耗模式

STM32U575/585 微控制器實現了多種不同的功耗模式。默認情況下,系統復位或上電復位后,MCU 進入運行模式。系統提供了多個低功耗模式,可在 CPU 不需要運行時(例如等待外部事件時)節省功耗。由用戶選擇具體的模式,以在低功耗、短啟動時間和可用喚醒源之間尋求最佳平衡。如需更詳細信息,請參考[1]。

3.1.1 睡眠模式

CPU 時鐘關閉,包括 Cortex-M33 內核(例如 NVIC、SysTick 等)在內的所有外設都可以運行,并在發生中斷或事件時喚醒 CPU。

3.1.2 停機模式

停機模式基于 Cortex-M33 深度睡眠模式與外設時鐘門控的組合。核心域中的所有時鐘均停止。禁用 PLL、MSIS、MSIK、HSI16 和 HSE 振蕩器,如果外設請求,則可以在停機 0、停機 1、或停機 2 模式下啟用 MSIS、MSIK、HSI16。

停機 0 和停機 1 提供最大數量的活動外設和喚醒源,相比停機 2,其喚醒時間更短,但功耗較高。在停機 2 和停機3 模式下,核心域的大部分處于低漏電模式。

在從停機模式退出時,系統時鐘可以是 MSIS(最高 24 MHz)或 HSI16,具體取決于軟件配置。

低功耗后臺自主模式(LPBAM)

一些外設是自主的,可以在需要時通過請求其內核時鐘(最高 24MHz 的 MSIK,或 HSI16)及其總線(APB 或AHB)而在停機 0、停機 1、或停機 2 模式下運行,以便與 DMA(GPDMA1 或 LPDMA1,取決于外設和功耗模式)傳輸數據。

3.1.3 待機模式

待機模式實現在保留欠壓復位功能時的最低功耗:關閉內部調壓器,從而關閉核心域。PLL、MSI(MSIS 和MSIK)RC、HSI16 RC 和 HSE 晶振也會關閉。RTC 可保持激活狀態。可選擇保留 8、56 或 64 KB 的 SRAM2。可以施加內部上拉或下拉來保持 I/O 電平。喚醒后的系統時鐘為 MSIS,最高 4MHz。

3.1.4 關斷模式

關斷模式下功耗達到最低。該模式基于深度睡眠模式,其中調壓器被禁用。因此核心域斷電。通過關閉內部穩壓器,以及禁用耗電監控,該模式可實現最低電流消耗。借助某一個(共五個)喚醒引腳或復位引腳,能夠從該模式喚醒。由低速外部振蕩器(LSE)定時的 RTC 在此模式下也是起作用的,具有喚醒功能。

文檔[1]的“功耗模式”部分中的“低功耗模式總結”表總結了每種模式的可用特性,并提供了電流消耗的指示。

3.2 功耗優化

3.2.1 ICACHE 處于運行模式

ICACHE 通過從內部 ICACHE 獲取指令來降低功耗。在大多數情況下,采用較低性能配置文件和嚴格的低功耗限制的應用程序可能會從配置為直接映射(ICACHE_1-way)的 ICACHE 的較低功耗而受益。

這種單路高速緩存配置是通過在 ICACHE_CR 中編程 WAYSEL=0 實現的。

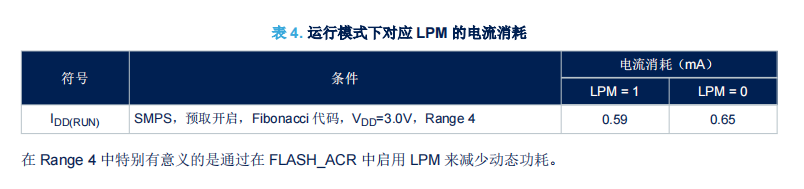

3.2.2運行和睡眠模式下的 Flash

STM32U575/585 Flash 包括主存儲器塊,該主存儲器塊由兩個 1 MB 的存儲區(bank)組成,每個 bank 包含 128個 8 KB 的頁面。當 MCU 處于運行和睡眠模式時,這一結構在專用模式下的功耗方面得到了優化。為了降低運行和睡眠模式下的功耗,可以根據所使用的存儲區,通過設置 FLASH_ACR 中的 PDREQ1 或 PDREQ2獨立地將每個存儲區置于掉電模式。

Flash 支持低功耗讀取模式,通過在 FLASH_ACR 中編程 LPM=1 來降低功耗。

預取往往會以額外的 Flash 存取為代價提升代碼執行性能。然而,對于大多數應用程序,預取開啟時的電源效率會更好。

3.2.3 電源控制優化

在待機模式下,可以將 BOR 配置為不連續模式(超低功耗模式),通過將 PWR_CR 中的 ULPMEN 位設置為 1 來進一步降低電流消耗。

為降低運行、睡眠或任何低功耗模式下的功耗,建議從 LDO 切換到 SMPS。

? SMPS 電源引腳僅在具有 SMPS 降壓轉換器選項的特定封裝上可用。

? 可以動態完成 SMPS 到 LDO 和 LDO 到 SMPS 的切換。

3.2.4 低功耗模式下的 RCC

為了維持輸出時鐘精度,MSI 偏置默認為連續模式。當調壓器處于 Range 4 中并且設備處于停機 1 或停機 2 模式時,在進入低功耗模式之前在 RCC_ICSCR1 中設置 MSIBIAS 可降低 MSI 功耗。

在進入低功耗模式之前,建議選擇 HSI16 或 MSIS(16 或 24MHz)作為喚醒源,以縮短喚醒時間,并減少喚醒期間損失的能量。若使用 24 MHz,則須為 SRAM 讀訪問配置一個等待 狀態延遲,這會影響代碼執行性能。然后須在1 個 SRAM 等待狀態下使用 24 MHz 和使用 16 MHz 作為系統時鐘之間對該性能進行評估。

停機模式期間或從停機模式喚醒時的 MSIS 頻率與進入停機模式之前頻率相同。如果使用 MSIS 在運行模式下饋送 PLL,則由于 PLL 輸入時鐘頻率限制使 MSIS 在 4MHz 到 16 MHz 之間。此時建議關閉 PLL 并在進入停機模式之前將 MSIS 配置為高頻(如果使用 MSIS 作為喚醒時鐘)。

必須通過清零外設自身的使能位來禁用無法在停機 2 模式下使能的所有外設,或者通過配置 RCC 寄存器 使其處于復位狀態。

對于每個時鐘源來說,在未使用時都可單獨開啟或者關閉,以降低功耗。

3.2.5 低功耗模式下的 I/O 狀態

如需更詳細信息,請參考[3]。

配置未使用的 GPIO

GPIO 始終有一個輸入通道,可以是數字或模擬通道。如果不需要讀取 GPIO 數據,則優先配置為模擬輸入。這節省了輸入施密特觸發器的消耗。

禁用 GPIO 寄存器時鐘

如果某個 GPIO 組長時間不需要使用,請使用 HAL_RCC_GPIOx_CLK_DISABLE()函數禁用其時鐘。

進入低功耗模式時配置 GPIO

在睡眠、停機 0、停機 1 或停機 2 模式下,所有 I/O 引腳保持與運行模式中相同的狀態。對于輸出,根據外部組件所需的電平驅動合適的電平。

在停機 3、待機或關斷模式下,I/O 默認處于浮動狀態。根據外部組件所需的電平施加上拉或下拉。應認識到,在退出關斷模式時不會施加該上拉/下拉,直到固件配置 GPIO 為止。

在一些應用中,為了進一步降低停機模式下的功耗,并為了獲得更高的電阻值精度,建議使用外部上拉而不是內部上拉。

3.2.6 內部 SRAM

STM32U575/585 器件嵌入了五個 SRAM,每個都具有特定的功能:SRAM1、SRAM2、SRAM3 為主 SRAM。SRAM4 在 SRAM 中用于停機 2 模式下的外設低功耗后臺自主模式(LPBAM)。

保留所有 SRAM 和寄存器內容,但 SRAM 可全部或部分關閉,以便進一步降低功耗。這些 SRAM 由多個可以關閉的塊組成:

? 運行模式

要降低運行模式下的功耗,應通過在 PWR_CR1 中編程 SRAMxPD 來關閉所有 SRAM。

? 停機模式

該模式可實現最低功耗,同時保持低功耗調壓器供電的 SRAM 和寄存器的內容。停機 3 是具有完全保留的最低功耗模式。為了進一步優化功耗,建議如下:

– 通過在 PWR_CR2 中編程 SRAMxPDSy = 1 來關閉未使用的 SRAM:

? SRAM1, SRAM3, SRAM4

? DCACHE1、DMA2D、FDCAN、FMAC、PKA(如可用)和 USB 的 SRAM

– 根據應用數據大小,通過清除 PWR_CR2 中的 SRAMPDS1 和/或 SRAMPDS2 位來保留 SRAM2 第 1頁和/或第 2 頁。

? 待機模式

進入待機模式后,除備份域和待機電路中的寄存器和備份 SRAM(2 KB)外,其余 SRAM 和寄存器的內容都將丟失。通過在 PWR_CR1 中設置由低功耗調壓器供電的 RRSB1 和/或 RRSB2,SRAM2 第 1 頁(8 KB)或第 2 頁(56 KB)或兩頁都可以在待機模式保持(在 RAM2 保持模式下待機)。

3.2.7 運行和停機模式下的外設時鐘門控

STM32U575/585 器件支持關閉 AHB/APB 時鐘的功能,以進一步降低功耗。

未使用任何 AHB/APB 外設并且其時鐘被禁用時,會出現以下情況:

? 當在 RCC_CFGR2 中設置 AHB1DIS = 1 時,AHB1 外設的所有時鐘都關閉( BKPSRAM、DCACHE1、FLASH、ICACHE 和 SRAM1 除外)。

? 當在 RCC_CFGR2 中設置 AHB2DIS = 1 時,來自 RCC_AHB2ENR1 的 AHB2 外設的所有時鐘都關閉(SRAM2 和 SRAM3 除外)。

? 當在 RCC_CFGR3 中設置 AHB3DIS = 1 時,AHB3 外設的所有時鐘都關閉(SRAM4 除外)。

? 當在 RCC_CFGR2 中設置 APB1DIS = APB2DIS = 1 且在 RCC_CFGR3 中設置 APB3DIS = 1 時,APB1/2/3外設的所有時鐘都關閉。

當啟用外設時,其時鐘可在器件處于休眠模式時通過清除 RCC_AHBxSMENR 和 RCC_APBxSMENR 中的外設SMEN 位而自動關閉。外設的 EN 位和 SMEN 位均須設置為 1,以便在休眠模式下保持時鐘開啟。

外設的 SMEN 位還用于根據外設請求在停機 0 和停機 1 模式下允許外設提供時鐘。當外設請求時鐘時,該時鐘將分配給所有啟用的外設。因此,如果在停機模式下未使用外設,則須在進入停機模式之前清除 SMEN 位。

Caution: 外設的 SMEN 位必須設置成允許產生能夠從停機模式喚醒器件的中斷。

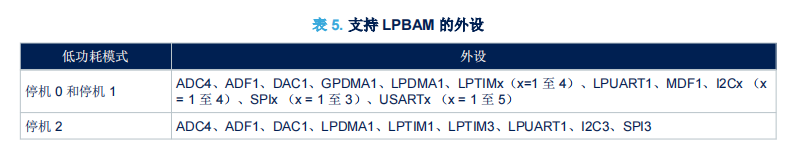

3.3 使用 LPBAM 優化外設功耗

STM32U575/585 器件支持低功耗后臺自主模式(LPBAM),使外設能夠在停機 0、停機 1 和停機 2 模式(無任何軟件運行)下工作并保持自主。

由于外設自身的獨立時鐘(稱為內核時鐘)請求性能,此功能在停機模式下可用。該內核時鐘在有外設請求時自動打開,并在無外設請求時自動關閉。如需更詳細信息,請參考[1]。

3.3.1 支持 LPBAM 的外設

下表列出了支持 LPBAM 的所有 STM32U575/585 外設。

3.3.2 主要用例

以下是可以留在停機模式下完成的用例示例(有關更多詳細信息,請參見文檔[4]):

? 由低功耗定時器(或任何其他觸發器)觸發的 ADC 或 DAC 轉換

? 音頻數字濾波器數據傳輸到 SRAM 中:檢測到聲音活動時從停機喚醒

? I2C/SPI 從設備傳輸、UART/LPUART 接收:在外設傳輸結束時或在 DMA 緩沖區事件時喚醒

? 由 LPTIM 觸發器觸發的(例如傳感器周期性讀取)I2C/SPI 主設備傳輸,UART/LPUART 傳輸:在外設傳輸結束時或在 DMA 緩沖區事件時喚醒

? 外設之間的橋。例如:通信外設傳輸的 ADC 轉換數據

? 從 SRAM 到另一個 SRAM 的數據傳輸

4、低功耗模式的選擇方法

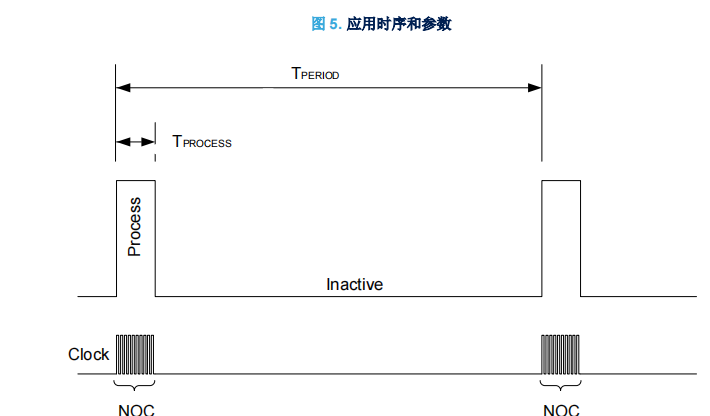

考慮一個簡化的應用模型,其中應用每隔 Tperiod 喚醒一次,始終執行一些相同操作并將指令數視為常數(無等待循環,無數據依賴)。然后可以進行以下近似計算:

? PROCESS 階段持續時間(Tprocess)可由每個階段要執行的時鐘周期次數(NOC)來定義。將 FCLK 定義為CPU 系統時鐘頻率,PROCESS 階段的持續時間等于 TPROCESS = NOC / FCLK。此階段的平均電流消耗等于Iprocess。

? INACTIVE 階段的持續時間為 TPERIOD - TPROCESS,其平均電流消耗為 IINACTIVE。

?

4.1 PROCESS 階段

根據處理要求(DMIPS),可以使用下列不同運行模式中的某一種:

? 具有 Range 1 電壓的運行模式,在 160 MHz 運行時最大可達 240 DMIPS

? 具有 Range 2 電壓的運行模式,在 110 MHz 運行時最大可達 165 DMIPS

? 具有 Range 3 電壓的運行模式,在 55 MHz 運行時最大可達 82.5 DMIPS

? 具有 Range 4 電壓的運行模式,在 25 MHz 運行時最大可達 37.5 DMIPS

選擇頻率時另一個需要考慮的參數是支持相關外設約束(如有)的能力。

4.2 INACTIVE 階段

STM32U575/585 期間提供了可用于 INACTIVE 階段的不同低功耗模式:

? 睡眠

? 停機 0(主調壓器開啟)

? 停機 1(具有低功耗穩壓器)

? 停機 2(具有低功耗穩壓器)

? 停機 3(具有低功耗穩壓器)

? 待機(具有 RTC 和 SRAM2 保留選項)

? 關斷(使用 RTC 作為選項)

根據喚醒源和睡眠周期持續時間,可選擇下述某一種模式:

? 睡眠:如果反應性是關鍵參數(此時喚醒時間僅為 8 個系統時鐘周期)

? 停機 0:當喚醒時間至關重要時(如果程序位于 Flash 中,則《2.5μs)

? 停機 1:如果有多個外設需保持喚醒且系統有多種喚醒源(此時應用必須能夠容許約 13 μs 的從 Flash 喚醒的時間)

? 停機 2:如果有少數外設需保持喚醒且能產生喚醒事件,如 DMA 傳輸完成、LPUART/SPI/I2C 傳輸事件、通

過 SDF 語音檢測、ADC 模擬看門狗(此時應用須能夠容許約 20 μs 的從 Flash 喚醒的時間)

? 停機 3:如果除 RTC 之外無其他外設需要在保留所有 SRAM 的情況下保持喚醒,在 FSTEN = 0 時從 Flash喚醒的時間為 66.5 μs

? 待機:如果除 RTC 之外無其他外設需要保持喚醒,并且需要保留不超過 64 KB 的 SRAM2(此時應用須容許在 MSIS = 4 MHz 且 FSTEN = 0 時從 Flash 喚醒的時間約為 64.5 μs)

? 關斷:如果只有 RTC 和備份寄存需要保持喚醒(此時應用須容許在 MSIS = 4 MHz 時約 610 μs 的喚醒時間)

喚醒時間取決于代碼位置(Flash)、系統時鐘源和頻率。詳細情況請參考[2]。上述從停機喚醒的圖形對應于 24MHz 或 4 MHz 時的 MSIS 且代碼在 Flash 中。為了縮短喚醒時間,建議在 PWR_CR2 中設置 FLASHFWU = 1 且SRAM4FWU = 1。

4.3 睡眠模式選擇

以下數值結果基于從文檔[2]中提取的 25°C 時的典型規格值。

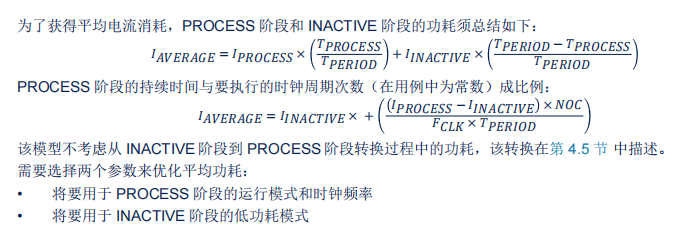

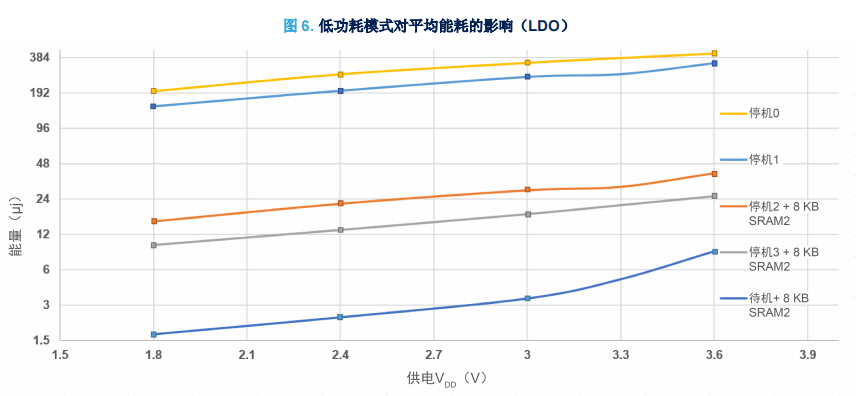

針對 RTC 處于 INACTIVE 階段的不同選擇的低功耗模式(睡眠、停機 1 、停機 2、停機 3、具有 RTC 和 SRAM2保留功能的待機、待機和關斷),下圖給出了作為主電源(VDD)函數的理論功耗。

前面的圖表明,對于需要保留一些數據的應用,待機模式可實現最佳能耗,而停機 3 模式是保留所有 SRAM 的最低功耗模式。如圖 7 所示,使用 SMPS 將能耗降至一半。

丟棄了關機模式(虛線),因為該模式無法為此類應用提供足夠的數據保持能力。

低功耗模式選擇不只是由總體功耗決定的,還與連接到該應用的其他喚醒考慮有關。圖 6 而且圖 7 表明,相比于待機,以少量額外功耗為代價,停機 2 和停機 3 模式針對喚醒的設置更加強大、簡單和快速(無需外設重新初始化)

?4.4 低功耗模式選擇

對于實際應用,根據喚醒周期,可使用下面的準則:

? 如果喚醒周期長于幾十 ms,則使用待機模式實現,可具有更好的功耗性能。

? 如果喚醒周期較短,則使用停機 2 或停機 3 模式實施效果則更好。

? 如果溫度較高,則最好使用待機模式。

低功耗模式選擇不僅依賴于功耗,還與喚醒時間要求(系統反應性)和數據保持要求有關。如果處理可適應低于 24 MHz 的頻率,則最優點如下:

? 待機或停機 3 模式

在待機模式下,最佳點是喚醒轉換時間長于 66μs、保留區低于 64KB SRAM + 2KB BKPSRAM。在停機 3 模式下,可以保留所有 SRAM。

? 停機 2 模式

最佳點是喚醒轉換時間長于 20μs 并且保留區大于 66KB (64KB SRAM2 + 2KB BKPSRAM)保留。

如果喚醒周期長于幾秒且無需保留內存,則關機模式下會有最好的功耗性能。這種情況下喚醒時間典型值為 610μs。

4.5 轉換的影響

為了完成這項研究,必須考慮在轉換階段(喚醒和停用)消耗的能量。

根據文檔[2],在 VDD=3.0V 時,使用 SMPS,離開低功耗模式時所消耗的能量大致為:

? 1.1 nAs,對于從停機 1 到運行模式的轉換(MSI = 24 MHz)

? 0.57 nAs,對于從停機 2 到運行模式的轉換(MSI = 24 MHz)

? 4.54 nAs,對于從停機 3 到運行模式的轉換(MSI = 24 MHz)

? 21.22 nAs,對于從待機到運行模式的轉換(MSI = 4 MHz)

? 457.29 nAs,對于從關斷到運行模式的轉換(MSI = 4 MHz)

5、ULPMark-CP 用例優化

5.1 ULPMark-CP 描述

ULPMark-內核配置文件(CP)基準側重于 MCU 內核,特別是睡眠中的能源成本,以及與激活模式之間的轉換。

該基準使用一組可在 8 位、16 位和 32 位微控制器之間移植的通用工作負載。內核配置文件以 1 秒的占空比運行,將這些工作負載與延長的不活動時間相結合,從而啟用微控制器低功耗模式。

在測試的激活部分,基準測試執行以下操作:

? 生成 20 個 GPIO 脈沖。

? 執行 8 位線性插值。

? 執行 16 位積分(過濾器)。

? 計算 7 段 LCD 二進制轉換(保存狀態)。

? 在字符串中搜索子字符串。

? 執行小型冒泡排序。

? 根據輸入和先前狀態置換字符串的位。

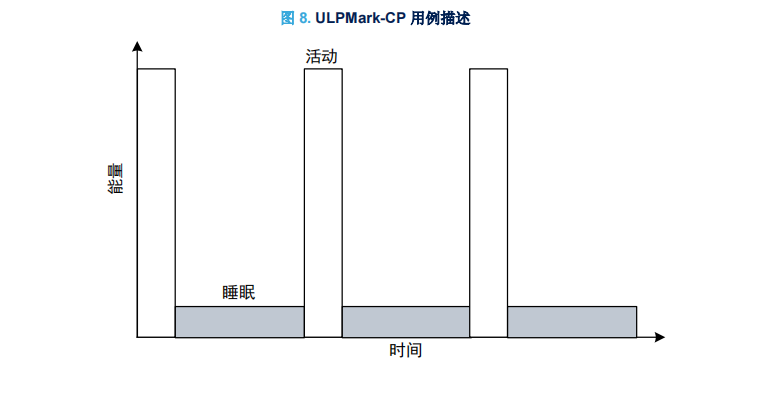

下圖顯示了 ULPMark-CP 基準在長時間睡眠中運行,隨后短暫喚醒以執行最少的處理,模擬睡眠邊緣節點來節省能源(更多詳細信息,請參見[5])。

5.2 應用約束條件

ULPMark-CP 規定了下列約束條件:

? 該應用每秒喚醒一次,基于精確 RTC 在一組數據上執行某些操作。

? 從一個處理周期到下一個處理周期時,數據需要保持。這要求在 INACTIVE 階段中能夠保持數據。

? 利用編譯器最強優化選項進行編譯時,應用所需的處理周期數約為每秒 10000 周期。

對于系統反應性不作特別約束,以便服務外部事件或 RTC 周期中斷。

5.3 PROCESS 階段優化

基準測試的激活部分僅運行總運行時間的約 3%,因此用戶可以使用內部 MSIS,使用對應于 16 MHz 電壓調節范圍4 的功率最佳點。在 16 MHz 標稱頻率下使用MSIS 時,其功耗低于使用 PLL 的任何其他解決方案。

為了進一步優化激活階段的功耗,可以應用以下步驟:

1. 在運行模式下關閉 SRAM1、SRAM2、SRAM3、SRAM4。

2. 將系統時鐘配置為 16 MHZ 的 MSIS 電壓調節范圍 4。

3. 將數據置于 BKPSRAM。

4. 禁用未使用的 AHB/APB 時鐘。

5. 將所有 GPIO 引腳置于模擬模式。

6. 關閉 Flash 存儲區 2。

7. 啟用 Flash 低功耗模式。

8. 配置編譯器優化(高速,無大小限制)。

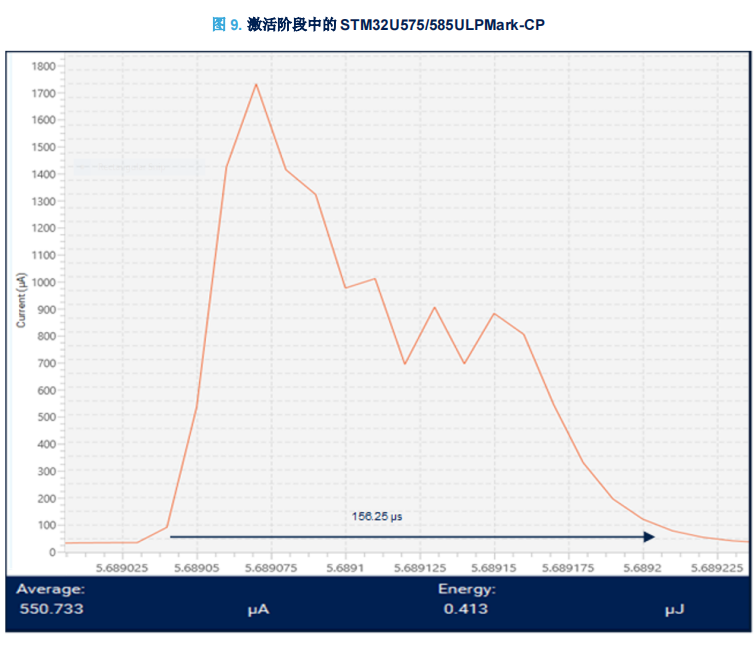

下圖顯示了處于激活階段的 ULPMark-CP。從喚醒到進入低?功耗模式大約需要 156μs,在 16 MHz 系統時鐘 MSIS的運行模式下消耗 550 μA 電流。

5.4 INACTIVE 階段優化

ULPBench-CP 基準要求從一次運行到下一次運行時能夠在低功耗模式下保持數據變量無變化。因此,不可使用關機模式,因為該模式無法為該應用提供足夠的數據保持能力。

停機 3 模式可在保留 8 KB SRAM2 或 2 KB BKPSRAM 以及最短喚醒時間的條件下使用。然而,最節能的解決方案是使用待機模式并且具有 RTC 和 8 KB SRAM2 或 2 KB BKPSRAM 數據保持。

為了進一步優化 INACTIVE 階段的功耗,可以應用以下步驟:

1. 啟用 SMPS 調壓器。

2. 啟用 ULPMEN 位。

3. 在停機 3 模式下關閉未使用的 SRAM。

4. 禁用 AHB/APB 外設的所有時鐘(RTC 的 AHB3/APB3 除外)。

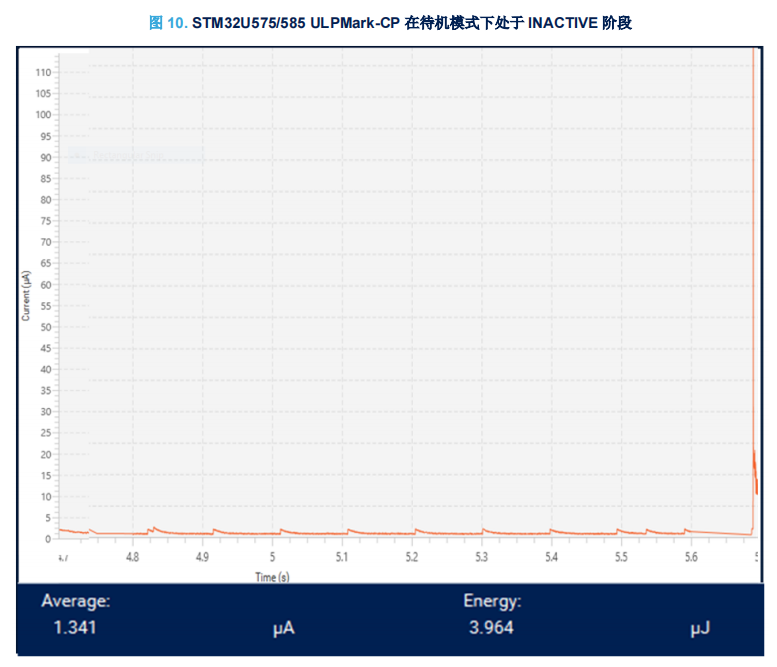

下圖顯示了待機模式下處于 INACTIVE 階段的 ULPMark-CP,其中平均電流消耗為 1.34μA。

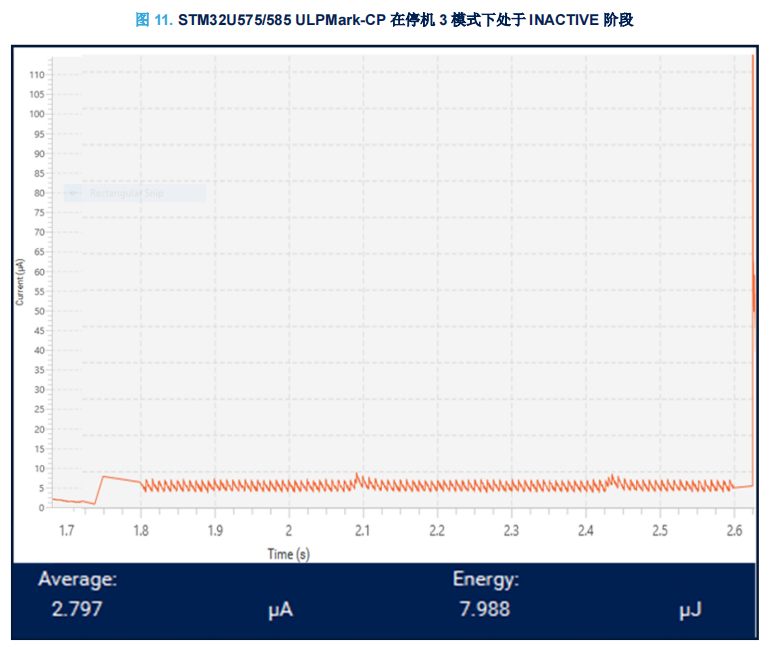

下圖顯示了停機 3 模式下處于 INACTIVE 階段的 ULPMark-CP,其中平均電流消耗為 2.97μA。

在 ULPBench 基準的情況下,喚醒周期為 1 秒,處理載荷約為每秒 10 K 循環時,最佳選擇是在 INACTIVE 階段使用待機模式,在 PROCESS 階段關聯地使用 16 MHz(來自 MSIS)下電壓調Range 4 模式。

5.5

STM32U575/585 測量結果

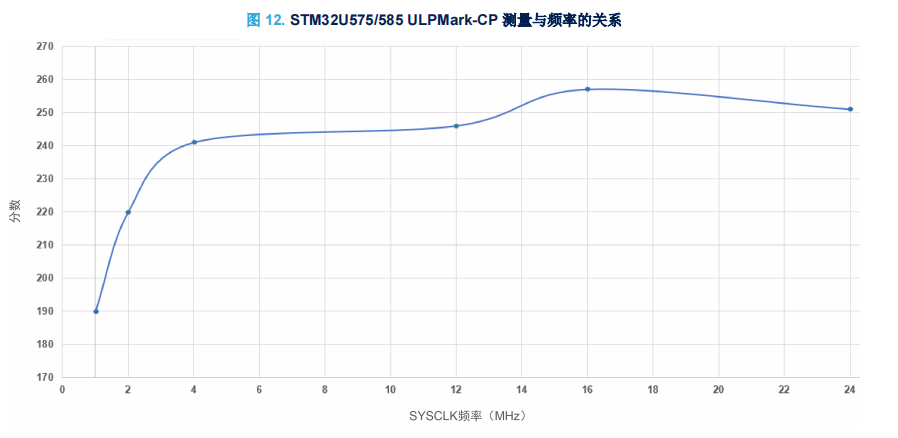

下圖顯示了在 PROCESS 階段使用不同系統時鐘頻率進行的 ULPMark-CP 得分測量,其中非活動階段使用具有BKPSRAM 保留和 RTC 功能的待機模式。

結果提供了不同的時鐘配置:對于低于 24MHz 的頻率,使用 MSI(因為從待機模式喚醒時會自動啟動)。

如在理論研究中已經看到的,使用電壓調節范圍 4 在 16 MHz 時,使用 MSIS 實現最佳結果。

5.6 電壓范圍內的性能演變

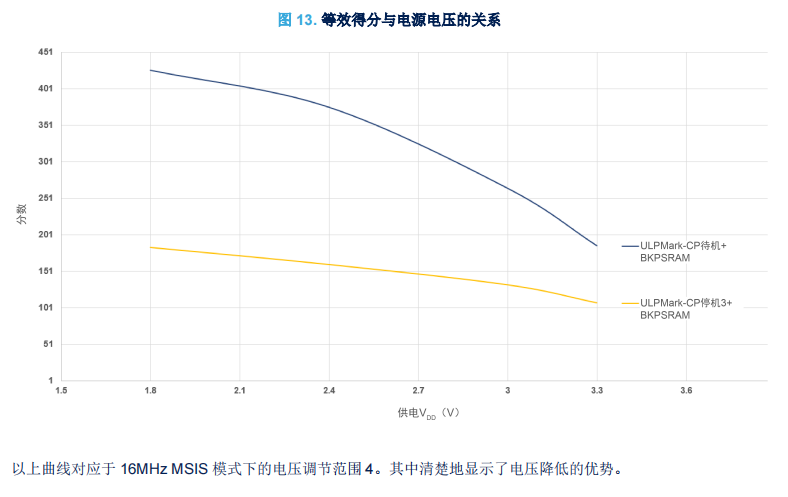

EEMBC 定義了 3.0V 的基礎測試默認值,但該電壓并不代表電池供電的低功耗應用。使用 LDO 調壓器時,與保持在 3.0V 相比,移至較低電壓時的功率增益明顯。相反,當使用 SMPS 調壓器增加 VDD 時,功耗降低。這就是為什么 EEMBC 引入了用戶定義電壓的比較,讓制造商選擇理想的工作條件。

下圖顯示了不同電壓下的 ULPMark-CP 得分測量。

6、結論

本應用筆記介紹了 STM32U575/585 微控制器的超低功耗特點。它們顯示了此微控制器系列在嵌入式系統中降低電流消耗方面所具有的優勢。無論何種應用,這些器件均可在優化性能和功耗方面提供多種選擇。

基于實驗和定量結果,本文檔提供了相關指南,幫助根據終端用戶應用的特點和約束條件,快速選擇最佳運行和低功耗模式。

電子發燒友App

電子發燒友App

評論