這篇應用筆記描述了怎么使用STM32F101xx和STM32F103xx的直接內存訪問(DMA)控制器。STM32F101xx和STM32F103xx DMA控制器、Cortex-M3內核、先進的微控制器總線架構和存儲系統,是為了提供一個高的數據帶寬,并開發響應時間非常快的軟件。這篇文檔也描述了怎樣充分利用這些特性,以及對于不同的外設和子系統怎樣保證正確的響應時間。

在下文中STM32F101xx 和STM32F103xx都記作STM32F10xxx,DMA控制器都記作DMA。

1、DMA控制器

DMA是一個AMBA先進的高性能總線(AHB),它的特點是它具有兩個AHB端口:一個從端口,用于DMA編程;一個是主端口,主端口允許DMA在不同的從模塊間發起數據傳輸。

DMA允許數據傳輸在后臺傳輸,而不需要Cortex-M3處理器的干預。在這個操作中,主處理器能夠執行其他的任務。CPU僅僅在要處理的數據塊傳輸完畢后才被中斷。大量的數據傳輸的同時不會對系統性能產生大的影響。

DMA主要用來為不同的外設模塊實現數據緩沖存儲(一般存儲在系統的主存儲器中)。這種解決方案和分布式解決方案(每個外設需要實現自己當地數據存儲)相比,無論在硅的使用和功耗上都要更勝一籌。STM32F10XXXDMA控制器充分利用了Cortex-M3 Harvard架構和多層的總線系統來保障非常低的DMA數據傳輸延時和CPU執行/中斷事件檢測/服務。

1.1 DMA的主要特性

DMA具有以下的特性:

1、7個DMA通道(channel 1到7)支持單向的從源端到目的端的數據傳輸;

2、DMA通道優先級可通過硬件和軟件編程;

3、支持存儲器到存儲器,存儲器到外設,外設到存儲器,外設到外設的數據傳輸;

4、能夠對硬件/軟件傳輸進行控制;

5、傳輸時內存和外設指針自動增加;

6、傳輸數據的大小可編程;

7、總線錯誤自動管理;

8、循環模式/非循環模式;

9、可傳輸高達65536個數據。

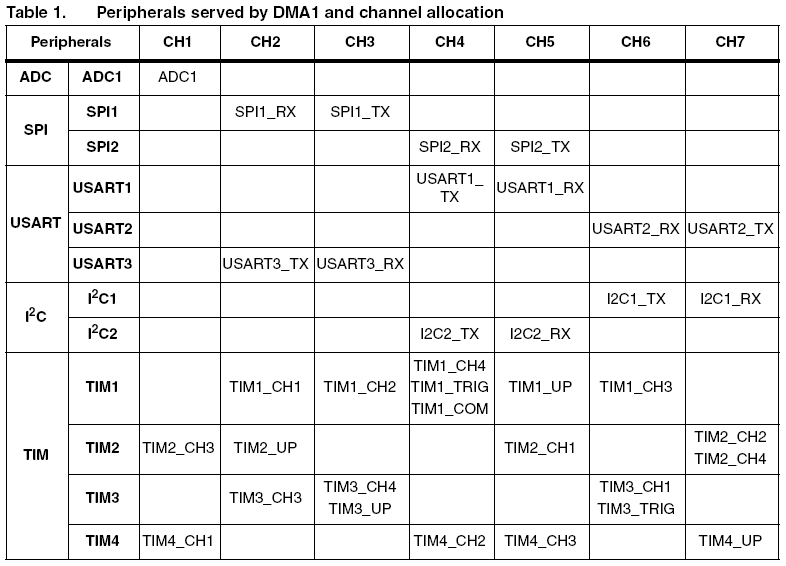

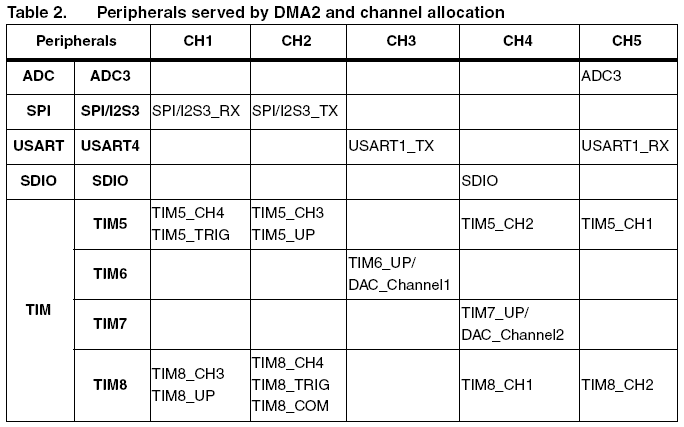

DMA目標是為所有外設提供相關的大的數據緩沖區,這些緩沖區一般位于系統的SRAM中。每一個通道在特定的時間里分配給唯一的外設,連接到同一個DMA通道的外設不能夠同時使用(在DMA活躍時),所有的

連接到給定的通道的外設中只有一個能夠擁有DMA功能。

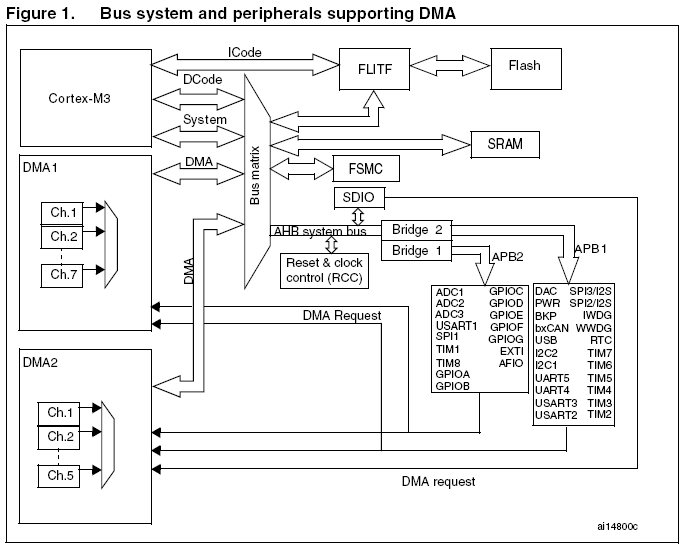

支持DMA的外設如下表, DMA服務的外設和總線系統結構也在下圖中:

2、性能考慮

STM32F10xxx有兩個主模塊Cortex-M3處理器和DMA。他們通過總線矩陣連接到從總線,Flash Memory總線,SRAM總線和AHB系統總線。從總線輪流連接到兩個APB總線以服務所有的嵌入的外設(參見上圖)。總線矩陣有兩個主要的特性,實現系統性能的最大化和減少延時:1、循環優先級調度;2、多層結構和總線挪用。

2.1 循環優先級調度

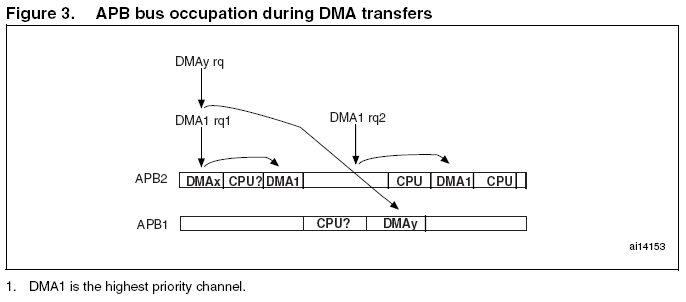

NVIC和Cortex-M3處理器實現了高性能低延時中斷調度。所有的Cortex-M3指令既可以在單周期內執行,也可以在周期級上被中斷。為了在系統水平上保證這個特性,DMA和總線矩陣必須確保DMA不能夠長時間占用總線。循環優先級調度能夠確保CPU能夠在任何一個周期訪問所有的從總線。因此,第一個數據最大總線系統延時在CPU看來,就是一個總線周期(兩個APB時鐘周期的最大值)。

2.2 多層結構和總線挪用

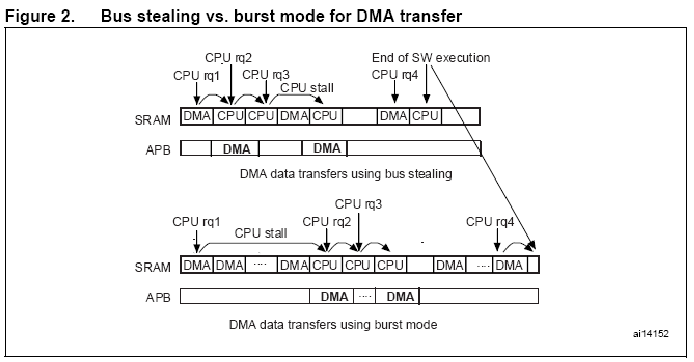

多層結構允許兩個兩個主設備并發執行數據傳輸,只要它們尋址到不同的設備。在Cortex-M3哈佛架構,這種結構提高了數據的并行性,因此減少了執行時間并且優化了DMA效率。從Flash存儲器取指是通過完全獨立的總線,所以DMA和CPU只是在需要通過一個給定的從總線進行數據訪問時才會產生競爭。當其他DMA控制器工作在突發模式下,STM32F10xxx DMA的數據傳輸(總線挪用)只需要單個總線周期。當使用總線挪用存取機制時,CPU等待數據的最大時間是很短的(一個總線周期)。CPU訪問SRAM和DMA存取就是自然地交叉存取。CPU訪問和DMA通過APB總線存取外設就可以并行進行。即使更多的數據訪問使用突發模式DMA可能會更快些,CPU停止的那段長時間很少被復原。下圖列出了總線挪用和突發機制的區別。

在極端的情況下(CPU從內存的一個地方復制一塊數據到內存中的另一個地方),軟件的執行必須等到整個DMA傳輸完畢。當然,CPU大部分時間完成的是數據處理,CPU和DMA交叉存取數據的頻率很低。STM32F10XXX總線結構固有的并行性,加上DMA總線挪用機制保證了CPU不會長時間地等待從SRAM中讀取數據。總線挪用機制的DMA使總線使用效率更高,明顯地減少了軟件執行時間。

2.3 DMA延遲

DMA完成從外設到SRAM 存儲器的數據傳輸有三個步驟:1、DMA請求仲裁;2、從外設中讀取數據(DMA源);3、將讀取的數據寫入到SRAM中(DMA目的地)。

當DMA把數據從內存中傳輸到外設(例如SPI傳送),操作必須按照以下順序:1、DMA請求仲裁;2、從SRAM中讀取數據;3、將讀取到的數據通過APB總線寫入到外設中。

每個通道總的服務時間是總裁時間(1個AHB時鐘周期),外設訪問時間(2個AHB時鐘周期)和SRAM讀/寫訪問時間(1個AHB時鐘周期用于單獨的讀/寫操作,2個周期用于寫操作后SRAM讀)的和。

當DMA通道空閑或者是第三個操作完成后,DMA比較所有掛起的DMA請求的優先級,高優先級的通道將會被服務,DMA開始執行第二個操作。當一個通道正在服務時(第二,三個操作正在進行),沒有其他的通道能夠被服務,而不管它的優先級如何。

當至少同時有兩個DMA通道使能時,最高優先級通道的DMA延遲時間為正在傳輸的時間加上下個將被服務的DMA通道(掛起優先級最高)。

2.4 數據總線帶寬限制

數據總線帶寬限制主要是因為APB總線比系統SRAM和AHB總線速度慢。對于最高優先級通道,以下兩種情況是需要考慮的:

1、當多余一個DMA通道使能時,最高優先級通道在APB總線上的請求數據帶寬必須比APB傳輸率低25%

2、盡管高速/高優先級DMA傳輸通常發生在APB2上(更快的APB總線),但是CPU和其他DMA通道可以在APB1上訪問外設。大約3/4的APB傳輸是在APB1上完成的,最小的APB2頻率依賴于最快的DMA通道數據帶寬,最大的APB時鐘分頻因子由下列的等式給出:

fAHB〉(2*N2+6*N1)*BMAX

如果N2< N1 則N1<( fAHB/ BMAX)/8

其中fAHB是AHB時鐘頻率;

N2和 N1是APB1和APB2的時鐘分頻因子;

Bmax是APB2上的最大并行數據帶寬。

2.5 通道優先級選擇

為了實現外設數據的連續傳輸,相關的DMA通道必須能夠維持外設數據傳輸率和確保服務的延遲時間比兩個連續的數據之間的時間短。

高速/高帶寬外設必須擁有最高的DMA優先級,這確保了最大的數據延遲對于這些外設都是可以忍受的,而且可以避免over/under-run的情況。

在相等的帶寬需求的情況下,推薦給工作在從模式下(沒有數據傳輸速度控制)的外設分配的優先級比工作在主模式(能夠控制數據流)下的外設分配的優先級高。

缺省情況下,通道分配和硬件優先級(從1到7)是按照最快的外設分配最高優先級的順序來分配。

當然,在某些運用場合下也許不是按照這樣來分配的,在這種情況下,用戶能夠為每一個通道配置軟件優先級(分4種,從非常高到低),軟件優先級優先于硬件優先級。

當幾個外設(不管有沒有使用DMA)并行使用時,用戶必須確保內部系統能夠維持運用所要求的總的數據帶寬,必須從下列因素中選擇一個折中方案:1、每個外設的運用需求;2、內部數據帶寬。

2.5.1 運用需求

以SPI接口為例,SPI接口數據帶寬是通過波特率除以SPI的數據字長度而得到的(由于一個滿數據需要在每次發送之前/之后傳輸到/傳輸自SPI),假設SPI的波特率是18M,數據是以8位傳輸的,操作配置在單一模式

下,內部數據帶寬需求是2.25M/s,如果SPI在16位模式下,則數據帶寬將是1.125M/s。

2.5.2 內部數據帶寬

內部數據帶寬依賴于以下兩個條件:1、總線頻率 可獲得的數據帶寬與總線時鐘頻率是成正比的;2、總線類型 AHB數據傳輸需要一個時鐘周期(除了SRAM寫后讀訪問需要2個周期),數據通過APB總線傳輸給外設需要花費2個APB時鐘周期。

推薦DMA總線使用保持在2/3以下,這樣系統和CPU的性能就可在合理的水平。

3、DMA編程示例

所有的示例都使用STM32F10xxx固件庫,可以參考AN2564 STM32F10XXX DMA運用的例子。相關的固件庫可以在ST網站上下載,網址為www.st.com

3.1 使用SPI傳輸實現ADC連續數據的獲取

ADC配置為連續轉換模式,該模式下,它能夠將一個輸入通道以最大速度進行連續轉換。為了獲得最大的連續轉換速度,AHB總線頻率設置為56MHz,ADC預分頻為4,采樣速度為13.5周期。這些設置通過DMA通道1傳輸到位于系統RAM中的緩沖區,通道1的數據帶寬設置為0.54M/s。

當ADC轉換后的數據填充了緩沖區的一半后,軟件計算出最大值并且是這些數字化的數據規格化(最大值設置為0xFF),ADC轉換的結果通過SPI接口傳輸到外部。ADC轉換結果是通過SPI1接口來傳輸的,使用DMA通道3把數據從SRAM緩沖區中傳輸到SPI1的數據寄存器。要達到最大的DMA傳輸的速度0.875M/s,SPI1接口必須配置為16位主傳輸模式、14M波特率的傳輸速度。

可是,當SPI1工作在主模式,SPI1有效的數據傳輸速度受數據的可用速率1M/S的限制時,優先級的配置如下:通道1(ADC):VeryHigh,通道3(SPI1_TX):High。

3.2 SPI直接傳輸實現ADC連續數據的獲取

這個示例完成的功能和前面一個幾乎相同,沒有數據的標準化。CPU內部并沒有使用這些數據,直接把ADC轉換結果傳輸到SRAM緩沖區可以較少一半的總線占用。所以,僅有DMA通道1被使用,該通道的目的存儲器地址設置為SPI數據寄存器,而不需要SRAM緩沖。

3.3 使用DMA實現GPIO快速數據傳輸

這個示例展示了如何將不同的外設用于DMA請求和數據傳輸。這個機制允許在沒有使用CPU的情況下實現簡單的快速并行同步接口。Timer1和DMA通道4連接到TIM1_TRIG,用來實現獲取數據的接口,在GPIO的端口上可以獲取8位并行數據,一個外部時鐘信號作用在Timer1的外部觸發器輸入端。在外部觸發器上升沿,定時器產生一個DMA請求,只要GPIO數據寄存器地址已設置到DMA通道4的外設地址,DMA控制器在每一次DMA請求時從GPIO端口讀取數據,并把它存儲到SRAM的緩沖器中。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論