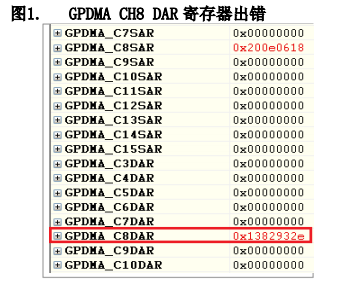

我這里也設計了兩輪DMA傳輸,照樣使用TIMER更新事件觸發ADC轉換。第一輪DMA傳輸傳輸3個AD轉換結果到某內存地址,第二輪傳輸5個轉換結果到另一內存位置。

2020-06-18 09:39:00 3838

3838

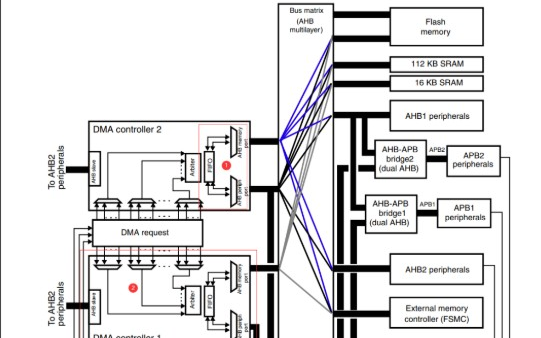

基于上面章節的需求,Linux kernel從虛擬內存(VM)、DMA mapping以及DMA buffer sharing三個角度,對內存進行管理.

2020-09-19 11:55:15 1437

1437

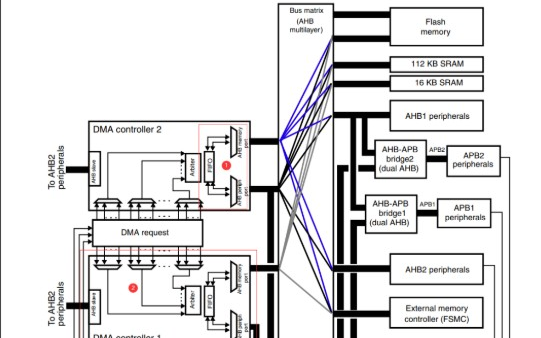

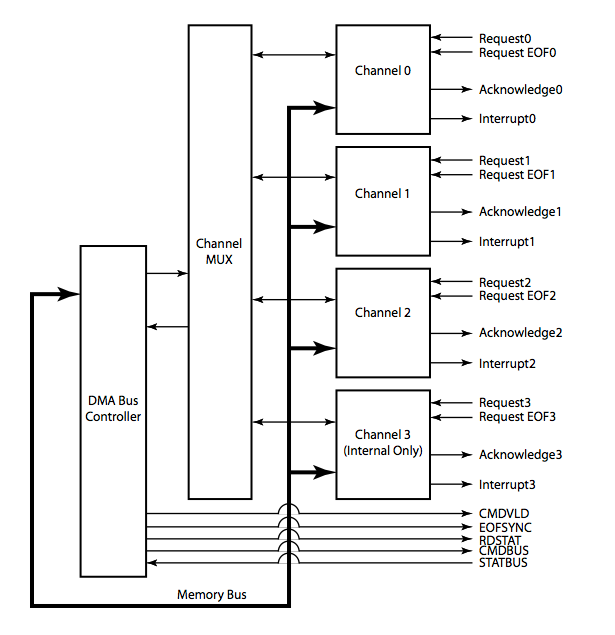

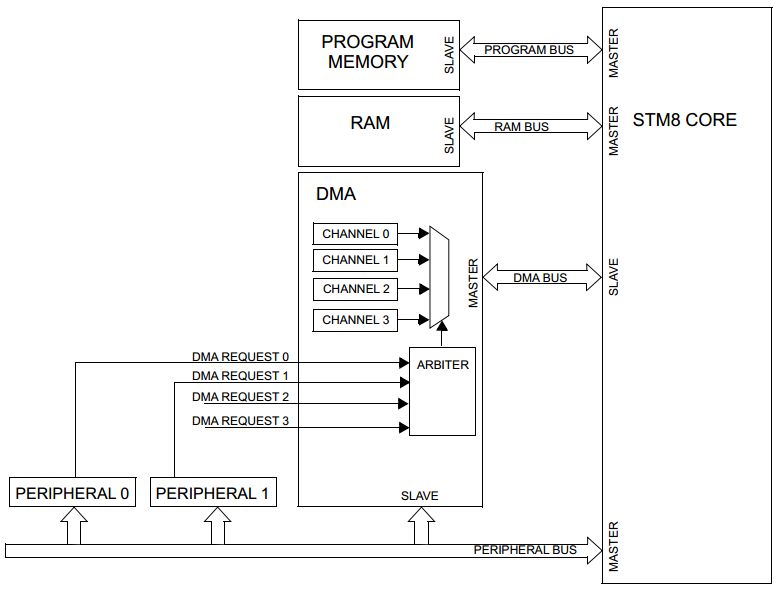

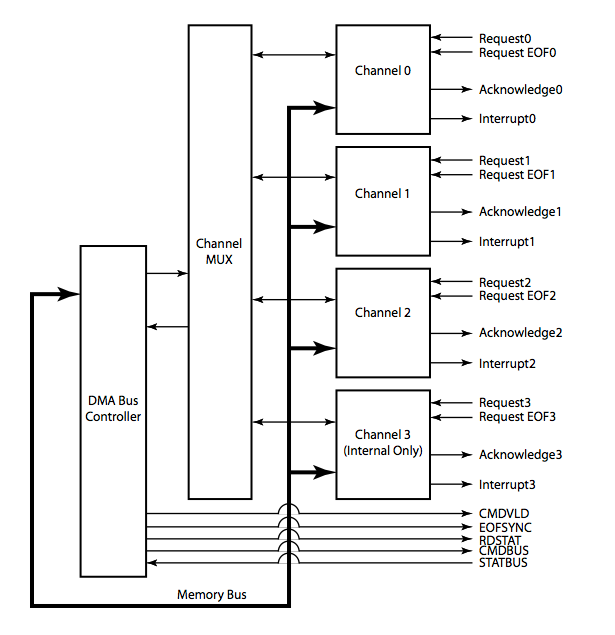

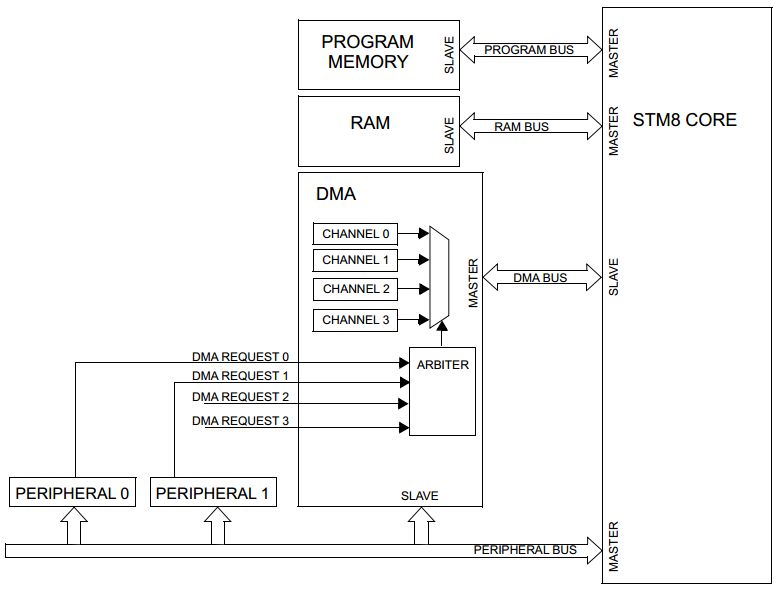

給中斷控制器; 5. 擁有8個DMA觸發事件并且可以編碼控制; 6. 128個(64bit)的MFIFO,在傳輸的時候讀寫端可寫入到此FIFO; 7. 支持任意內存到內存的傳輸; 整個系統中的DMA

2020-12-05 10:17:17 3606

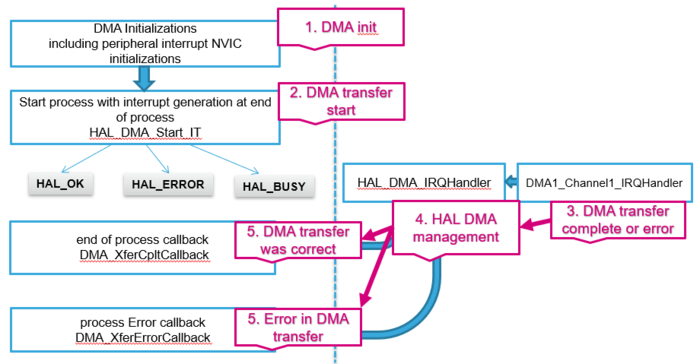

3606 ,當床書數目變為0是,將會自動的被恢復成配置通道是設置的初值,DMA操作將會繼續進行。五、1.錯誤管理2.中斷:每個通道傳輸一半、完成或錯誤時,可以使用單獨的中斷使能信號產生中斷。3.DMA請求映射

2013-06-13 12:50:24

rtthread怎么申請物理連續的1K內存供DMA傳輸使用

2022-06-07 09:10:02

//DMA內存傳輸到串口完成中斷實驗,自己編寫回調函數并注冊到dma句柄即可usart.h--------extern DMA_HandleTypeDef hdma_usart1_tx

2021-08-13 08:08:11

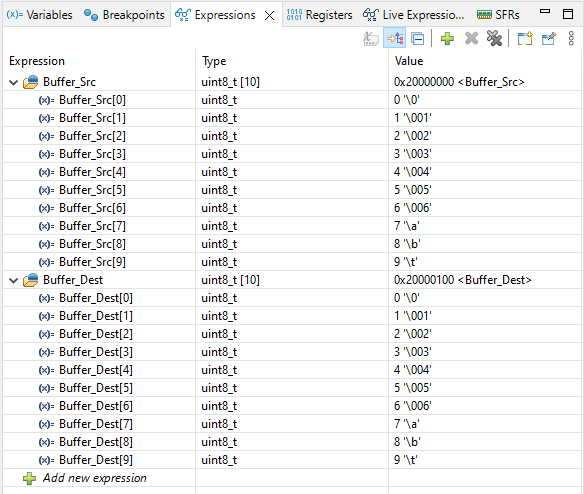

DMA內存到內存后的數據串口讀不出來,只能讀出原始數據,為何?

將chtx復制到chrx,然后串口分別輸出來,結果不能輸出chrx,

主要代碼如下:

uint8_t chtx[10

2023-10-27 07:39:39

上搬移數據。推廣出來,該通道上其它請求信號也可以啟動數據的傳輸。后記值得一提的是,DMA不僅支持內存上的數據傳輸,還支持外設之間,外設到內存,內存到外設的數據傳輸。說白了,外設、RAM、ROM都是依靠

2015-01-22 16:17:58

開辟20kb左右的緩存空間,如果直接用全局變量數組,在不需要用到DMA時,那這20k的內存就一直不能釋放,好浪費。若使用malloc來開辟動態內存,應該是放在堆區吧?堆區不是默認只有512字節?還要修改啟動文件的堆大小?

2023-10-23 06:53:54

開辟20kb左右的緩存空間,如果直接用全局變量數組,在不需要用到DMA時,那這20k的內存就一直不能釋放,好浪費。若使用malloc來開辟動態內存,應該是放在堆區吧?堆區不是默認只有512字節?還要修改啟動文件的堆大小?

2018-04-20 14:30:30

使用dma_alloc_coherent申請了一塊內存,然后使用mmap映射到用戶空間。然后,我用千兆網卡(CPSW驅動)進行發送(UDP方式),測量到的速度僅有12.5MB/s。 我又另外做了一個測試

2018-06-04 07:47:02

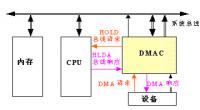

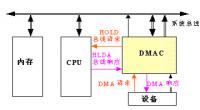

1:DMA(DIRECT MEMORY ACCESS)即直接存儲器存取,是指外部設備不通過CPU而直接與系統內存交換數據的接口技術。 要把外設的數據讀入內存或把內存的數據傳送到外設,一般都要通過

2022-02-22 08:07:17

指示了內存大小這可以理解,但是在SECTION部分居然 把 外設這些內容分配到上面些指示的內存部分,小弟搞不明白了,既然這些內存是邏輯上的,那怎么還給他分配存儲內容啊??分配了這些內容存到哪里啊??我個人認為好像應該把要存儲的內容都分配到想DDR這些實實在在存在的內存,求大神們稍微給解釋下???

2020-04-01 10:58:05

) 什么是 DMA· 直接內存訪問是一種硬件機制,它允許外圍設備和主內存之間直接傳輸它們的 I/O 數據,而不需要系統處理器的參與2) DMA 控制器的功能· 能向 CPU 發出系統保持(HOLD)信號

2020-08-24 07:44:49

框大小的內存時可以使用vmalloc建立非連續物理內存到虛擬地址的映射物理不連續,適合需要大內存,但是對地址連續性沒有要求的場合dma_alloc_coherent基于_alloc_pages 實現

2020-08-25 07:42:08

至斷點2,UART中斷狀態寄存器UART_ISR的RXIDLE_INTF位清0。這時串口接收到的數據就自動保存到了DMA初始化中你填寫的那個內存基地址所在的內存區域了,想什么時候用就什么時候用。原作者:果果小師弟

2022-07-06 11:28:40

DMA的一些問題,具有信道優先級:內存到內存的傳輸似乎干擾內存到外圍傳輸。我最多使用4個通道:-CHANNel 0用于定期更新SPI LED驅動器的緩沖區(每500us更新一次),使用SPI模塊2通道1從

2019-08-14 09:28:31

廢話不說了,直接上代碼:我的思路是這樣的:AD采集的值通過DMA方式傳輸到內存,然后再請求使用DMA方式將數據直接打印到串口!下面是DMA的配置!!! u16

2018-11-06 08:45:22

內存到外設*/29.DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralDST;30./*禁止內存到內存的傳輸

2014-03-26 10:05:22

); DMA_InitStructure.DMA_BufferSize = 12;// 緩存大小 DMA_InitStructure.DMA_M2M = DMA_M2M_Disable; // 內存到內存關閉

2018-06-28 10:20:48

_M2M = DMA_M2M_Disable; // 內存到內存關閉DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;// 普通模式

2018-07-02 06:37:32

和目的地傳輸數據大小:字節,

半詞或單詞。

?每個通道有3個事件標志:DMA半傳輸、DMA傳輸完成和DMA

傳輸錯誤。

?內存到內存、外設到內存和內存到外設傳輸

外圍設備到外圍設備的傳輸。

?如果出現

2023-09-12 06:06:45

STM32H750在使能內存保護后啟用cache 導致SPI+DMA傳輸不準確,具體就是調用HAL_SPI_TransmitReceive_DMA 這個函數,讀到的數據全是0,但是拿邏輯分析儀看上面顯示的數據是正確的。

2024-03-07 06:12:42

:字節,

半詞或單詞。

?每個通道有3個事件標志:DMA半傳輸、DMA傳輸完成和

DMA傳輸錯誤。

?內存到內存、外設到內存和內存到外設傳輸

外圍設備到外圍設備的傳輸。

?如果出現總線訪問錯誤,故障通道將自動硬件禁用。

?可編程的數據傳輸數量:最高可達65535。

?支持循環緩沖區管理。

2023-09-07 06:52:59

STM32U575 定時器PWM觸發DMA搬運內存,為什么程序在DMA中斷里出不來?

2024-03-12 08:33:11

; DMA_InitStructure.DMA_DIR=DMA_DIR_PeripheralDST;//設置為 內存到外設的傳輸方式 DMA_InitStructure.DMA_M2M=DMA

2018-07-02 05:18:05

DMA_ClearITPendingBit(DMA_IT_TC);2、覺得的這個傳輸過半中斷很好用,可實現類似雙緩存功能,即把內存區設置為要傳輸的字節數(例如串口傳輸)的兩倍,DMA填滿一半了,啟用(串口)傳輸,DMA完成了,再傳DMA內存區的后一半。

2014-12-31 10:55:53

/DDR3內存 --> 光纖/RocketIO GTP/GTX接口.3. 寄存器訪問:軟件訪問FPGA內部與DMA傳輸相關的寄存器.4. FPGA發出Doorbell中斷.如有Serial RapidIO相關方面的技術合作,可聯系我。聯系方式:neteasy163z@163.com

2014-08-23 13:27:47

您好,

我正在使用 Traveo CYT2B7,我想要使用 P-DMA 連續將 ADC 的 16-bit 采樣結果傳輸到內存中,請問每 16-bit 的數據傳輸是否是原子傳輸?在 P-DMA 傳輸過程中,CPU 同時讀取內存中目的地址的數據是否會出現錯誤數據(既不是新的數據也不是舊的數據的情況)?

2024-02-02 12:36:05

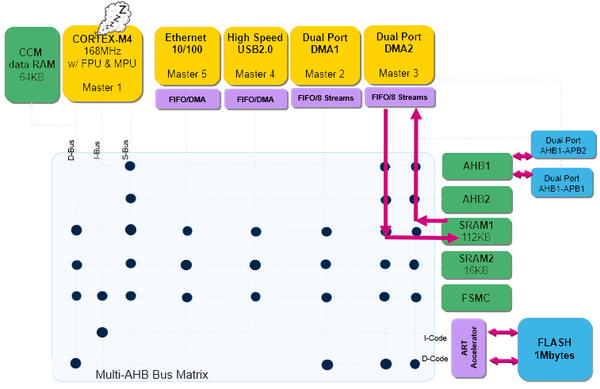

不同類型的DMAHigh performance w/DMA幾種DMA的總結ZYNQ中不同應用的DMA幾個常用的 AXI 接口 IP 的功能(上面已經提到):AXI-DMA:實現從 PS 內存到

2022-03-31 11:39:10

*/NVIC_Config();/*傳輸大小*/DMA_InitStructure.DMA_BufferSize = SENDBUFF_SIZE;/*方向:從內存到外設*/DMA_InitStructure.DMA

2014-03-13 16:33:43

了,數據從內存到外設,或者外設到內存,或者內存到內存都不需要CPU的參與,直接存儲器訪問即可,減輕了CPU的壓力。既然有了增加了DMA,所以我們的串口終端服務函數也要修改一下了。在中斷服務函數中,當

2022-07-20 15:03:09

大家好,這是關于DMA的非常基本的問題。1)什么是DMA(直接內存訪問)和什么時候使用?2)它是如何提高CPU性能的?或如何獨立工作,以節省時間和更快的性能和減少延遲?3)什么是間接的和平的模式?4

2019-01-25 10:45:34

STM32 DMA簡述**DMA (Direct Memory Access) ** 直接內存存儲器,在做數據傳輸時能夠大大減輕CPU的負擔。DMA的作用DMA提供了一個關于數據的高數傳輸通道,這個

2022-01-11 07:36:06

。與之相反的是,主機發送DMA寫指令和數據要放主機內存首地址給FPGA,FPGA根據內存首地址和數據長度發起帶數據Mwr,這樣就數據傳送到主機,稱為DMA寫操作。

1024Byte DMA讀,主機到

2023-11-17 15:08:37

我找不到任何有意義的文件,用于USB DMA W/自動內存管理。有一個例子被張貼在論壇,但是它不顯示任何數據傳輸,所以大多是無用的,一些正確的問題被問在論壇上卻沒有回答。我不知道這種模式是不被任何人

2019-09-05 09:47:45

增加了S/G傳輸模式,它卸載了處理器對寄存器的讀寫,通過獨立的S/G讀寫通道對存儲著命令描述符的內存進行訪問讀取、處理描述符,然后更新描述符寫入內存。幾種應用DMA的場合表4?20三種DMA的應用場合幾種

2022-10-14 15:23:41

利用XIlinx V6評估板ML605實現PCIE2.0,8通道主模式DMA數據傳輸,DMA由FPGA發起,采用1GB DDR3作為FPGA板卡大緩存,實現FPGA到PC內存(寫操作)和PC內存到

2013-04-25 12:48:30

使用stm32f429的dcmi接口接攝像頭,dma雙緩沖讀取圖像數據,u***-hs上傳數據(圖像數據有10MB)。問題:如何使內存中的圖像數據通過u***的dma方式傳輸。

2019-06-13 09:22:55

我正在嘗試以循環模式通過 DMA 將數據從 ADC 直接發送到 FMAC 。來自 STM32G4 參考手冊 (dm00355726) 第 402 頁:“外設到內存、內存到外設、內存到內存和外設

2023-01-06 07:12:11

如何減少存儲空間?如何控制脈沖數量?如何解決DMA傳輸數據耗內存的問題?

2021-12-21 07:53:15

我目前正在使用雙核 STM32H745,并且正在嘗試利用兩個內核上的 DMA 對共享內存進行讀/寫。DMA 僅在 M4 內核上成功,并且總是產生 DMA 傳輸錯誤。我沒有做任何事情來修改內核之間 DMA 外圍設備的初始化(默認情況下,Cube 會初始化兩個內核上選擇的所有 DMA)。

2023-01-17 07:51:24

Stm32之DMA直接內存讀取1.DMA簡介:DMA*(Direct Memory Access controller)*:可用于為CPU減負,可以將內存中的數據與外設中的數據進行搬運(無法進行計算

2022-02-14 07:30:36

ADCHS FIFO 傳輸到用戶內存。我無法讓他工作。為了簡化事情,我首先設置了一個內存到內存的傳輸,使用 DMA 控制器作為流量控制器。這工作正常。接下來我嘗試使用 DMA 控制器作為流控制器進行內存到

2023-04-07 06:55:59

監聽到的數據全是0,但是字節數是對的!但用DEBUG調試的時候,若用memory monitor 查看DMA指向的內存后,UART輸出的數據就對了;而不用memory monitorDMA指向的內存

2014-12-13 21:59:48

慕課電子科技大學.嵌入式系統.第十章.中斷時間和內存管理.內存管理0 目錄10 中斷時間和內存管理10.3 內存管理10.3.1課堂重點10.3.2測試與作業11 下一章0 目錄10 中斷時間和內存管理10.3 內存管理10.3.1課堂重點10.3.2測試與作業11 下一章博客地址: ...

2021-12-17 07:37:40

網上有說DMA內存到外設間傳輸數據的過程為:1、內存 到 外設2、內存 到 DMAC 到 外設3、內存 到 數據總線 到 DMA數據緩沖器 到數據總線 到 外設 那么,到底是哪一種情況呢?還有

2019-01-30 06:36:30

做產品時用到了16K的內存到內存的數據DMA傳輸,看了一下STM32的DMA手冊,說會占用一定的系統總線,到網上查了一下,基本也很難說準底在進行DMA傳輸時對CPU影響有多大,所以拿出來大家討論一下,誰做過這方面的實驗也可以講講,看看在進行DMA數據傳輸時,對CPU的執行速率有多大影響。

2018-11-13 10:25:36

第二個頻道。這一個鏈接到第一個(內存到內存4字節傳輸)的末端,但是只有2字節長,因為我想同時傳送第二個計數器的結果。我假設這是愚蠢的,因為它只有在第一個TD(4字節后面2個字節)之后才出現,但是如果

2019-08-06 13:25:22

緩存到內存中后,然后中斷完成標志位置1,再進入中斷服務函數,打印出500個數據?還是DMA接收1個數據后,就進入中斷函數打印這個數據,然后循環進行直到取滿500個數據呢?程序例子如下:while (1

2018-08-23 13:38:09

特點:(1)VMIC反射內存是一種通過局域網在互連的計算機間提供的數據傳輸的技術,強實時網絡設計人員已經越來越多地采用這種技術。VMIC反射內存實時局域網的概念十分簡單,就是設計一種網絡內存板,在

2022-10-09 14:18:29

特點:(1)VMIC反射內存是一種通過局域網在互連的計算機間提供的數據傳輸的技術,強實時網絡設計人員已經越來越多地采用這種技術。VMIC反射內存實時局域網的概念十分簡單,就是設計一種網絡內存板,在

2022-10-11 10:22:41

板載128Mbyte內存或256M內存 2. 網絡傳輸高速,實時,確定 3. 高速光纖網絡波特率可達2.125G 4. 低延遲率:節點間百納秒級延遲

2023-06-02 15:15:37

dma是什么意思? 什么是dma?

DMA的英文拼寫是“Direct Memory Access”,漢語的意思就是直接內存訪問,是一種不經過CPU而直接從內存了存取數據的數據交換模式

2008-04-17 17:06:03 34055

34055

主板支持的內存傳輸標準有哪些? 內存傳輸標準是指主板所支持的內存傳輸帶寬大小或主板所支持的內存的工作頻率

2009-12-24 14:58:23 893

893 內存的傳輸類型有哪些? 傳輸類型指內存所采用的內存類型,不同類型的內存傳輸類型各有差異,

2009-12-25 13:37:21 1643

1643 內存傳輸標準有哪些? 內存是計算機內部最

2009-12-25 13:49:07 427

427 內存最高傳輸標準 內存傳輸標準是指主板所支持的內存傳輸帶寬大小或主板所支持的內存的工作頻率,這里的內

2009-12-26 15:56:43 259

259 什么是內存段/DMA

像I/O地址一樣,一些設備在主內存中分配有地址。當你安裝這樣的設備時,實際上也插了一塊內存模塊(主內存

2010-02-05 09:55:43 500

500 DMA_讀取GPIO電平到內存(中斷恢復目的地址)

2016-01-12 18:20:04 4

4 DMA_讀取GPIO電平到內存,單片機程序

2016-01-12 18:19:55 10

10 卡中斷方式傳輸數據的缺陷,介紹了多系統內存分布和數據傳輸協議。理論分析和試驗結果均表明,本協議能夠滿足鐵鳥試驗臺飛機仿真試驗中多系統間實時數據傳輸需求,同時能夠快速診斷各系統異常情況,提高了在仿真試驗中飛機

2017-11-10 10:05:06 11

11 1.DMA概述 DMA是外設與主存之間的一種數據傳輸機制。一般來說,外設與主存之間存在兩種數據傳輸方法:(1)Pragrammed I/O(PIO)方法,也即由CPU通過內存讀寫指令或I/O指令

2017-12-07 19:13:28 267

267 【*】程序簡介 -工程名稱:DMA直接內存存取 -實驗平臺: 秉火STM32 F429 開發板 -MDK版本:5.16 -ST固件庫版本:1.5.1 【 !】功能簡介: 使用DMA把內存數據傳輸

2017-12-13 15:09:52 9

9 手頭項目也需要加入DMA數據傳輸,以最大限度地提升CPU效率,于是測試了一下XMEGA的DMA模塊,把一塊內存中的數據DMA傳輸到另外一塊內存,DMA傳輸完成后,在中斷函數中顯示“DMA Finished”,提示DMA成功完成數據傳輸。

2018-04-27 09:22:00 8633

8633 該裝置將一個通用DMA控制器,系統的DMA(SDMA)控制器,用于內存到內存,內存和外設存儲器傳輸外。

2018-04-13 15:48:54 2

2 DRAM就是我們一般在用的內存,而NAND Flash 閃存,它在做的事情其實是硬盤。

2018-07-17 17:43:39 18789

18789

手機內存到底怎么選?這三種配置最推薦,你選對了嗎?

2019-08-28 17:17:15 9334

9334 內存便宜了,單條16GB插滿內存槽成為可能。64GB大內存該如何利用?很多人想起了古老但又有些陌生的玩法:RAMOS內存操作系統。通過內存模擬硬盤,再將整個Windows系統放入內存中運行。

2020-01-30 12:24:00 21545

21545 我這里也設計了兩輪DMA傳輸,照樣使用TIMER更新事件觸發ADC轉換。第一輪DMA傳輸傳輸3個AD轉換結果到某內存地址,第二輪傳輸5個轉換結果到另一內存位置。

2020-05-14 09:24:11 3278

3278

內存超頻有一定幾率損壞內存。內存超頻涉及到修改內存的電壓、主頻、時序等內容,如果內存體質不佳且修改的范圍超過了內存能夠承受的上限,內存很容易因此而燒壞。即便超頻的內存能夠點亮并且通過壓力測試,但也容易加速內存壽命老化。以下是對內存超頻的詳細說明:

2020-06-15 10:38:44 9092

9092 DMA的總結 ZYNQ中不同應用的DMA 幾個常用的 AXI 接口 IP 的功能(上面已經提到): AXI-DMA:實現從 PS 內存到 PL 高速傳輸高速通道 AXI-HP----AXI-Stream

2020-10-09 18:05:57 6391

6391

1、綜述 DMA(Direct memory access)直接內存訪問,被用于內存和內存之間或內存和外設之間的高速數據傳輸。數據傳輸可以在沒有CPU的干預下快速移動,這樣可以保持CPU資源處理其他

2020-10-27 14:47:50 9655

9655

的測試/演示。 特征 ZNEO CPU 突出的直接內存訪問特性是: 四個獨立的 DMA 通道 支持內存到內存、內存到外設、外設到內存以及外設到外設的數據傳輸。 在直接或鏈表模式下運行 字節

2021-06-21 17:28:25 1347

1347

內存預拷貝遷移在密集型負載下存在內存臟頁反復傳輸的冋題,導致迭代輪數較多且大幅降低了內存預拷貝遷移的整體性能。臟頁概率預測能夠有效減少內存臟頁反復傳輸的現象,然而現有臟頁概率預測硏究都只關注時間

2021-05-24 15:40:58 14

14 DMA(Direct Memory Access),即直接存儲器存取,是一種快速傳送數據的機制。數據傳遞可以從適配卡到內存,從內存到適配卡或從一段內存到另一段內存。利用它進行數據傳送時不需要CPU

2021-10-19 18:33:08 10

10 stm32F1DMA詳解1、問題:什么是DMA?回答:DMA,全稱為:Direct Memory Access,即直接存儲器訪問簡而言之,DMA就是將一個內存里的數據搬運到另一個內存里,此過程無需

2021-11-26 17:51:11 10

10 Stm32之DMA直接內存讀取1.DMA簡介:DMA*(Direct Memory Access controller)*:可用于為CPU減負,可以將內存中的數據與外設中的數據進行搬運(無法進行計算

2021-12-09 15:36:07 10

10 1:DMA(DIRECT MEMORY ACCESS)即直接存儲器存取,是指外部設備不通過CPU而直接與系統內存交換數據的接口技術。 要把外設的數據讀入內存或把內存的數據

2021-12-28 19:22:30 11

11 系統 BIOS 分配寄存器組和反射內存的基址。反射內存的寄存器組的基址和內存地址可以比較隨意,。對于超出了基本的設置,如啟用或禁用中斷或 DMA 周期的操作,用戶必須知道三個寄存器組內具體寄存器分配,本章提供的這些信息。

2022-04-02 16:25:27 455

455 DMA(Direct memory access):直接內存存儲。DMA可以提高外設和內存以及內存到內存直接的傳輸速率,數據能不經過CPU任何的參與快速地移動,這樣可以節省CPU去處理其他事情

2023-02-14 09:42:22 919

919

DMA 通道可以在不被外設請求觸發的情況下運行。這種模式稱為內存到內存模式,由軟件啟動。 它允許在沒有硬件請求的情況下從一個地址位置傳輸到另一個地址位置。配置并啟用通道后,傳輸將立即開始

2023-03-23 15:23:00 1858

1858

電子發燒友網站提供《STM32L4直接訪問內存模塊(DMA)介紹.pdf》資料免費下載

2023-08-01 10:15:55 1

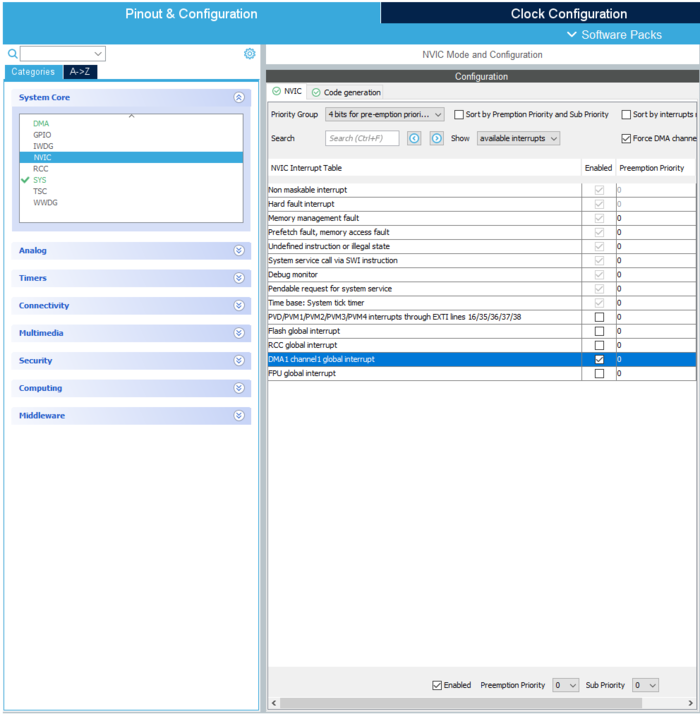

1 隨意選擇ADC1的4個通道,掃描模式,連續轉換,DMA傳輸轉換結果并令DMA工作在外設字到內存字的循環傳輸模式。使用CubeMx進行配置。其中DMA通道使用Channel 1。

2023-07-29 16:19:13 758

758

DMA不產生傳輸完成中斷

2023-10-18 16:44:03 616

616

用戶使用STM32G473RET6芯片,開發環境STM32CubeMX+Keil(LL庫)。使用DMA1通道1,在半傳輸中斷和完全傳輸中斷里,拷貝ADC采集的數據。在應用過程中發現DMA半傳輸中斷和完全傳輸中斷不能獨立使用。

2023-12-01 09:19:48 797

797

電子發燒友App

電子發燒友App

評論