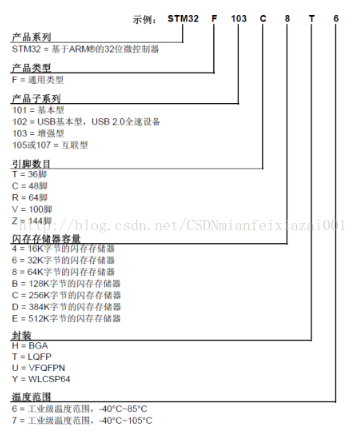

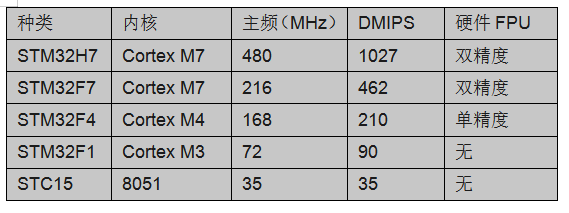

今天打算繼續(xù)總結stm32單片機的基礎知識,鞏固基礎。這里呢,聲明一下,《stm32單片機基礎知識總結》主要基于stm32f1及stm32f4兩個系列來做的。原因是stm32f1系列是Cortex-M3內(nèi)核 ,stm32f4系列是基于Cortex-M4內(nèi)核。我在項目開發(fā)中,主要用到了這兩個系列的片子,所以算是對自己知識的一個鞏固。另外,知識都是相通的。所以如果理解了這兩種架構,那么如果需要的話,我們也能夠快速地去學習其他的系統(tǒng)架構。

一、STM32單片機架構

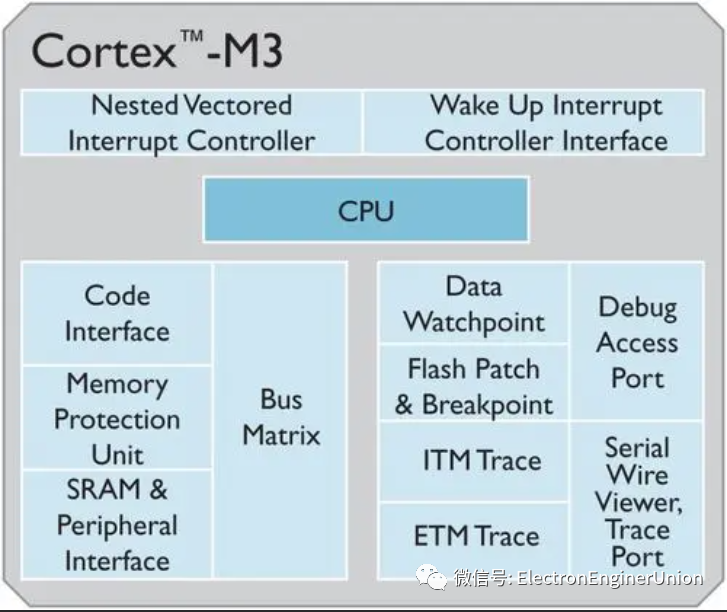

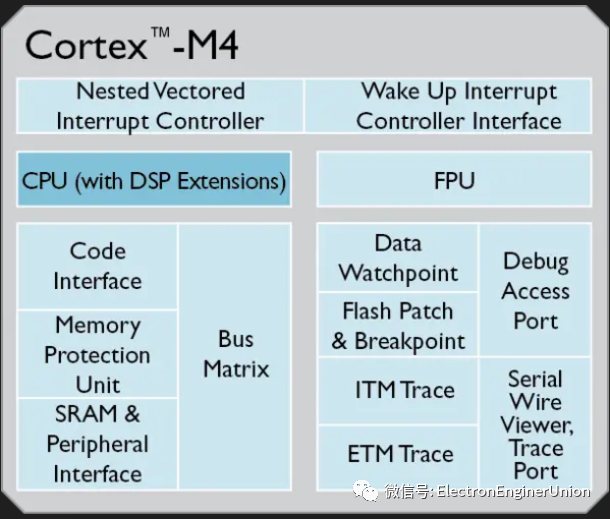

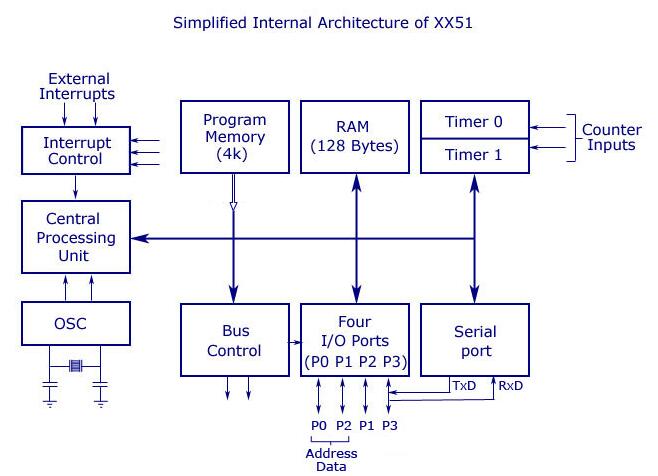

通過兩張圖片來對Cortex-M3 和Cortex-M4兩個內(nèi)核資源進行一個對比。

?

通過對此,我們可以看到有這樣幾個不同之處:

M4具有單精度浮點運算單元,F(xiàn)1沒有浮點運算單元。

M4具備增強的DSP指令集。

然后其他共有的模塊如下:

內(nèi)核系統(tǒng)模塊

nested vectored interrupt controller

嵌套向量中斷控制器

wake up interrupt controller interface

喚醒中斷控制器接口

DSP:數(shù)字信號處理單元,

FPU:浮點運算器

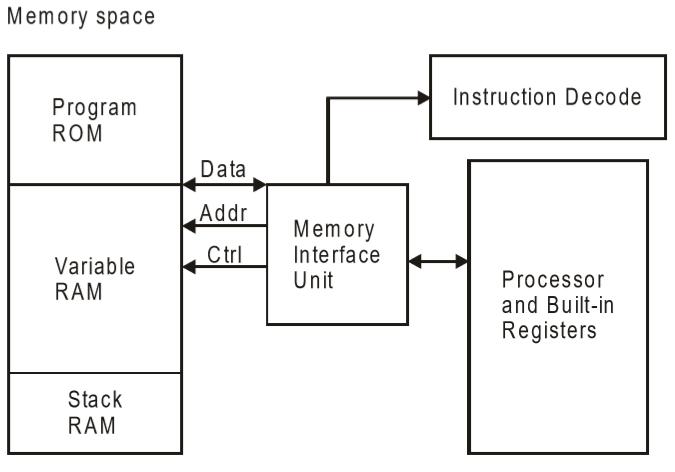

Memory Interface Unit(MPU):存儲器保護單元

它可以實施對存儲器(主要是內(nèi)存和外設寄存器)的保護,以使軟件更加健壯和可靠。在使用前,必須根據(jù)需要對其編程。如果沒有啟用MPU,則等同于系統(tǒng)中沒有配MPU。

MPU有如下的能力可以提高系統(tǒng)的可靠性:

阻止用戶應用程序破壞操作系統(tǒng)使用的數(shù)據(jù)。

阻止一個任務訪問其它任務的數(shù)據(jù)區(qū),從而把任務隔開。

可以把關鍵數(shù)據(jù)區(qū)設置為只讀,從根本上消除了被破壞的可能。

檢測意外的存儲訪問,如,堆棧溢出,數(shù)組越界。

此外,還可以通過MPU設置存儲器regions的其它訪問屬性,比如,是否緩區(qū),是否緩沖等。

SRAM &Peripheral interface:SRAM&外設接口

Bus Matrix:總線矩陣用于多主(Core,DMA等),多從(內(nèi)部RAM,APB,外部總線等)的交聯(lián)和仲裁。目的是為了提高不同主機訪問不同外設情況下的帶寬。

跟蹤調(diào)試系統(tǒng)

Data Watchpoint:

用于實時變量監(jiān)控,可用于定期輸出PC或各種CPU內(nèi)部計數(shù)器,從目標獲取分析信息。

Flash Patch &BreakPoint:轉換及斷電單元

ITM Trace:

指令跟蹤宏單元,一種針對MCU進行跟蹤調(diào)試的新方法,與打斷點(Breakpoint)不同,ITM方法不需要暫停程序運行,可以在程序全速運行的過程中實時輸出變量的數(shù)值以便觀察,即Trace功能

ETM Trace:集成跟蹤選項

Debug Access Port:調(diào)試端口

Serial Wire Viewer ,Trace port :串行線查看器,跟蹤端口

以上把所有的模塊都簡單翻譯了一下,個別的稍加闡述。篇幅原因就不再進行深入了。感興趣的朋友可以網(wǎng)上再查一查資料。我這里當是拋磚引玉了。

針對stm32f1與stm32f4,兩個片子的框架,再進行一個簡單總結。整個這些知識內(nèi)容都是一些基礎的東西,可能很多東西不懂也能夠把代碼寫出來,調(diào)試也能通過。入門的話,也可以了。我個人覺得想走更遠,應該知其然也知其所以然。雖然我水平一般,需要學習實踐的地方有很多。但從多年的工作經(jīng)歷來說,我覺得做到大而廣不難,做到大而廣還要細就是很考驗人的了。

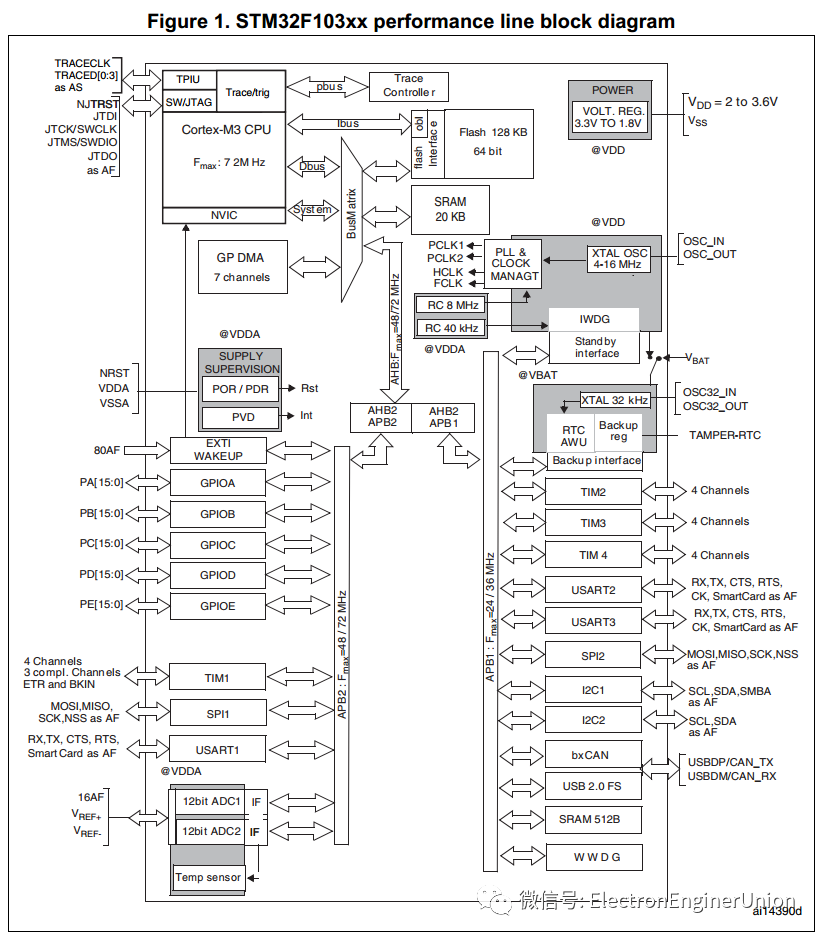

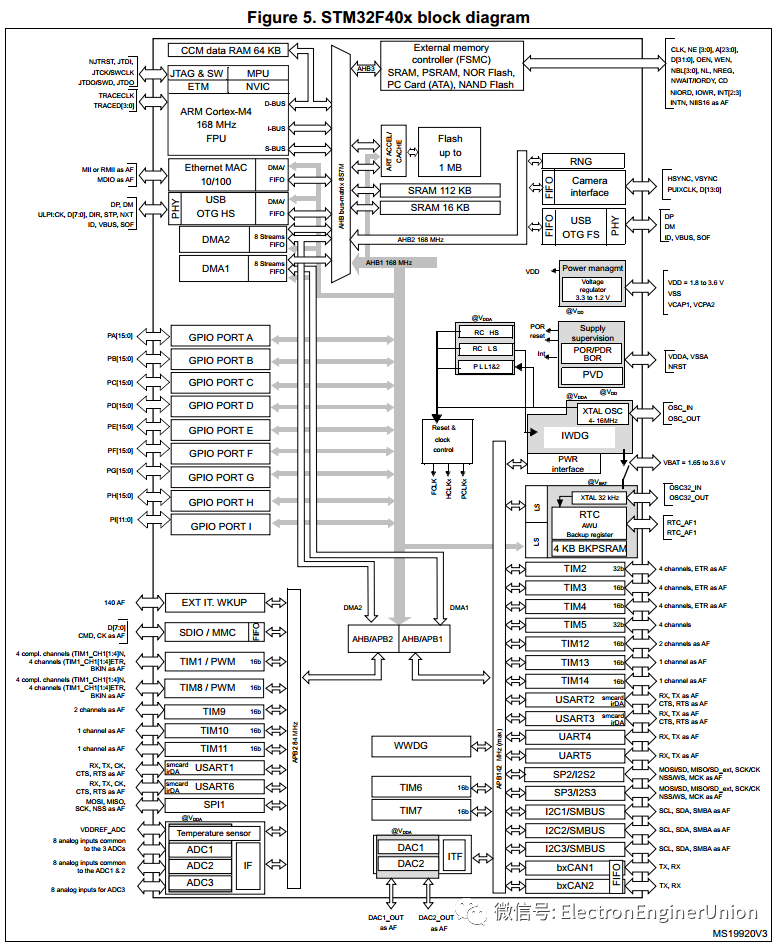

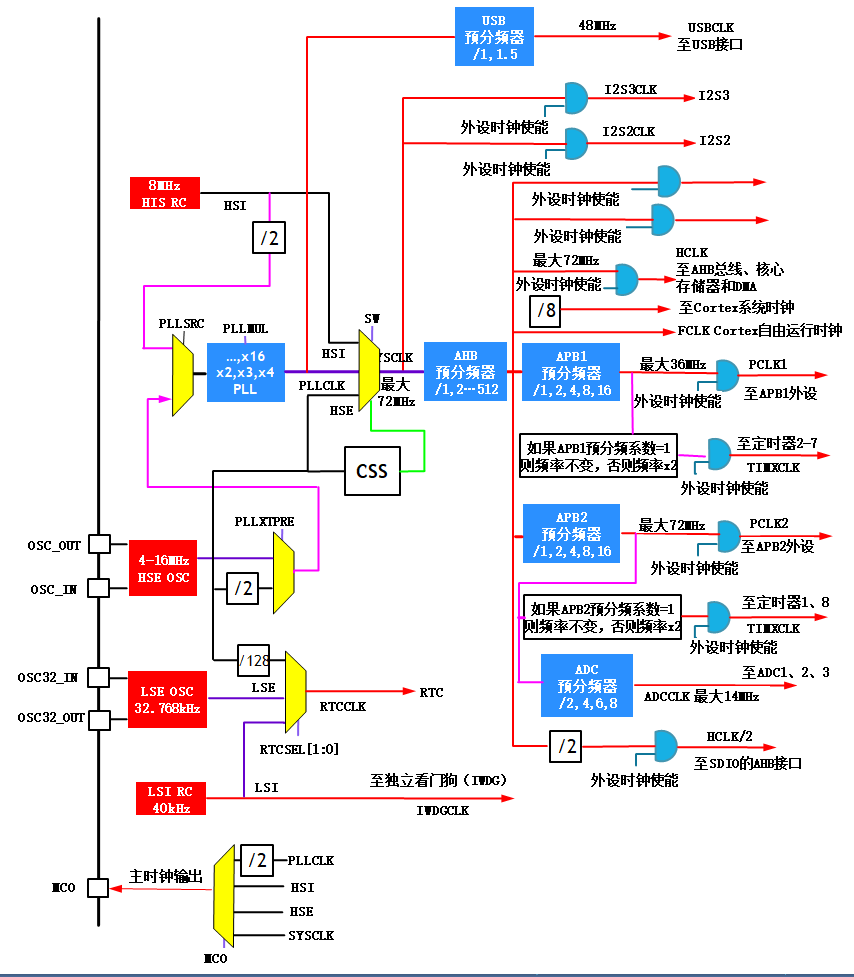

下面兩張Block diagram 是我從ST官方文檔上面截下來的。第一張是STM32f103。第二張是STM32F40x。STM32f103是基于Cortex-M3架構。STM32f40x是基于Cortex-M4架構。很明顯STM32f40x芯片的內(nèi)核所掛載的資源相當于STM32f103芯片所掛載的資源要豐富很多。

stm32f103內(nèi)部架構圖?

stm32f40x架構圖

從上面兩張架構圖中,我們可以讀出很多信息。

1)stm32f1主頻最高是72MHZ.stm32f4主頻最高是168MHZ,且集成了FPU功能。

2)F1內(nèi)部SRAM最大64K字節(jié), F4內(nèi)部SRAM有192K字節(jié)(112K+64K+16K)。

3)四個主動單元 :

M3內(nèi)核的ICode總線(I-bus)、DCode總線(D-bus)、 系統(tǒng)總線(S-bus)、DMA(DMA1、DMA2、以太網(wǎng)DMA)

ICode總線 :

將M3內(nèi)核的指令總線與FLASH指令接口相連,用于指令預取

DCode總線:

將M3內(nèi)核的數(shù)據(jù)總線與FLASH數(shù)據(jù)接口相連,常量加載和調(diào)試

系統(tǒng)總線 :

將M3內(nèi)核的系統(tǒng)總線與總線矩陣相連,協(xié)調(diào)內(nèi)核與DMA訪問

DMA總線:

將DMA的AHB主控接口與總線矩陣相連,協(xié)調(diào)CPU的DCode和DMA到SRAM、閃存、外設的訪問

4)四個被動單元 :

內(nèi)部SRAM、內(nèi)部閃存、FSMC、AHB到APB橋

AHB橋:

AHB(Advanced High performance Bus),高性能總線。主要用于高性能模塊(如CPU、DMA和DSP等)AHB 系統(tǒng)由主模塊、從模塊和基礎結構(Infrastructure)3部分組成,整個AHB總線上的傳輸都由主模塊發(fā)出,由從模塊負責回應。

APB橋:

APB(Advanced Peripheral Bus),片上外設總線。主要用于慢速片上外設與ARM核的通訊。

例如UART、1284等,它的總線架構不像 AHB支持多個主模塊,在APB里面唯一的主模塊就是APB 橋。再往下,APB2負責AD,I/O,高級TIM,串口1;APB1負責DA,USB,SPI,I2C,CAN,串口2345,普通TIM。

cortex-M3、cortex-M4內(nèi)核是由ARM公司提供的。芯片其余外圍是由ST公司設計完成的。

篇幅有限,很多要點的內(nèi)容也需要時間的沉淀。后續(xù)的工作學習中,再對這些知識點做補充優(yōu)化。

電子發(fā)燒友App

電子發(fā)燒友App

評論