01 時(shí)鐘系統(tǒng)

1.1 時(shí)鐘系統(tǒng)的作用

Stm32芯片中有大量的電路模塊,時(shí)鐘系統(tǒng)提供一個(gè)頻率信號(hào)為電路模塊提供統(tǒng)一的節(jié)拍,使電路模塊能有序工作,最終達(dá)到控制電路的目的。

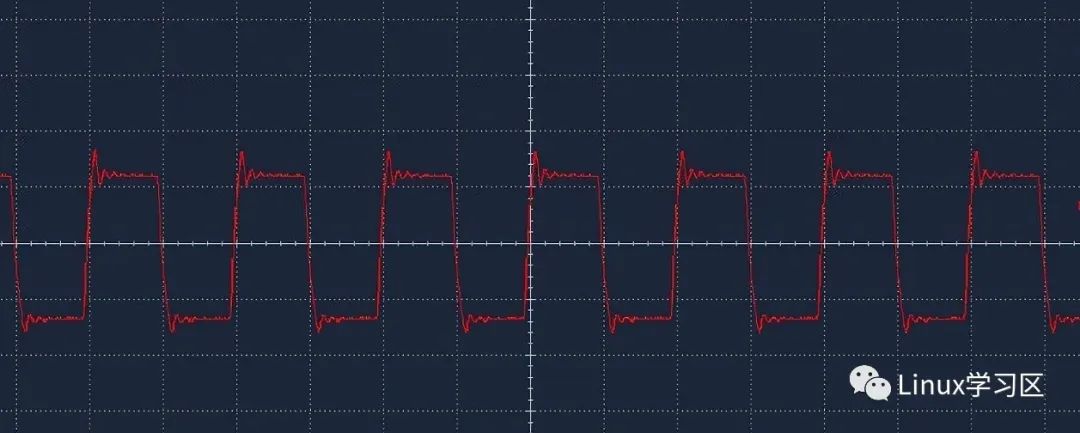

圖1.1 晶振頻率圖

1.2 時(shí)鐘周期的關(guān)系

時(shí)鐘:為Stm32提供統(tǒng)一的節(jié)拍,形象的稱時(shí)鐘是單片機(jī)的心臟。

時(shí)鐘周期:又名振蕩周期,一個(gè)高低電平(0或1)所需要的時(shí)間。

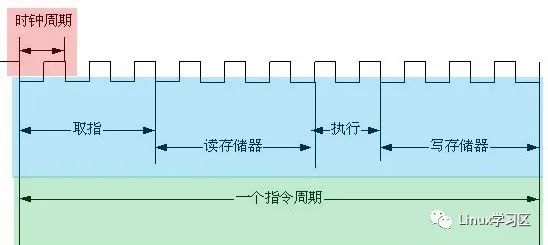

指令周期:CPU從存儲(chǔ)器中取出并執(zhí)行一條指令所需的全部時(shí)間(取指、譯碼與執(zhí)行三部分時(shí)間)。

機(jī)器周期:執(zhí)行一個(gè)動(dòng)作的時(shí)間周期,如取指令、存儲(chǔ)器讀、存儲(chǔ)器寫等,這每一項(xiàng)工作稱為一個(gè)基本操作。完成一個(gè)基本操作所需要的時(shí)間稱為機(jī)器周期。

圖1.2 指令周期圖

02 Stm32的時(shí)鐘源

2.1 Stm32時(shí)鐘樹(shù)

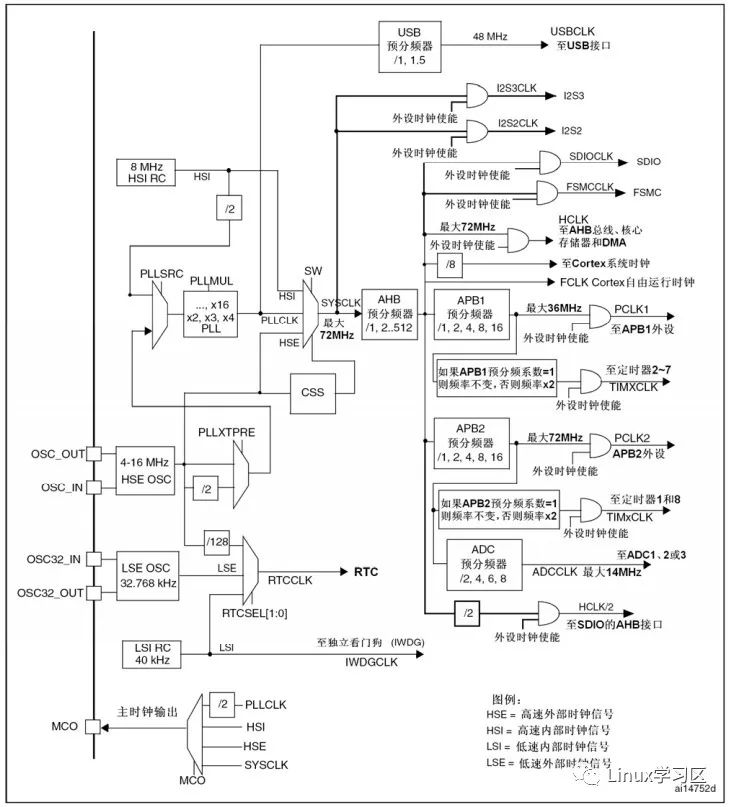

由外部晶體振蕩器提供時(shí)鐘輸入,最終轉(zhuǎn)換為多個(gè)外部設(shè)備的周期性運(yùn)作。這種時(shí)鐘“能量”的傳遞路徑猶如大樹(shù)的養(yǎng)分由主干流向分支,因此稱為時(shí)鐘樹(shù)。理解系統(tǒng)時(shí)鐘的大小如何獲得(分頻與倍頻),其他外設(shè)的時(shí)鐘又如何劃分,可以通過(guò)一張時(shí)鐘樹(shù)圖找到答案,只要理解好時(shí)鐘樹(shù),Stm32一切時(shí)鐘的來(lái)龍去脈就會(huì)非常清楚。

圖2.1 Stm32時(shí)鐘樹(shù)圖

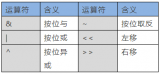

2.2 時(shí)鐘源的分類

Stm32有兩類時(shí)鐘源,一種是以晶振的內(nèi)置與外置來(lái)分別,另一種以時(shí)鐘的速度來(lái)區(qū)分,并由此分為如下四種類型。

圖2.2 時(shí)鐘源分類圖

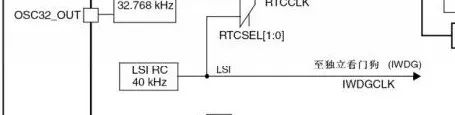

2.2.1 內(nèi)置低速時(shí)鐘LSI

從內(nèi)部RC振蕩器產(chǎn)生,頻率為40khz,也是主要提供給實(shí)時(shí)時(shí)鐘模塊,同時(shí)LSI時(shí)鐘擔(dān)當(dāng)一個(gè)低功耗時(shí)鐘源,為獨(dú)立看門狗和自動(dòng)喚醒單元提供時(shí)鐘,它可以在停機(jī)和待機(jī)模式下保持運(yùn)行。

圖2.3 內(nèi)置低速時(shí)鐘LSI

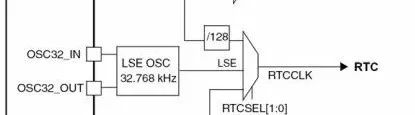

2.2.2 外置低速時(shí)鐘LSE

以低速外部晶振(低速外部石英晶體或陶瓷諧振器)作為時(shí)鐘源,主要是提供給實(shí)時(shí)時(shí)鐘模塊或者為其他定時(shí)功能提供一個(gè)低功耗且精確的時(shí)鐘源(RTC時(shí)鐘源),所以一般選用32.768khz的石英晶振,該頻率下定時(shí)器方便取整。

圖2.4 外置低速時(shí)鐘LSE

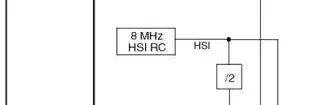

2.2.3 高速內(nèi)部時(shí)鐘HSI

以內(nèi)部RC振蕩器產(chǎn)生,頻率為8Mhz,優(yōu)點(diǎn)是成本低且啟動(dòng)速度快,但相較于外部時(shí)鐘不穩(wěn)定,精度較差。如果HSE晶體振蕩器失效,HSI時(shí)鐘會(huì)被作為備用時(shí)鐘源。

圖2.5 高速內(nèi)部時(shí)鐘HSI

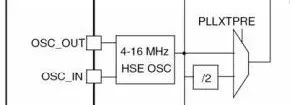

2.2.4 外置高速時(shí)鐘HSE

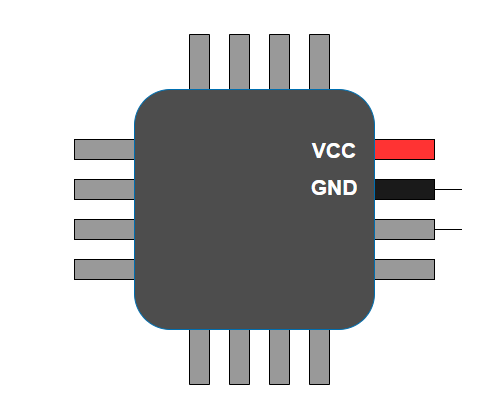

以外部晶振作為時(shí)鐘源,晶振頻率可取范圍為4~16Mhz,一般采用8Mhz的晶振,為系統(tǒng)提供更為精確的主時(shí)鐘。

圖2.6 外置高速時(shí)鐘HSE

03 HSE、HSI和PLL的使能

3.1 系統(tǒng)時(shí)鐘源的使能

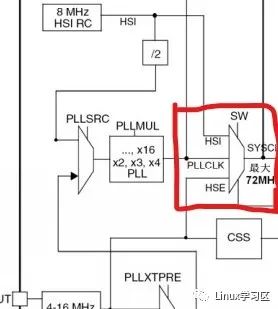

Stm32的時(shí)鐘源主要有: 內(nèi)部時(shí)鐘、外部時(shí)鐘、鎖相環(huán)倍頻輸出時(shí)鐘。內(nèi)部時(shí)鐘、外部時(shí)鐘又分為高速時(shí)鐘、低速時(shí)鐘。系統(tǒng)時(shí)鐘源sysclk的時(shí)鐘由HSE、HSI、PLL三個(gè)時(shí)鐘提供,具體在RCC_CFGR寄存器中配置。

圖3.1 系統(tǒng)時(shí)鐘源的使能

PLL鎖相環(huán)倍頻輸出時(shí)鐘又主PLL時(shí)鐘、PLLI2S時(shí)鐘。PLL時(shí)鐘來(lái)源可以有兩個(gè):一個(gè)是HSE,另一個(gè)是HSI/2。由時(shí)鐘配置寄存器CFGR的位16,即PLLSRC設(shè)置具體用哪個(gè)。HSI是內(nèi)部高速的時(shí)鐘信號(hào),頻率為8MHz,這里我們選擇HSE作為PLL的時(shí)鐘來(lái)源。

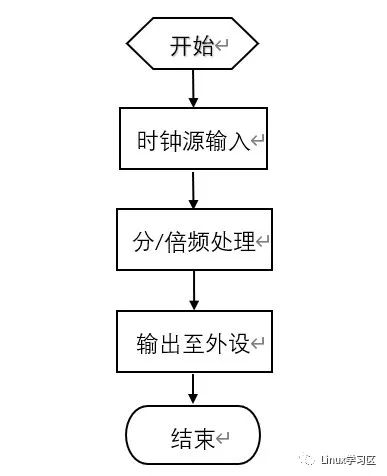

3.2 系統(tǒng)時(shí)鐘的設(shè)置步驟

(1) 開(kāi)機(jī)后,先讓系統(tǒng)啟動(dòng)起來(lái),由于HSI的啟動(dòng)速度快,所以先啟動(dòng)內(nèi)部HSI待系統(tǒng)穩(wěn)定后再切高速時(shí)鐘源。

(2) 系統(tǒng)啟動(dòng)后,切換系統(tǒng)時(shí)鐘的時(shí)鐘源為HSE。切換時(shí)要注意,先關(guān)閉時(shí)鐘相關(guān)的中斷,防止中斷破壞時(shí)鐘源的切換。

(3) 設(shè)置HSE的信號(hào)源,外部晶振不旁路,然后開(kāi)啟HSE,并等待HSE穩(wěn)定;HSE穩(wěn)定后,配置Stm32工作于高性能模式下,配置PWR_CR寄存器。

(4) 配置AHB、APB1和APB2的分頻系數(shù);配置PLL的分頻、倍頻系數(shù),然后開(kāi)啟PLL,等待PLL輸出穩(wěn)定。

(5) 配置指令預(yù)取、指令cache、數(shù)據(jù)cache等使能;選擇主PLL為系統(tǒng)時(shí)鐘,并等待其穩(wěn)定。

04 鎖相環(huán)PLL的內(nèi)部結(jié)構(gòu)

4.1 鎖相環(huán)內(nèi)部結(jié)構(gòu)

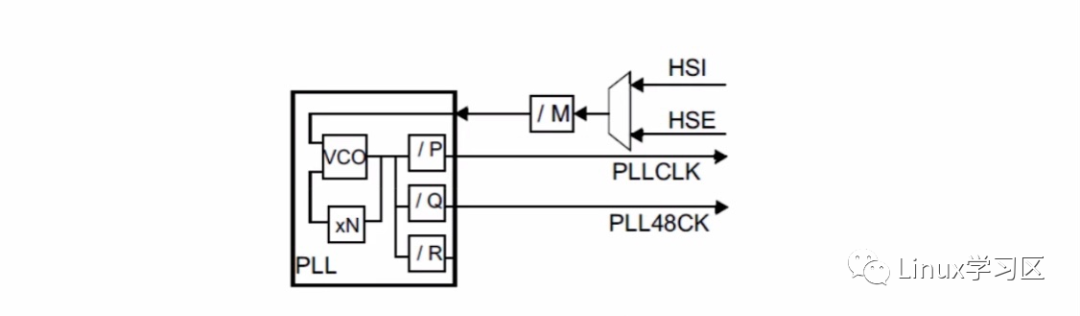

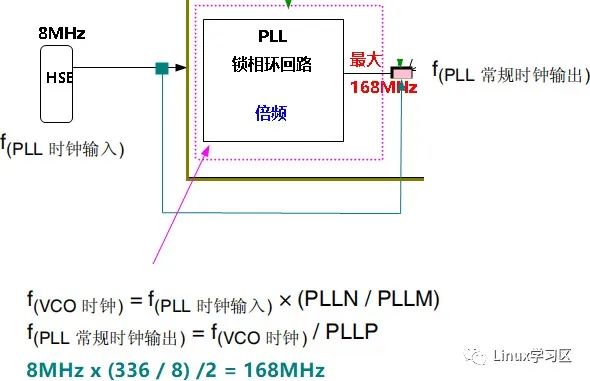

PLL是鎖相環(huán),用于倍頻輸出,因?yàn)殚_(kāi)發(fā)板外部高速晶振也只有8M,如果要使芯片的最大時(shí)鐘頻率是72M,可通過(guò)PLL鎖相環(huán)來(lái)倍頻。它是由HSL或者HSI驅(qū)動(dòng)產(chǎn)生的一個(gè)時(shí)鐘,先經(jīng)過(guò)分頻器M,再經(jīng)過(guò)倍頻器N,再經(jīng)過(guò)分頻器P出來(lái),形成PLL時(shí)鐘源,供給外設(shè)或者系統(tǒng)時(shí)鐘使用的。

圖4.1 PLL的時(shí)鐘結(jié)構(gòu)圖

圖4.2 鎖相環(huán)原理圖

PLL計(jì)算公式 : x=f / m * n / p;

x為PLL頻率,f為輸入時(shí)鐘源(HSL、HSI)時(shí)鐘頻率,m、p為分頻器,n為倍頻器。

05 眾多時(shí)鐘的分配

5.1 時(shí)鐘的分配

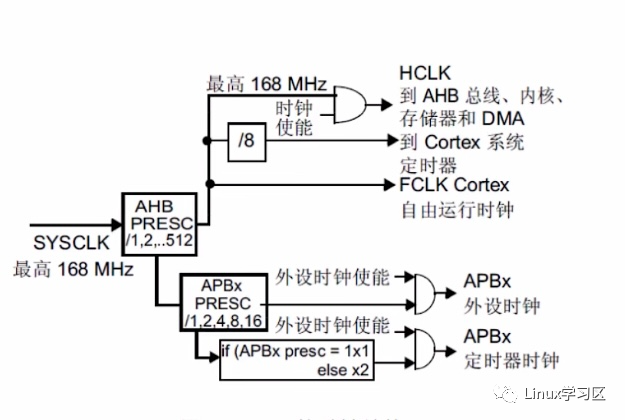

因?yàn)镾tm32的外設(shè)繁多,外設(shè)的運(yùn)作所需要的最佳時(shí)鐘各不相同,如果所有時(shí)鐘同時(shí)運(yùn)行會(huì)給MCU帶來(lái)極大的負(fù)載,所以Stm32采取的時(shí)鐘管理方式是——隨用隨開(kāi)。

圖5.1 時(shí)鐘分配原理圖

(1) 送給AHB總線(Advanced Hight Bus高級(jí)高性能總線)如內(nèi)核、內(nèi)存和DMA使用的HCLK時(shí)鐘。

(2) Systick時(shí)鐘

8分頻后給Stm32的系統(tǒng)定時(shí)器作為時(shí)鐘源。

(3) CPU主頻

給Cortex的自由運(yùn)行時(shí)鐘FCLK,用來(lái)采樣中斷和為調(diào)試模塊計(jì)時(shí)。

(4) 送給APB1(Advanced Peripheral Bus先進(jìn)外設(shè)低速總線)低速預(yù)分頻器APB1。

(5) 送給APB2(Advanced Peripheral Bus先進(jìn)外設(shè)高速總線)高速預(yù)分頻器APB2。

圖5.2 AHB的時(shí)鐘結(jié)構(gòu)

5.2 最終時(shí)鐘外設(shè)分配

最開(kāi)始的節(jié)拍通過(guò)圖5.1的時(shí)鐘流程走下來(lái),經(jīng)歷了一系列的分頻和倍頻,得到了幾個(gè)與我們開(kāi)發(fā)密切相關(guān)的時(shí)鐘。

(1) SYSCLK:系統(tǒng)時(shí)鐘,是Stm32大部分器件的時(shí)鐘來(lái)源,主要由AHB預(yù)分頻器分配到各個(gè)部件。

(2) HCLK:由AHB預(yù)分頻器直接輸出得到,它是高速總線AHB的時(shí)鐘信號(hào),提供給存儲(chǔ)器,DMA及Cortex內(nèi)核,是Cortex內(nèi)核運(yùn)行的時(shí)鐘,CPU主頻就是這個(gè)信號(hào)。

(3) FCLK:由AHB輸出得到,是內(nèi)核的“自由運(yùn)行時(shí)鐘”。“自由”表現(xiàn)在它不來(lái)自時(shí)鐘HCLK。因此在HCLK停止時(shí)FCLK也可以繼續(xù)運(yùn)行,也就是說(shuō),即使CPU休眠了,也能夠采樣到外部中斷和跟蹤休眠事件,低功耗模式下使用。

(4) PCLK1:外設(shè)時(shí)鐘,由APB1分頻得到,最大可為72Mhz,提供給APB1總線上的外設(shè)使用。

(5) PCLK2:外設(shè)時(shí)鐘,由APB2預(yù)分頻輸出得到,最大為72Mhz,提供給APB2總線上的外設(shè)。

06 APB1和APB2總線上掛接的模塊

6 APB1和APB2總線上掛接的模塊

總線是嵌入式系統(tǒng)主機(jī)部件之間傳送信息的公用通道,物理上對(duì)應(yīng)一組組導(dǎo)線(地址總線,數(shù)據(jù)總線,控制總線),CPU、內(nèi)存、輸入輸出、各種外設(shè)之間的比特信息都在這些總線上傳輸,Stm32微處理器的總線有兩類,分別是AHB和APB。

AHB先進(jìn)高性能總線是一種系統(tǒng)總線,主要用于高性能模塊(如CPU、D MA和DSP等)之間的連接。AHB系統(tǒng)由主模塊、從模塊和基礎(chǔ)結(jié)構(gòu)3部分組成,整個(gè)AHB總線上的傳輸都由主模塊發(fā)出,由從模塊回應(yīng)。

APB是先進(jìn)外設(shè)總線,是一種外圍總線,APB主要用于低帶寬的周邊外設(shè)之間的連接,如USART串口、IO、AD/DA等不需要很高的時(shí)鐘頻率的外設(shè),因此功耗就比較低。

07 應(yīng)用場(chǎng)景

7 應(yīng)用場(chǎng)景

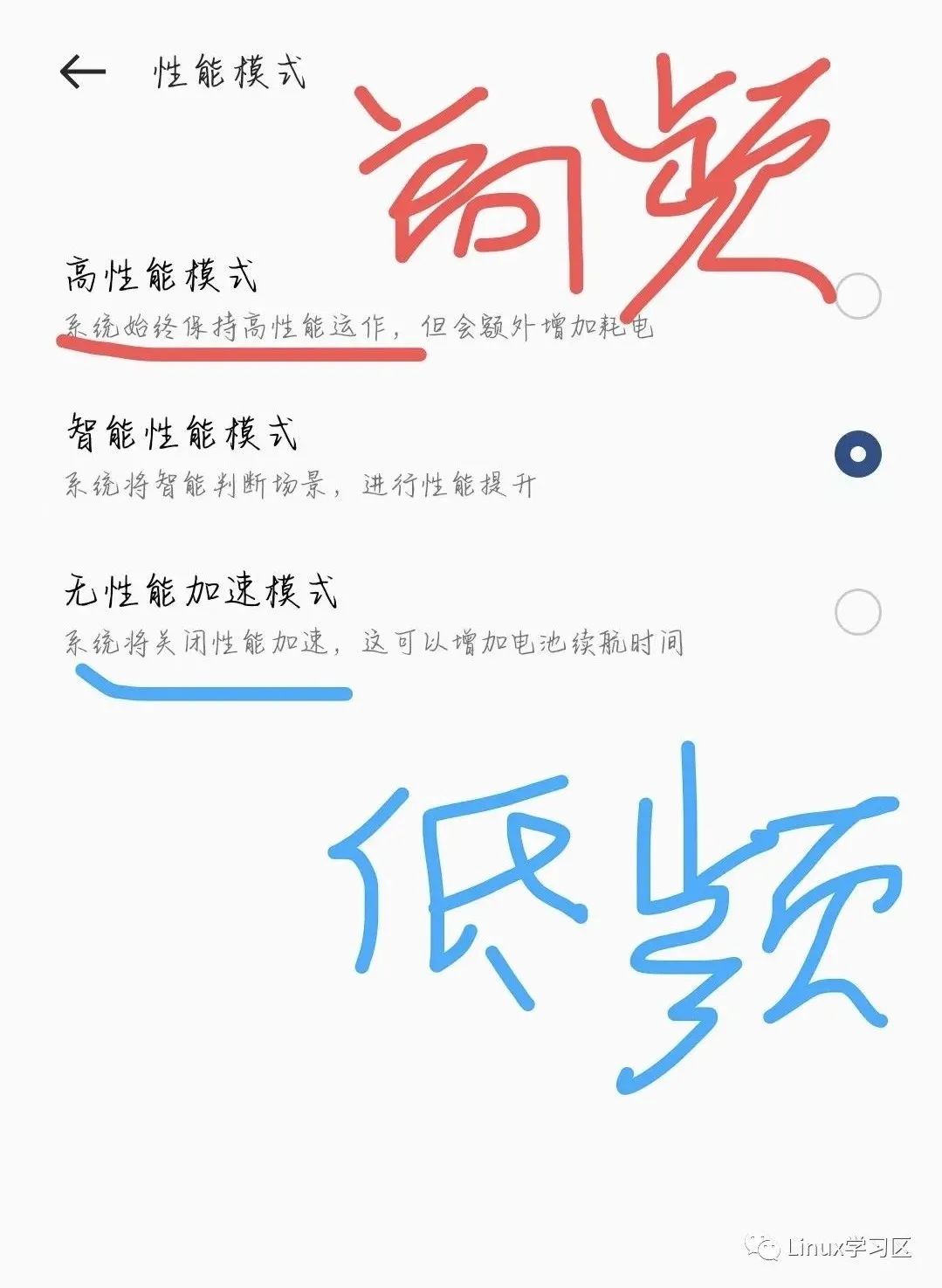

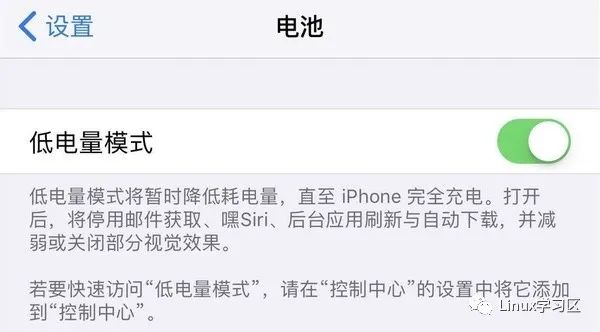

調(diào)節(jié) CPU 的運(yùn)行頻率,來(lái)控制系統(tǒng)的性能與功耗。比較典型的例子就是說(shuō)手機(jī)/筆記本電腦都有高性能模式、平衡模式、低性能模式。

圖7.1 Android的性能模式

圖7.2 Apple的性能模式

08 總結(jié)展望

8 總結(jié)

當(dāng)我們?cè)谀玫揭豢钚碌男酒瑫r(shí),查看它的時(shí)鐘框圖,可以獲取一些信息,為后面的應(yīng)用芯片準(zhǔn)備:

(1) 了解單片機(jī)的時(shí)鐘系統(tǒng)的時(shí)鐘源,及時(shí)鐘頻率為多少

(2) 觀察系統(tǒng)時(shí)鐘Sysclk由哪幾個(gè)時(shí)鐘源驅(qū)動(dòng)

(3) 最后觀察時(shí)鐘樹(shù)圖了解外設(shè)分別掛在哪個(gè)時(shí)鐘線或者時(shí)鐘源上

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論