設計DSP常見的問題集

二.DSP的C語言同主機C語言的主要區別?

1)DSP的C語言是標準的ANSI C,它不包括同外設聯系的擴展部分,如屏幕繪圖等。但在CCS中,為了方便調試,可以將數據通過prinf命令虛擬輸出到主機的屏幕上。

2)DSP的C語言的編譯過程為,C編譯為ASM,再由ASM編譯為OBJ。因此C和ASM的對應關系非常明確,非常便于人工優化。

3)DSP的代碼需要絕對定位;主機的C的代碼有操作系統定位。

4)DSP的C的效率較高,非常適合于嵌入系統。

三.DSP發展動態

1.TMS320C2000 TMS320C2000系列包括C24x和C28x系列。C24x系列建議使用LF24xx系列替代C24x系列,LF24xx系列的價格比C24x便宜,性能高于C24x,而且LF24xxA具有加密功能。 C28x系列主要用于大存儲設備管理,高性能的控制場合。

2.TMS320C3x TMS320C3x系列包括C3x和VC33,主要推薦使用VC33。C3x系列是TI浮點DSP的基礎,不可能停產,但價格不會進一步下調。

3.TMS320C5x TMS320C5x系列已不推薦使用,建議使用C24x或C5000系列替代。

4.TMS320C5000 TMS320C5000系列包括C54x和C55x系列。 其中VC54xx還不斷有新的器件出現,如:TMS320VC5471(DSP+ARM7)。 C55x系列是TI的第三代DSP,功耗為VC54xx的1/6,性能為VC54xx的5倍,是一個正在發展的系列。 C5000系列是目前TI DSP的主流DSP,它涵蓋了從低檔到中高檔的應用領域,目前也是用戶最多的系列。

5.TMS320C6000 TMS320C6000系列包括C62xx、C67xx和C64xx。此系列是TI的高檔DSP系列。 其中C62xx系列是定點的DSP,系列芯片種類較豐富,是主要的應用系列。 C67xx系列是浮點的DSP,用于需要高速浮點處理的領域。 C64xx系列是新發展,性能是C62xx的10倍。

6.OMAP系列 是TI專門用于多媒體領域的芯片,它是C55+ARM9,性能卓越,非常適合于手持設備、Internet終端等多媒體應用。

四.5V/3.3V如何混接?

TI DSP的發展同集成電路的發展一樣,新的DSP都是3.3V的,但目前還有許多外圍電路是5V的,因此在DSP系統中,經常有5V和3.3V的DSP混接問題。在這些系統中,應注意: 1)DSP輸出給5V的電路(如D/A),無需加任何緩沖電路,可以直接連接。 2)DSP輸入5V的信號(如A/D),由于輸入信號的電壓>4V,超過了DSP的電源電壓,DSP的外部信號沒有保護電路,需要加緩沖,如74LVC245等,將5V信號變換成3.3V的信號。 3)仿真器的JTAG口的信號也必須為3.3V,否則有可能損壞DSP。

五.為什么要片內RAM大的DSP效率高?

目前DSP發展的片內存儲器RAM越來越大,要設計高效的DSP系統,就應該選擇片內RAM較大的DSP。片內RAM同片外存儲器相比,有以下優點: 1)片內RAM的速度較快,可以保證DSP無等待運行。 2)對于C2000/C3x/C5000系列,部分片內存儲器可以在一個指令周期內訪問兩次,使得指令可以更加高效。 3)片內RAM運行穩定,不受外部的干擾影響,也不會干擾外部。 4)DSP片內多總線,在訪問片內RAM時,不會影響其它總線的訪問,效率較高。

六.為什么DSP從5V發展成3.3V?

超大規模集成電路的發展從1um,發展到目前的0.1um,芯片的電源電壓也隨之降低,功耗也隨之降低。DSP也同樣從5V發展到目前的3.3V,核心電壓發展到1V。目前主流的DSP的外圍均已發展為3.3V,5V的DSP的價格和功耗都價格,以逐漸被3.3V的DSP取代。

七如何選擇DSP的電源芯片?

TMS320LF24xx:TPS7333QD,5V變3.3V,最大500mA。

TMS320VC33: TPS73HD318PWP,5V變3.3V和1.8V,最大750mA。

TMS320VC54xx:TPS73HD318PWP,5V變3.3V和1.8V,最大750mA; TPS73HD301PWP,5V變3.3V和可調,最大750mA。

TMS320VC55xx:TPS73HD301PWP,5V變3.3V和可調,最大750mA。

TMS320C6000: PT6931,TPS56000,最大3A。

八.軟件等待的如何使用?

DSP的指令周期較快,訪問慢速存儲器或外設時需加入等待。等待分硬件等待和軟件等待,每一個系列的等待不完全相同。

1)對于C2000系列: 硬件等待信號為READY,高電平時不等待。 軟件等待由WSGR寄存器決定,可以加入最多7個等待。其中程序存儲器和數據存儲器及I/O可以分別設置。

2)對于C3x系列: 硬件等待信號為/RDY,低電平是不等待。 軟件等待由總線控制寄存器中的SWW和WTCNY決定,可以加入最多7個等待,但等待是不分段的,除了片內之外全空間有效。

3)對于C5000系列: 硬件等待信號為READY,高電平時不等待。 軟件等待由SWWCR和SWWSR寄存器決定,可以加入最多14個等待。其中程序存儲器、控制程序存儲器和數據存儲器及I/O可以分別設置。

4)對于C6000系列(只限于非同步存儲器或外設): 硬件等待信號為ARDY,高電平時不等待。 軟件等待由外部存儲器接口控制寄存器決定,總線訪問外部存儲器或設備的時序可以設置,可以方便的同異步的存儲器或外設接口。

九.中斷向量為什么要重定位?

為了方便DSP存儲器的配置,一般DSP的中斷向量可以重新定位,即可以通過設置寄存器放在存儲器空間的任何地方。 注意:C2000的中斷向量不能重定位。

十.DSP的最高主頻能從芯片型號中獲得嗎?

TI的DSP最高主頻可以從芯片的型號中獲得,但每一個系列不一定相同。

1)TMS320C2000系列:

TMS320F206-最高主頻20MHz。

TMS320C203/C206-最高主頻40MHz。

TMS320F24x-最高主頻20MHz。

TMS320LF24xx-最高主頻30MHz。

TMS320LF24xxA-最高主頻40MHz。

TMS320LF28xx-最高主頻150MHz。

2)TMS320C3x系列:

TMS320C30:最高主頻25MHz。

TMS320C31PQL80:最高主頻40MHz。

TMS320C32PCM60:最高主頻30MHz。

TMS320VC33PGE150:最高主頻75MHz。

3)TMS320C5000系列:

TMS320VC54xx:最高主頻160MHz。

TMS320VC55xx:最高主頻300MHz。

4)TMS320C6000系列:

TMS320C62xx:最高主頻300MHz。

TMS320C67xx:最高主頻230MHz。

TMS320C64xx:最高主頻720MHz。

十一.DSP可以降頻使用嗎?

可以,DSP的主頻均有一定的工作范圍,因此DSP均可以降頻使用。

十二.如何選擇外部時鐘?

DSP的內部指令周期較高,外部晶振的主頻不夠,因此DSP大多數片內均有PLL。但每個系列不盡相同。

1)TMS320C2000系列:

TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部時鐘可以為5MHz-40MHz。

TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部時鐘可以為2.22MHz-40MHz。

TMS320F241/C242/F243:PLL可以×4,因此外部時鐘為5MHz。 TMS320LF24xx:PLL可以由RC調節,因此外部時鐘為4MHz-20MHz。

TMS320LF24xxA:PLL可以由RC調節,因此外部時鐘為4MHz-20MHz。

2)TMS320C3x系列:

TMS320C3x:沒有PLL,因此外部主頻為工作頻率的2倍。

TMS320VC33:PLL可以÷2,×1,×5,因此外部主頻可以為12MHz-100MHz。

3)TMS320C5000系列:

TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主頻可以為0.625MHz-50MHz。

TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主頻可以為6.25MHz-300MHz。

4)TMS320C6000系列:

TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主頻可以為11.8MHz-300MHz。

TMS320C67xx:PLL可以×1和×4,因此外部主頻可以為12.5MHz-230MHz。

TMS320C64xx:PLL可以×1,×6和×12,因此外部主頻可以為30MHz-720MHz

十三.如何選擇DSP的外部存儲器?

DSP的速度較快,為了保證DSP的運行速度,外部存儲器需要具有一定的速度,否則DSP訪問外部存儲器時需要加入等待周期。

1)對于C2000系列: C2000系列只能同異步的存儲器直接相接。 C2000系列的DSP目前的最高速度為150MHz。建議可以用的存儲器有:

CY7C199-15:32K×8,15ns,5V;

CY7C1021-12:64K×16,15ns,5V; CY7C1021V33-12:64K×16,15ns,3.3V。

2)對于C3x系列: C3x系列只能同異步的存儲器直接相接。 C3x系列的DSP的最高速度,5V的為40MHz,3.3V的為75MHz,為保證DSP無等待運行,分別需要外部存儲器的速度<25ns和<12ns。建議可以用的存儲器有:

ROM: AM29F400-70:256K×16,70ns,5V,加入一個等待;

AM29LV400-55(SST39VF400):256K×16,55ns,3.3V,加入兩個等待(目前沒有更快的Flash)。

SRAM: CY7C199-15:32K×8,15ns,5V;

CY7C1021-15:64K×16,15ns,5V;

CY7C1009-15:128K×8,15ns,5V;

CY7C1049-15:512K×8,15ns,5V;

CY7C1021V33-15:64K×16,15ns,3.3V;

CY7C1009V33-15:128K×8,15ns,3.3V;

CY7C1041V33-15:256k×16,15ns,3.3V。

3)對于C54x系列: C54x系列只能同異步的存儲器直接相接。 C54x系列的DSP的速度為100MHz或160MHz,為保證DSP無等待運行,需要外部存儲器的速度<10ns或<6ns。建議可以用的存儲器有:

ROM: AM29LV400-55(SST39VF400):256K×16,55ns,3.3V,加入5或9個等待(目前沒有更快的Flash)。

SRAM: CY7C1021V33-12:64K×16,12ns,3.3V,加入一個等待;

CY7C1009V33-12:128K×8,12ns,3.3V,加入一個等待。

4)對于C55x和C6000系列: TI的DSP中只有C55x和C6000可以同同步的存儲器相連,同步存儲器可以保證系統的數據交換效率更高。

ROM: AM29LV400-55(SST39VF400):256K×16,55ns,3.3V。

SDRAM: HY57V651620BTC-10S:64M,10ns。

SBSRAM: CY7C1329-133AC,64k×32;

CY7C1339-133AC,128k×32。

FIFO:CY7C42x5V-10ASC,32k/64k×18。

十四.DSP芯片有多大的驅動能力?

DSP的驅動能力較強,可以不加驅動,連接8個以上標準TTL門。

十五.調試TMS320C2000系列的常見問題?

1)單步可以運行,連續運行時總回0地址: Watchdog沒有關,連續運行復位DSP回到0地址。

2)OUT文件不能load到片內flash中: Flash不是RAM,不能用簡單的寫指令寫入,需要專門的程序寫入。CCS和C Source Debugger中的load命令,不能對flash寫入。 OUT文件只能load到片內RAM,或片外RAM中。

3)在flash中如何加入斷點: 在flash中可以用單步調試,也可以用硬件斷點的方法在flash中加入斷點,軟件斷點是不能加在ROM中的。硬件斷點,設置存儲器的地址,當訪問該地址時產生中斷。

4)中斷向量: C2000的中斷向量不可重定位,因此中斷向量必須放在0地址開始的flash內。在調試系統時,代碼放在RAM中,中斷向量也必須放在flash內。

十六.調試TMS320C3x系列的常見問題?

1)TMS320C32的存儲器配置: TMS320C32的程序存儲器可以配置為16位或32位;數據存儲器可以配置為8位、16位或32位。

2)TMS320VC33的PLL控制: TMS320VC33的PLL控制端只能接1.8V,不能接3.3V或5V。

十七.如何調試多片DSP?

對于有MPSD仿真口的DSP(TMS320C30/C31/C32),不能用一套仿真器同時調試,每次只能調試其中的一個DSP; 對于有JTAG仿真口的DSP,可以將JTAG串接在一起,用一套仿真器同時調試多個DSP,每個DSP可以用不同的名字,在不同的窗口中調試。 注意:如果在JTAG和DSP間加入驅動,一定要用快速的門電路,不能使用如LS的慢速門電路。

十八.在DSP系統中為什么要使用CPLD?

DSP的速度較快,要求譯碼的速度也必須較快。利用小規模邏輯器件譯碼的方式,已不能滿足DSP系統的要求。 同時,DSP系統中也經常需要外部快速部件的配合,這些部件往往是專門的電路,有可編程器件實現。 CPLD的時序嚴格,速度較快,可編程性好,非常適合于實現譯碼和專門電路。

十九.DSP系統構成的常用芯片有哪些?

1)電源: TPS73HD3xx,TPS7333,TPS56100,PT64xx...

2)Flash: AM29F400,AM29LV400,SST39VF400...

3)SRAM: CY7C1021,CY7C1009,CY7C1049...

4)FIF CY7C425,CY7C42x5...

5)Dual port: CY7C136,CY7C133,CY7C1342...

6)SBSRAM: CY7C1329,CY7C1339...

7)SDRAM: HY57V651620BTC...

8)CPLD: CY37000系列,CY38000系列,CY39000系列...

9)PCI: PCI2040,CY7C09449...

10)USB: AN21xx,CY7C68xxx...

11)Codec:TLV320AIC23,TLV320AIC10...

12)A/D,D/A:ADS7805,TLV2543...

具體資料見www.ti.com,www.cypress.com

二十.什么是boot loader?

DSP的速度盡快,EPROM或flash的速度較慢,而DSP片內的RAM很快,片外的RAM也較快。為了使DSP充分發揮它的能力,必須將程序代碼放在RAM中運行。為了方便的將代碼從ROM中搬到RAM中,在不帶flash的DSP中,TI在出廠時固化了一段程序,在上電后完成從ROM或外設將代碼搬到用戶指定的RAM中。此段程序稱為"boot loader"。

二十一.TMS320C3x如何boot?

在MC/MP管腳為高時,C3x進入boot狀態。C3x的boot loader在reset時,判斷外部中斷管腳的電平。根據中斷配置決定boot的方式為存儲器加載還是串口加載,其中ROM的地址可以為三個中的一個,ROM可以為8位。

二十二.Boot有問題如何解決?

1)仔細檢查boot的控制字是否正確。

2)仔細檢查外部管腳設置是否正確。

3)仔細檢查hex文件是否轉換正確。

4)用仿真器跟蹤boot過程,分析錯誤原因。

二十三.DSP為什么要初始化?

DSP在RESET后,許多的寄存器的初值一般同用戶的要求不一致,例如:等待寄存器,SP,中斷定位寄存器等,需要通過初始化程序設置為用戶要求的數值。 初始化程序的主要作用: 1)設置寄存器初值。 2)建立中斷向量表。 3)外圍部件初始化。

二十四.DSP有哪些數學庫及其它應用軟件?

TI公司為了方便客戶開發DSP,在它的網站上提供了許多程序的示例和應用程序,如MATH庫,FFT,FIR/IIR等,可以在TI的網頁免費下載。

二十五.如何獲得DSP專用算法?

TI有許多的Third Party可以通過DSP上的多種算法軟件。可以通過TI的網頁搜索你所需的算法,找到通過算法的公司,同相應的公司聯系。注意這些算法都是要付費的。

二十六.eXpressDSP是什么?

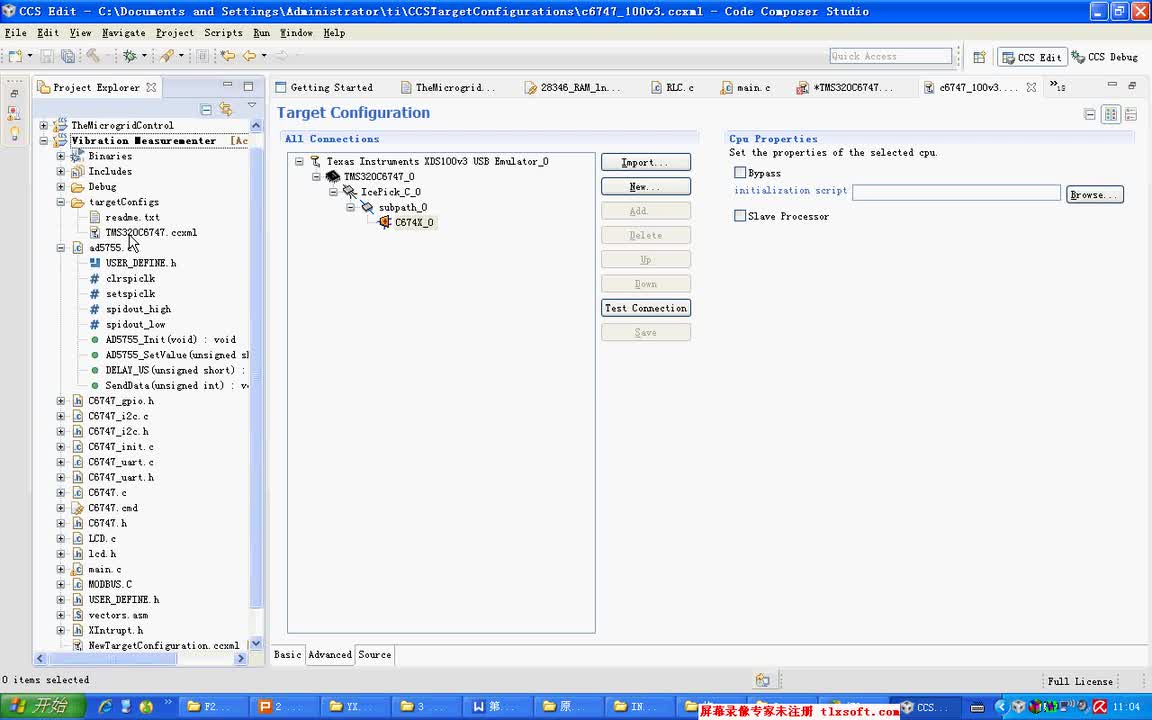

eXpressDSP是一種實時DSP軟件技術,它是一種DSP編程的標準,利用它可以加快你開發DSP軟件的速度。 以往DSP軟件的開發沒有任何標準,不同的人寫的程序一般無法連接在一起。DSP軟件的調試工具也非常不方便。使得DSP軟件的開發往往滯后于硬件的開發。 eXpressDSP集成了CCS(Code Composer Studio)開發平臺,DSP BIOS實時軟件平臺,DSP算法標準和第三方支持四部分。利用該技術,可以使你的軟件調試,軟件進程管理,軟件的互通及算法的獲得,都便的容易。這樣就可以加快你的軟件開發進程。

1)CCS是eXpressDSP的基礎,因此你必須首先擁有CCS軟件。

2)DSP BIOS是eXpressDSP的基本平臺,你必須學會所有DSP BIOS。

3)DSP算法標準可以保證你的程序可以方便的同其它利用eXpressDSP技術的程序連接在一起。同時也保證你的程序的延續性。

二十七.為什么要用DSP?

3G技術和internate的發展,要求處理器的速度越來越高,體積越來越小,DSP的發展正好能滿足這一發展的要求。因為,傳統的其它處理器都有不同的缺陷。MCU的速度較慢;CPU體積較大,功耗較高;嵌入CPU的成本較高。 DSP的發展,使得在許多速度要求較高,算法較復雜的場合,取代MCU或其它處理器,而成本有可能更低。

二十八.如何選擇DSP?

選擇DSP可以根據以下幾方面決定:

1)速度: DSP速度一般用MIPS或FLOPS表示,即百萬次/秒鐘。根據您對處理速度的要求選擇適合的器件。一般選擇處理速度不要過高,速度高的DSP,系統實現也較困難。

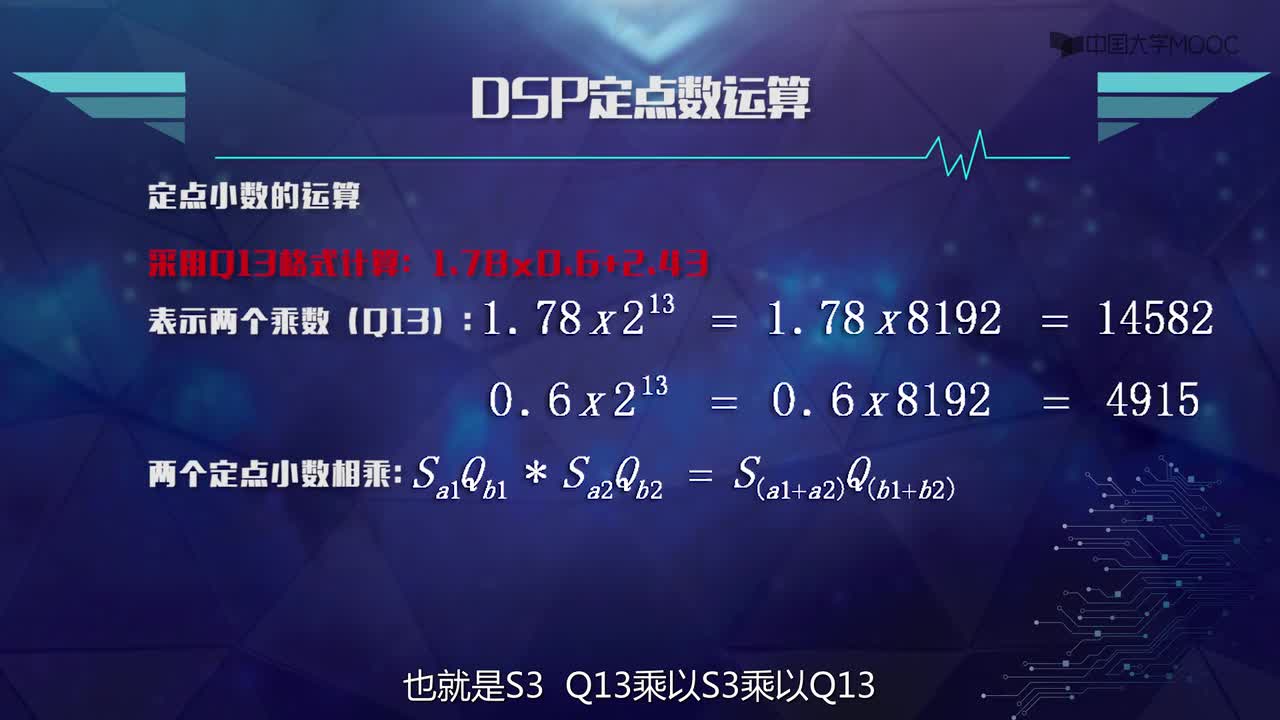

2)精度: DSP芯片分為定點、浮點處理器,對于運算精度要求很高的處理,可選擇浮點處理器。定點處理器也可完成浮點運算,但精度和速度會有影響。

3)尋址空間: 不同系列DSP程序、數據、I/O空間大小不一,與普通MCU不同,DSP在一個指令周期內能完成多個操作,所以DSP的指令效率很高,程序空間一般不會有問題,關鍵是數據空間是否滿足。數據空間的大小可以通過DMA的幫助,借助程序空間擴大。

4)成本: 一般定點DSP的成本會比浮點DSP的要低,速度也較快。要獲得低成本的DSP系統,盡量用定點算法,用定點DSP。

5)實現方便: 浮點DSP的結構實現DSP系統較容易,不用考慮尋址空間的問題,指令對C語言支持的效率也較高。

6)內部部件:根據應用要求,選擇具有特殊部件的DSP。如:C2000適合于電機控制;OMAP適合于多媒體等。

二十九.DSP同MCU相比的特點?

1)DSP的速度比MCU快,主頻較高。

2)DSP適合于數據處理,數據處理的指令效率較高。

3)DSP均為16位以上的處理器,不適合于低檔的場合。

4)DSP可以同時處理的事件較多,系統級成本有可能較低。

5)DSP的靈活性較好,大多數算法都可以軟件實現。

6)DSP的集成度較高,可靠性較好。

三十.DSP同嵌入CPU相比的特點?

1)DSP是單片機,構成系統簡單。 2)DSP的速度快。 3)DSP的成本較低。 4)DSP的性能高,可以處理較多的任務。

三十一.如何編寫C2000片內Flash?

DSP中的Flash的編寫方法有三中:

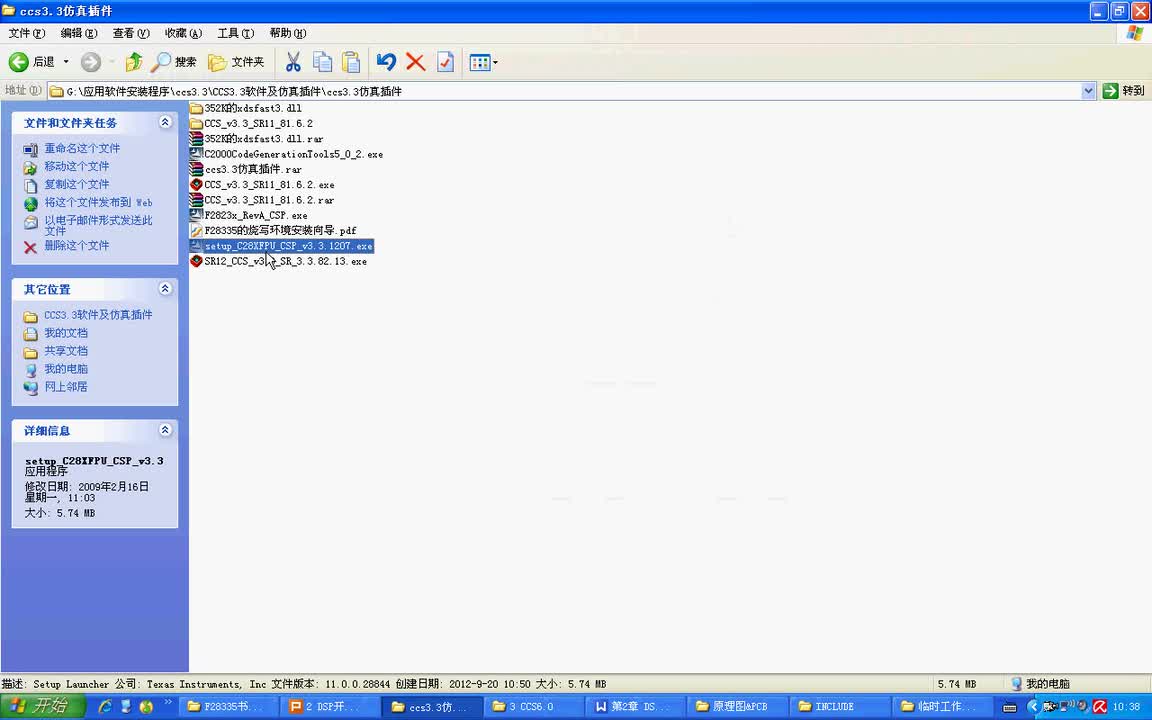

1.通過仿真器編寫:在我們的網頁上有相關的軟件,在銷售仿真器時我們也提供相關軟件。其中LF240x的編寫可以在CCS中加入一個插件,F24x的編寫需要在windows98下的DOS窗中進行。具體步驟見軟件中的readme。有幾點需要注意: a.必須為MC方式; b.F206的工作頻率必須為20MHz; c.F240需要根據PLL修改C240_CFG.I文件。建議外部時鐘為20MHz。 d.LF240x也需要根據PLL修改文件。 d.如果編寫有問題,可以用BFLWx.BAT修復。

2.提供串口編寫:TI的網頁上有相關軟件。注意只能編寫一次,因為編寫程序會破壞串口通信程序。

3.在你的程序中編寫:TI的網頁上有相關資料。

三十二.如何編寫DSP外部的Flash?

DSP的外部Flash編寫方法:

1.通過編程器編寫:將OUT文件通過HEX轉換程序轉換為編程器可以接受的格式,再由編程器編寫。

2.通過DSP軟件編寫:您需要根據Flash的說明,編寫Flash的編寫程序,將應用程序和編寫Flash的程序分別load到RAM中,運行編寫程序編寫。

三十三.對于C5000,大于48K的程序如何BOOT?

對于C5000,片內的BOOT程序在上電后將數據區的內容,搬移到程序區的RAM中,因此FLASH必須在RESET后放在數據區。由于C5000,數據區的空間有限,一次BOOT的程序不能對于48K。解決的方法如下:

1.在RESET后,將FLASH譯碼在數據區,RAM放在程序區,片內BOOT程序將程序BOOT到RAM中。

2.用戶初試化程序發出一個I/O命令(如XF),將FLASH譯碼到程序區的高地址。開放數據區用于其它的RAM。

3.用戶初試化程序中包括第二次BOOT程序(此程序必須用戶自己編寫),將FLASH中沒有BOOT的其它代碼搬移到RAM中。

4.開始運行用戶處理程序。

三十四.DSP外接存儲器的控制方式

對于一般的存儲器具有RD、WR和CS等控制信號,許多DSP(C3x、C5000)都沒有控制信號直接連接存儲器,一般采用的方式如下:

1.CS有地址線和PS、DS或STRB譯碼產生;

2./RD=/STRB+/R/W; 3./WR=/STRB+R/W。

三十五.GEL文件的功能?

GEL文件的功能同emuinit.cmd的功能基本相同,用于初始化DSP。但它的功能比emuinit的功能有所增強,GEL在CCS下有一個菜單,可以根據DSP的對象不同,設置不同的初始化程序。以TMS320LF2407為例:

#define SCSR1 0x7018 ;定義scsr1寄存器

#define SCSR2 0X7019 ;定義scsr2寄存器

#define WDKEY 0x7025 ;定義wdkey寄存器

#define WDNTR 0x7029 ;定義wdntr寄存器

StartUp() ; 開始函數

{

GEL_MapReset(); ; 存儲空間復位 GEL_MapAdd(0x0000,0,0x7fff,1,1); 定義程序空間從0000-7fff 可讀寫

GEL_MapAdd(0x8000,0,0x7000,1,1); 定義程序空間從8000-f000 可讀寫

GEL_MapAdd(0x0000,1,0x10000,1,1); 定義數據空間從0000-10000可讀寫

GEL_MapAdd(0xffff,2,1,1,1); 定義i/o 空間0xffff可讀寫

GEL_MapOn(); 存儲空間打開

GEL_MemoryFill(0xffff,2,1,0x40); 在i/o空間添入數值40h

*(int *)SCSR1=0x0200; 給scsr1寄存器賦值

*(int *)SCSR2=0x000C; 給scsr2寄存器賦值,在這里可以進行mp/mc方式的轉換

*(int *)WDNTR=0x006f; 給wdntr寄存器賦值

*(int *)WDKEY=0x055; 給wdkey寄存器賦值

*(int *)WDKEY=0x0AA; 給wdkey寄存器賦值

}

三十六.使用TI公司模擬器件與DSP結合使用的好處。

1)在使用TI公司的DSP的同時,使用TI公司的模擬可以和DSP進行無縫連接。器件與器件之間不需要任何的連接或轉接器件。這樣即減少了板卡的尺寸,也降低了開發難度。

2)同為TI公司的產品,很多器件可以固定搭配使用。少了器件選型的煩惱

3)TI在CCS中提供插件,可以用于DSP和模擬器件的開發,非常方便。

三十七.C語言中可以嵌套匯編語言?

可以。在ANSI C標準中的標準用法就是用C語言編寫主程序,用匯編語言編寫子程序,中斷服務程序,一些算法,然后用C語言調用這些匯編程序,這樣效率會相對比較高

三十八.在定點DSP系統中可否實現浮點運算?

當然可以,因為DSP都可以用C,只要是可以使用c語言的場合都可以實現浮點運算。

三十九.JTAG頭的使用會遇到哪些情況?

1)DSP的CLKOUT沒有輸出,工作不正常。

2)Emu0,Emu1需要上拉。

3)TCK的頻率應該為10M。

4)在3.3V DSP中,PD腳為3.3V 供電,但是仿真器上需要5V電壓供電,所以PP仿真器盒上需要單獨供電。

4)仿真多片DSP。在使用菊花鏈的時候,第一片DSP的TDO接到第二片DSP的TDI即可。注意當串聯DSP比較多的時候,信號線要適當的增加驅動。

四十.include頭文件(.h)的主要作用

頭文件,一般用于定義程序中的函數、參數、變量和一些宏單元,同庫函數配合使用。因此,在使用庫時,必須用相應的頭文件說明。

四十一.DSP中斷向量的位置

1)2000系列dsp的中斷向量只能從0000H處開始。所以在我們調試程序的時候,要把DSP選擇為MP(微處理器方式),把片內的Flash屏蔽掉,免去每次更改程序都要重新燒寫Flash工作。

2)3x系列dsp的中斷向量也只能在固定的地址。

3)5000,6000系列dsp的中斷向量可以重新定位。但是它只能被重新定位到Page0范圍內的任何空間。

四十二.有源晶振與晶體的區別,應用范圍及用法

1)晶體需要用DSP片內的振蕩器,在datasheet上有建議的連接方法。晶體沒有電壓的問題,可以適應于任何DSP,建議用晶體。

2)有源晶振不需要DSP的內部振蕩器,信號比較穩定。有源晶振用法:一腳懸空,二腳接地,三腳接輸出,四腳接電壓。

四十三.程序經常跑飛的原因

1)程序沒有結尾或不是循環的程序。

2)nmi管腳沒有上拉。

3)在看門狗動作的時候程序會經常跑飛。

4)程序編制不當也會引起程序跑飛。

5)硬件系統有問題。

四十四.并行FLASH引導的一點經驗

最近BBS上關于FLASH和BOOT的討論很活躍,我也多次來此請教。前幾天自制的DSP板引導成功,早就打算寫寫這方面的東西。我用的DSP是5416,以其為核心,做了一個相對獨立的子系統(硬件、軟件、算法),目前都已基本做好。 下面把在FLASH引導方面做的工作向大家匯報一下,希望能對大家有所幫助。本人經驗和文筆都有限,寫的不好請大家諒解。

硬件環境:

DSP:TMS320VC5416PGE160

FLASH:SST39VF400A-70-4C-EK 都是貼片的,FLASH映射在DSP數據空間的0x8000-0xFFFF

軟件環境: CCS v2.12.01

主程序(要燒入FLASH的程序): DEBUG版,程序占用空間0x28000-0x2FFFF(片內SARAM),中斷向量表在0x0080-0x00FF(片內DARAM),數據空間使用0x0100-0x7FFF(片內DARAM)。 因為FLASH是貼片的,所以需要自己編一個數據搬移程序,把要主程序搬移到FLASH中。在寫入FLASH數據時,還應寫入引導表的格式數據。最后在數據空間的0xFFFF處寫入引導表的起始地址(這里為0x8000)。

搬移程序: DEBUG版,程序空間0x38000-0x3FFFF(片內SARAM),中斷向量表在0x7800-0x78FF(片內DARAM),數據空間使用0x5000-0x77FF(片內DARAM)。 搬移程序不能使用與主程序的程序空間和中斷向量表重合的物理空間,以免覆蓋。 燒寫時,同時打開主程序和搬移程序的PROJECT,先LOAD主程序,再LOAD搬移程序,然后執行搬移程序,燒寫OK! 附:搬移程序(僅供參考)

volatile unsigned int *pTemp=(unsigned int *)0x7e00; unsigned int iFlashAddr;

int iLoop; /* 在引導表頭存放并行引導關鍵字 */

iFlashAddr=0x8000;

WriteFlash(iFlashAddr,0x10aa);

iFlashAddr++; /* 初始化SWWSR值 */

WriteFlash(iFlashAddr,0x7e00);

iFlashAddr++; /* 初始化BSCR值 */

WriteFlash(iFlashAddr,0x8006);

iFlashAddr++; /* 程序執行的入口地址 */

WriteFlash(iFlashAddr,0x0002);

iFlashAddr++;

WriteFlash(iFlashAddr,0x8085);

iFlashAddr++; /* 程序長度 */

WriteFlash(iFlashAddr,0x7f00);

iFlashAddr++; /* 程序要裝載到的地址 */

WriteFlash(iFlashAddr,0x0002);

iFlashAddr++;

WriteFlash(iFlashAddr,0x8000);

iFlashAddr++;

for (iLoop=0;iLoop<0x7f00;iLoop++)

{ /* 從程序空間讀數據,放到暫存單元 */

asm(" pshm al");

asm(" pshm ah");

asm(" rsbx cpl");

asm(" ld #00fch,dp");

asm(" stm #0000h, ah");

asm(" MVDM _iLoop, al");

asm(" add #2800h,4,a");

asm(" reada 0h");

asm(" popm ah");

asm(" popm al");

asm(" ssbx cpl"); /* 把暫存單元內容寫入FLASH */

WriteFlash(iFlashAddr,*pTemp);

iFlashAddr++; } /* 中斷向量表長度 */

WriteFlash(iFlashAddr,0x0080);

iFlashAddr++; /* 中斷向量表裝載地址 */

WriteFlash(iFlashAddr,0x0000);

iFlashAddr++;

WriteFlash(iFlashAddr,0x0080);

iFlashAddr++;

for (iLoop=0;iLoop<0x0080;iLoop++) { /* 從程序空間讀數據,放到暫存單元 */

asm(" pshm al");

asm(" pshm ah");

asm(" rsbx cpl");

asm(" ld #00fch,dp");

asm(" stm #0000h, ah");

asm(" MVDM _iLoop, al");

asm(" add #0080h,0,a");

asm(" reada 0h");

asm(" popm ah");

asm(" popm al");

asm(" ssbx cpl"); /* 把暫存單元內容寫入FLASH */

WriteFlash(iFlashAddr,*pTemp);

iFlashAddr++;

} /* 寫入引導表結束標志 */

WriteFlash(iFlashAddr,0x0000);

iFlashAddr++;

WriteFlash(iFlashAddr,0x0000); /* 在數據空間的0xFFFF寫入引導表起始地址 */

iFlashAddr=0xffff;

WriteFlash(iFlashAddr,0x8000);

四十五.關于LF2407A的FLASH燒寫問題的幾點說明

TI現在關于LF24x寫入FLASH的工具最新為c2000flashprogsw_v112。可以支持LF2407、LF2407a、LF2401及相關的LF240x系列。建議使用此版本。在http://focus.ti.com/docs/tool/toolf...燦寫松招闖絳頡?/a> 在使用這個工具時注意:

一,先解壓,再執行setup.exe。

二、進入cc中,在tools圖標下有燒寫工具;

1、關于FLASH時鐘的選擇,此燒寫工具默認最高頻率進行FLASH的操作。根據目標系統的工作主頻重新要進行PLL設置。方法:先在advance options下面的View Config file中修改倍頻。存盤后,在相應的目錄下(tic2xx\\algos\\相應目錄)運行buildall.bat就可以完成修改了。再進行相應的操作即可。

2、若是你所選的頻率不是最高頻率,還需要設定你自已的timings.xx來代替系統默認的最高頻率的timings.xx。例如LF2407a的默認文件是timings.40。Timings.xx可以利用include\\timings.xls的excel工作表來生成。然后在advance options下面的View Config file中修改相應的位置。存盤后,在相應的目錄下運行buildall.bat就可以完成修改了。

3、對于TMS320LF240XA系列,還要注意:由于這些DSP的FLASH具有加密功能,加密地址為程序空間的0x40-0X43H,程序禁止寫入此空間,如果寫了,此空間的數據被認為是加密位,斷電后進入保護FLASH狀態,使FLASH不可重新操作,從而使DSP報廢,燒寫完畢后一定要進行Program passwords的操作,如果不做加密操作就默認最后一次寫入加密位的數據作為密碼。

4、2407A不能用DOS下的燒寫軟件燒寫,必須用c2000flashprogsw_v112軟件燒寫;

5、建議如下:

1)、一般調試時,在RAM中進行;

2)、程序燒寫時,避開程序空間0x40-0x43H加密區,程序最好小于32k;

3)、每次程序燒寫完后,將word0,word1,word2,word3分別輸入自己的密碼,再點擊 Program password,如果加密成功,提示Program is arrayed,如果0x40-0x43h中寫入的是ffff,認為處于調試狀態,flash不會加密;

4)、斷電后,下次重新燒寫時需要往word0~word3輸入已設的密碼,再unlock,成功后可以重新燒寫了;

6、VCPP管腳接在+5V上,是應直接接的,中間不要加電阻。

7、具體事宜請閱讀相應目錄下的readme1,readme2幫助文件。

8.注意*.cmd文件的編寫時應該避開40-43H單元,好多客戶由于沒有注意到這里而把FALSH加密。

四十六.如何設置硬件斷點?

在profiler ->profile point -> break point

四十七.c54x的外部中斷是電平響應還是沿響應?

是沿響應,準確的說,它要檢測到100(一個clk的高和兩個clk的低)的變化才可以。

四十八。參考程序,里面好象都要 disable wachdog,不知道為什么?

watchdog是一個計數器,溢出時會復位你的DSP,不disable的話,你的系統會動不動就reset。

四十九。DSP系統設計100問

一、時鐘和電源

問:DSP的電源設計和時鐘設計應該特別注意哪些方面?外接晶振選用有源的好還是無源的好?

答:時鐘一般使用晶體,電源可用TI的配套電源。外接晶振用無源的好。

問:TMS320LF2407的A/D轉換精度保證措施。

答:參考電源和模擬電源要求干凈。

問:系統調試時發現紋波太大,主要是哪方面的問題?

答:如果是電源紋波大,加大電容濾波。

問:請問我用5V供電的有源晶振為DSP提供時鐘,是否可以將其用兩個電阻進行分壓后再接到DSP的時鐘輸入端,這樣做的話,時鐘工作是否穩定?

答:這樣做不好,建議使用晶體。

問:一個多DSP電路板的時鐘,如何選擇比較好?DSP電路板的硬件設計和系統調試時的時序問題?

答:建議使用時鐘芯片,以保證同步。硬件設計要根據DSP芯片的時序,選擇外圍芯片,根據時序設定等待和硬件邏輯。

二.干擾與板的布局

問:器件布局應重點考慮哪些因素?例如在集中抄表系統中?

答:可用TMS320VC5402,成本不是很高。器件布局重點應是存貯器與DSP的接口。

問:在設計DSP的PCB板時應注意哪些問題?

答:1.電源的布置;2.時鐘的布置;3.電容的布置;4.終端電路;5.數字同模擬的布置。

問:請問DSP在與前向通道(比如說AD)接口的時候,布線過程中要注意哪些問題,以保證AD采樣的穩定性?

答:模擬地和數字地分開,但在一點接地。

問:DSP主板設計的一般步驟是什么?需要特別注意的問題有哪些?

答:1.選擇芯片;2.設計時序;3.設計PCB。最重要的是時序和布線。

問:在硬件設計階段如何消除信號干擾(包括模擬信號及高頻信號)?應該從那些方面著

手?

答:1.模擬和數字分開;2.多層板;3.電容濾波。

問:在電路板的設計上,如何很好的解決靜電干擾問題。

答:一般情況下,機殼接大地,即能滿足要求。特殊情況下,電源輸入、數字量輸入串接

專用的防靜電器件。

問:DSP板的電磁兼容(EMC)設計應特別注意哪些問題?

答:正確處理電源、地平面,高速的、關鍵的信號在源端串接端接電阻,避免信號反射。

問:用電感來隔離模擬電源和數字電源,其電感量如何決定?是由供電電流或噪音要求來

決定嗎?有沒有計算公式?

答:電感或磁珠相當于一個低通濾波器,直流電源可以通過,而高頻噪聲被濾除。所以電

感的選擇主要決定于電源中高頻噪聲的成分。

問:講座上的材料多是電源干擾問題,能否介紹板上高頻信號布局(Layout)時要注意的

問題以及數字信號對模擬信號的影響問題?

答:數字信號對模擬信號的干擾主要是串擾,在布局時模擬器件應盡量遠離高速數字器件,高速數字信號盡量遠離模擬部分,并且應保證它們不穿越模擬地平面。

問:能否介紹PCB布線對模擬信號失真和串音的影響,如何降低和克服?

答:有2個方面,1. 模擬信號與模擬信號之間的干擾:布線時模擬信號盡量走粗一些,如果有條件,2個模擬信號之間用地線間隔。2. 數字信號對模擬信號的干擾:數字信號盡量遠離模擬信號,數字信號不能穿越模擬地。

三.DSP性能

問:1.我要設計生物圖像處理系統,選用那種型號較好(高性能和低價格)?2.如果選定

TI DSP,需要什么開發工具?

答:1.你可采用C54x 或 C55x平臺,如果你需要更高性能的,可采用C6x系列。2.需要EVM

s和XDS510仿真器。

問:請介紹一種專門用于快速富利葉變換(FFT), 數字濾波,卷積,相關等算法的DSP,

最好集成12bit以上的ADC功能。

答:如果你的系統是馬達/能量控制的,我建議你用TMS320LF240x。

問:有些資料說DSP比單片機好,但單片機用的比DSP廣。請問這兩個在使用上有何區別?

答:單片機一般用于要求低的場合,如4/8位的單片機。DSP適合于要求較高的場合。

問:我想了解在信號處理方面DSP比FPGA的優點。

答:DSP是通用的信號處理器,用軟件實現數據處理;FPGA用硬件實現數據處理。DSP的成本便宜,算法靈活,功能強;FPGA的實時性好,成本較高。

問:請問減小電路功耗的主要途徑有哪些?

答:1.選擇低功耗的芯片;2.減少芯片的數量;3.盡量使用IDLE。

問:用C55設計一個低功耗圖像壓縮/解壓和無線傳輸的產品,同時雙向傳輸遙控指令和其

他信息,要求圖像30幀/秒,TFT顯示320*240,不知道能否實現?若能,怎樣確定性能?選擇周邊元器件?確定最小的傳輸速率?能否提供開發的解決方案?軟件核?

答:1.有可能,要看你的算法。2.建議先在模擬器上模擬。

問:用DSP開發MP3,比較專用MP3解碼芯片如何,比如成本、難度、周期?謝謝。

答:1.DSP的功能強,可以實現附加的功能,如ebook等;2.DSP的性能價格比高;3.難度較大,需要算法,因此周期較長,但TI有現成的方案。

問:用DSP開發的系統跟用普通單片機開發的系統相比,有何優勢?DSP一般適用于開發什么樣的系統?其開發周期、資金投入、開發成本如何?與DSP的接口電路是否還得用專門的芯片?

答:1.性能高;2.適合于速度要求高的場合;3.開發周期一般6個月,投入一般要一萬元左

右;4.不一定,但需要速度較高的芯片。

問:DSP會對原來的模擬電路產生什么樣的影響?

答:一方面DSP用數字處理的方法可以代替原來用模擬電路實現的一些功能;另一方面,DSP的高速性對模擬電路產生較大的干擾,設計時應盡量使DSP遠離模擬電路部分。

問:請問支持MPEG-4芯片型號是什么?

答:C55x或 C6000 或DSC2x

問:DSP內的計算速度是快的,但是它的I/O口的交換速度有多快呢?

答:主頻的1/4左右。

四.技術性問題

問:我有二個關于C2000的問題:1、C240或C2407的RS復位引腳既可輸入,也可輸出,直接用CMOS門電路(如74ACT04)驅動是否合適,還是應該用OC門(集電極開路)驅動?2、大程序有時運行異常,但加一兩條空指令就正常,是何原因?

答:1、OC門(集電極開路)驅動。2、是流水線的問題。

問:1.DSP芯片內是否有單個的隨機函數指令?2.DSP內的計算速度是快的,但是它的I/O

口的交換速度有多快呢?SP如何配合EPLD或FPGA工作呢?

答:1.沒有。2.取決于你所用的I/O。對于HPI,傳輸速率(字節)大約為CPU的1/4,對McBSP,位速率(kbps)大約為CPU的1/2。3.你可以級聯仿真接口和一個EPLD/FPGA在一起。

問:設計DSP系統時,我用C6000系列。DSP引腳的要上拉,或者下拉的原則是怎樣的?我經常在設計時為某一管腳是否要設置上/下拉電阻而猶豫不定。

答:C6000系列的輸入引腳內部一般都有弱的上拉或者下拉電阻,一般不需要考慮外部加上

拉或者下拉電阻,特殊情況根據需要配置。

問:我正在使用TMS320VC5402,通過HPI下載代碼,但C5402的內部只提供16K字的存儲區,請問我能通過HPI把代碼下載到它的外部擴展存儲區運行嗎?

答:不行,只能下載到片內。

問:電路中用到DSP,有時當復位信號為低時,電壓也屬于正常范圍,但DSP加載程序不成功。電流也偏大,有時時鐘也有輸出。不知為什么?

答:復位時無法加載程序。

問:DSP和單片機相連組成主從系統時,需要注意哪些問題?

答:建議使用HPI接口,或者通過DPRAM連接。

問:原來的DSP的程序需放在EPROM中,但EPROM的速度難以和DSP匹配。現在是如何解決此問題的?

答:用BootLoad方法解決。

問:我在使用5402DSK時,一上電,不接MIC,只接耳機,不運行任何程序,耳機中有比較明顯的一定頻率的噪聲出現。有時上電后沒有出現,但接MIC,運行范例中的CODEC程序時,又會出現這種噪聲。上述情況通常都在DSK工作一段時間后自動消失。我在DSP論壇上發現別人用DSK時也碰到過這種情況,我自己參照5402DSK做了一塊板,所用器件基本一樣,也是這現象,請問怎么回事?如何解決?

答:開始時沒有有效的程序代碼,所以上電后是隨機狀態,出現這種情況是正常的。

問:我使用的是TMS320LF2407,但是仿真時不能保證每次都能GO MAIN。我想詳細咨詢一下,CMD文件的設置用法,還有VECTOR的定義。

答:可能看門狗有問題,關掉看門狗。有關CMD文件配置請參考《匯編語言工具》第二章。

問:我設計的TMS320VC5402板子在調試軟件時會經常出現存儲器錯誤報告,排除是映射的問題,是不是板子不穩定的因素?還是DSP工作不正常的問題?如何判別?

答:你可以利用Memoryfill功能,填入一些數值,然后刷新一下,看是不是在變,如果是

在變化,則Memory 是有問題。

問:如何解決Flash編程的問題:可不可以先用仿真器下載到外程序存儲RAM中,然后程序代碼將程序代碼自己從外程序存儲RAM寫到F240的內部Flash ROM中,如何寫?

答:如果你用F240,你可以用下載TI做的工具。其它的可以這樣做。

問:C5510芯片如何接入E1信號?在接入時有什么需要注意的地方?

答:通過McBSP同步串口接入。注意信號電平必須滿足要求。

問:請問如何通過仿真器把.HEX程序直接燒到FLASH中去?所用DSP為5402是否需要自己另外編寫一個燒寫程序, 如何實現?謝謝!!

答:直接寫.OUT。是DSP中寫一段程序,把主程序寫到FLASH中。

問:DSP的硬件設計和其他的電路板有什么不同的地方?

答:1.要考慮時序要求;2.要考慮EMI的要求;3.要考慮高速的要求;4.要考慮電源的要求。

問:ADS7811,ADS7815,ADS8320,ADS8325,ADS8341,ADS8343,ADS8344,ADS8345中,哪個可以較方便地與VC33連接,完成10個模擬信號的AD轉換(要求16bit,1毫秒內完成10個信號的采樣,當然也要考慮價格)?

答:作選擇有下列幾點需要考慮1. 總的采樣率:1ms、10個通道,總采樣率為100K ,所有A/D均能滿足要求。2. A/D與VC33的接口類型:并行、串行。前2種A/D為并行接口,后幾種均為串行接口。3. 接口電平的匹配。前2種A/D為5V電平,與VC33不能接口;后幾種均可為3.3V電平,可與VC33直接接口。

問:DSP的電路板有時調試成功率低于50%,連接和底板均無問題,如何解決?有時DSP同CPLD產生不明原因的沖突,如何避免?

答:看來你的硬件設計可能有問題,不應該這么小的成功率。我們的板的成功率為95%以上。

問:我們的工程有兩人參與開發,由于事先沒有考慮周全,一人使用的是助記符方式編寫

匯編代碼,另一人使用的是代數符號方式編寫匯編代碼,請問CCS5000中這二種編寫方式如何嵌在一起調試?

答:我沒有這樣用過,我想可以用下面的辦法解決:將一種方式的程序先單獨編譯為.obj

文件,在創建工程時,將這些.obj文件和另一種方式的程序一起加進工程中,二者即可一

起編譯調試了。

問:DSP數據緩沖,能否用SDRAM代替FIFO?

答:不行

問:ADC或DAC和DSP相連接時,要注意什么問題?比如匹配問題,以保證A/D采樣穩定或D/A碼不丟失。

答:1. 接口方式:并行/串行;2. 接口電平,必須保證二者一致。

問:用F240經常發生外部中斷丟失現象,甚至在實際環境中只有在程序剛開始時能產生中

斷,幾分鐘后就不能產生中斷。有時只能采取查詢的方式,請問有何有效的解決方法?改

為F2407是不是要好些?

答:應該同DSP無關。建議你將中斷服務程序簡化看一下。

四十九.時鐘電路選擇原則

1,系統中要求多個不同頻率的時鐘信號時,首選可編程時鐘芯片;

2,單一時鐘信號時,選擇晶體時鐘電路;

3,多個同頻時鐘信號時,選擇晶振;

4,盡量使用DSP片內的PLL,降低片外時鐘頻率,提高系統的穩定性;

5,C6000、C5510、C5409A、C5416、C5420、C5421和C5441等DSP片內無振蕩電路,不能用晶體時鐘電路;

6,VC5401、VC5402、VC5409和F281x等DSP時鐘信號的電平為1.8V,建議采用晶體時鐘電路

五十.C程序的代碼和數據如何定位

1,系統定義:

.cinit 存放C程序中的變量初值和常量;

.const 存放C程序中的字符常量、浮點常量和用const聲明的常量;

tch 存放C程序tch語句的跳針表;

.text 存放C程序的代碼;

.bss 為C程序中的全局和靜態變量保留存儲空間;

.far 為C程序中用far聲明的全局和靜態變量保留空間;

.stack 為C程序系統堆棧保留存儲空間,用于保存返回地址、函數間的參數傳遞、存儲局部變量和保存中間結果;

.sysmem 用于C程序中malloc、calloc和realloc函數動態分配存儲空間

2,用戶定義:

#pragma CODE_SECTION (symbol, "section name");

#pragma DATA_SECTION (symbol, "section name")

五十一.cmd文件

由3部分組成:

1)輸入/輸出定義:.obj文件:鏈接器要鏈接的目標文件;.lib文件:鏈接器要鏈接的庫文件;.map文件:鏈接器生成的交叉索引文件;.out文件:鏈接器生成的可執行代碼;鏈接器選項

2)MEMORY命令:描述系統實際的硬件資源

3)SECTIONS命令:描述"段"如何定位

五十二.為什么要設計CSL?

1,DSP片上外設種類及其應用日趨復雜

2,提供一組標準的方法用于訪問和控制片上外設

3,免除用戶編寫配置和控制片上外設所必需的定義和代碼

五十三.什么是CSL?

1,用于配置、控制和管理DSP片上外設

2,已為C6000和C5000系列DSP設計了各自的CSL庫

3,CSL庫函數大多數是用C語言編寫的,并已對代碼的大小和速度進行了優化

4,CSL庫是可裁剪的:即只有被使用的CSL模塊才會包含進應用程序中

5,CSL庫是可擴展的:每個片上外設的API相互獨立,增加新的API,對其他片上外設沒有影響

五十四.CSL的特點

1,片上外設編程的標準協議:定義一組標準的APIs:函數、數據類型、宏;

2,對硬件進行抽象,提取符號化的片上外設描述:定義一組宏,用于訪問和建立寄存器及其域值

3,基本的資源管理:對多資源的片上外設進行管理;

4,已集成到DSP/BIOS中:通過圖形用戶接口GUI對CSL進行配置;

5,使片上外設容易使用:縮短開發時間,增加可移植.

五十五.為什么需要電平變換?

1)DSP系統中難免存在5V/3.3V混合供電現象;

2)I/O為3.3V供電的DSP,其輸入信號電平不允許超過電源電壓3.3V;

3)5V器件輸出信號高電平可達4.4V;

4)長時間超常工作會損壞DSP器件;

5)輸出信號電平一般無需變換

五十六.電平變換的方法

1,總線收發器(Bus Transceiver):

常用器件: SN74LVTH245A(8位)、SN74LVTH16245A(16位)

特點:3.3V供電,需進行方向控制,

延遲:3.5ns,驅動:-32/64mA,

輸入容限:5V

應用:數據、地址和控制總線的驅動

2,總線開關(Bustch)

常用器件:SN74CBTD3384(10位)、SN74CBTD16210(20位)

特點:5V供電,無需方向控制

延遲:0.25ns,驅動能力不增加

應用:適用于信號方向靈活、且負載單一的應用,如McBSP等外設信號的電平變換

3,2選1切換器(1 of 2 Multiplexer)

常用器件:SN74CBT3257(4位)、SN74CBT16292(12位)

特點:實現2選1,5V供電,無需方向控制

延遲:0.25ns,驅動能力不增加

應用:適用于多路切換信號、且要進行電平變換的應用,如雙路復用的McBSP

4,CPLD

3.3V供電,但輸入容限為5V,并且延遲較大:>7ns,適用于少量的對延遲要求不高的輸入信號

5,電阻分壓

10KΩ和20KΩ串聯分壓,5V×20÷(10+20)≈3.3V

五十七.未用的輸入/輸出引腳的處理

1,未用的輸入引腳不能懸空不接,而應將它們上拉活下拉為固定的電平

1)關鍵的控制輸入引腳,如Ready、Hold等,應固定接為適當的狀態,Ready引腳應固定接為有效狀態,Hold引腳應固定接為無效狀態

2)無連接(NC)和保留(RSV)引腳,NC 引腳:除非特殊說明,這些引腳懸空不接,RSV引腳:應根據數據手冊具體決定接還是不接

3)非關鍵的輸入引腳,將它們上拉或下拉為固定的電平,以降低功耗

2,未用的輸出引腳可以懸空不接

3,未用的I/O引腳:如果確省狀態為輸入引腳,則作為非關鍵的輸入引腳處理,上拉或下拉為固定的電平;如果確省狀態為輸出引腳,則可以懸空不接

電子發燒友App

電子發燒友App

評論