|

A New Standard for Multiprocessing DSP Systems Today's applications for computer technology are more demanding than ever before, and no where is this more evident than in the world of digital signal processors (DSPs). DSP chip manufacturers and board vendors are responding to this need with products that possess an inherent ability to support scalable, multiprocessing system architectures. These systems are powerful enough to address the most demanding DSP applications of today and provide a clear upgrade path for the future. The most common DSP applications involve a completely embedded system that is dedicated to performing a particular task in real time. As with all computer applications, speed is of the essence both for processing and data I/O. In addition, constraints on available space and power may further complicate the picture. Requirements such as these present a significant challenge that DSP chip designers and board vendors must face head on. Multiprocessing computing has emerged as the only viable way of addressing a vast assortment of high-end DSP applications. Applications that require multiprocessing computing performance include medical, 3D graphics acceleration, military, industrial control, high end audio, telephony, and wireless communications infrastructure. The metrics that designers of these systems judge DSP performance by are processing per dollar, processing per watt, and processing per area. The real advantage of multiprocessing systems is the ability to tune the performance and cost of a system to yield the required functionality and processing performance. This feature of multiprocessing system architectures is known as scalability. A scalable architecture allows users to tune performance based on the number of processing nodes required. In fact, the ability of a multiprocessing system to scale is not just convenient, it's required; and the ability to design scalable multiprocessing systems starts at the chip level. The new ADSP-21160 SHARC processor, with its large internal memory blocks, multiple internal bus structure, and integrated I/O subsystem, possesses all of the features necessary to build multiprocessing systems that provide true scalability to any number of processors. Like its predecessor (the ADSP-21060 SHARC), the ADSP-21160 is setting the pace for high-performance multiprocessing floating-point DSP systems. |

| Defining Multiprocessing Systems |

|

Processor technology has progressed at such a fast rate over the past decade that most of us cannot even remember how impressed we were with the power of our new 80286 PCs in the late 80's. But while chip manufacturers have awed us with their huge strides in processor technology, they have also exposed the performance limitations inherent in single-processor systems. Thus it is not surprising that high-performance system designers have started using aggregates of processors to build more powerful (multiprocessing) computing systems. |

|

Figure 1. Multiprocessing Systems: |

|

This trend has become very apparent in the embedded DSP industry. As DSP applications become more and more demanding, board-level suppliers are responding with PCI and VME system components that squeeze larger numbers of processors into smaller spaces. Packaging technology has played a role here, as DSP chip-level manufacturers developed smaller package sizes that are relatively easy to cool. However, a system of multiple processors cannot be considered truly multiprocessing based solely on the fact that more than one processor is used. The term multiprocessing implies that the processors in the system are able to work together, in an efficient manner, to perform the required calculations. This means that the exchange of data between processors is critical, and an effective multiprocessing DSP must possess a means for achieving this data transfer. The SHARC processor family has answered this challenge with an internal I/O processor (or DMA engine) that allows data communication to occur without impeding the progress of the processing core. As a result, every time a SHARC processor is added to a multiprocessing network, both processing horsepower and data communication bandwidth are increased. This feature of the SHARC family, together with its unique link-port architecture, is one of the most important ingredients in its ability to support multiprocessing system design. The new ADSP-21160 has increased the number of DMA channels over those available in the first generation ADSP-21060 SHARC from 10 to 14. This allows for a separate independent DMA channel for the transmit and receive buffers of the 2 serial ports, the 6 bi-directional link port buffers, and 4 bi-directional external port buffers. With these enhanced DMA capabilities, the ADSP-21160 has the flexibility to support a variety of scalable multiprocessing system architectures. |

| The Link Port Architecture |

|

Multiprocessing system architectures come in two basic flavors: shared memory and distributed memory. The ADSP-21160 SHARC possesses built-in features that allow it to gluelessly support both of these architectures, as well as architectural hybrids. The key lies in the ADSP-21160's unique link-port architecture. In shared memory systems, every processor has access to a global memory block (made up of internal and external memory) with processors exchanging data via a shared bus. This approach is reminiscent of traditional single-processor programming since all of the data is located in a single memory block. However, the shared memory architecture lacks the inherent ability to scale, since the addition of each new device on the bus decreases the average bus bandwidth available to each processor. The SHARC family of processors gets around this issue through the use of dedicated data communication ports known as link ports. Link ports provide high-bandwidth, point-to-point connections between processors for the sole purpose of inter-processor communication. This allows the ADSP-21160 to support a distributed memory architecture in which all inter-processor communication takes place over the links, leaving the full bandwidth of the data bus for servicing external memory and I/O peripherals. Distributed memory architectures are truly scalable, and they allow users to configure very large scale multiprocessing networks using a natural mesh-like architecture. One of the key strengths of the link-port architecture, however, is that system designers are not forced to choose between shared and distributed memory. Architectural hybrids combining these two philosophies are easy to construct, allowing users to glove-fit their system to their application. The ADSP-21160's ability to support these multiple system architectures is another key aspect of system scaling. System designers are provided the freedom to easily tune their system's form and functionality as well as processing performance. |

| A Balanced Approach |

|

It is well known that the most serious problem facing multiprocessing DSP system and chip-level designers is data flow. In order for a DSP to even approach its peak computational performance, it must be fed with a constant stream of data. This means that a multiprocessing system's ability to route data among the various nodes in the system is equally as important as its ability to process the data. Early multiprocessing system architectures suffered from the malady of having high theoretical MFLOPS numbers but very few usable MFLOPS. This came about as a result of attaching rather inefficient communication engines to very high-performance RISC-style processors that were not designed to be used in multiprocessing systems. The result was a sub-linear scaling characteristic in which system performance increased only slightly as processors were added to the system. The SHARC processing family, on the other hand, places its I/O subsystem and processing core on equal footing, creating a balance between processing and data routing efficiency. This balance allows the DSP application to supply the 21160's high-speed SIMD core with a constant stream of data, resulting in a nearly linear scaling over a wide range of system sizes. Of course taking advantage of this balance in an actual application is a software development function as well. Third party board-level and software vendors supply software development tools for the SHARC family of processors to simplify this effort. Today a variety of native and portable programming tools are available including SHARC-specific run-time environments and industry-standard real-time operating systems. These products not only simplify the task of targeting an application at a multiprocessing network, they also help programmers to take full advantage of the SHARC's balanced hardware design and squeeze the maximum performance out of their embedded SHARC systems. |

| COTS and the Multiprocessing DSP |

|

Multiprocessing digital signal processing systems have become common place in a wide variety of military and commercial applications including RADAR, SONAR, industrial control, image processing and telecommunications. As the need for higher speed and more compact systems arises, multiprocessing DSP systems will become even more widespread. One the fastest growing opportunities for the ADSP-21160 processor is the commercial off the shelf (COTS) board-level vendor market. The use of COTS products has become a mandate (over custom board developments) for both military and commercial users. Fueling this trend is a need for lower product development costs and a faster time to market. The SHARC family, with its unique multiprocessing architecture, lends itself very well to the development of modular system components that can be used together to build high-end multiprocessing systems with essentially any performance and functionality characteristics. This flexibility is the key feature required by COTS customers. Potential application areas for the 21160 appear boundless, with opportunities in many different markets. Regardless of the application, however, it is clear that the multiprocessing movement is here to stay in the embedded DSP marketplace. The ADSP-21160 SHARC from Analog Devices has secured a position to lead this processing revolution into the next millennium, truly setting a new standard for multiprocessing digital signal processing. |

A New Standard for Multiproces

- dsp(343840)

- System(36551)

相關推薦

New Balance 首款智能手表發售 售價299美元

此前報道,New Balance在CES 2017期間帶來他們的首款運動智能手表RunIQ。而近日,New Balance正式發售了這款運動智能手表。

2017-02-06 10:48:01 1217

1217

1217

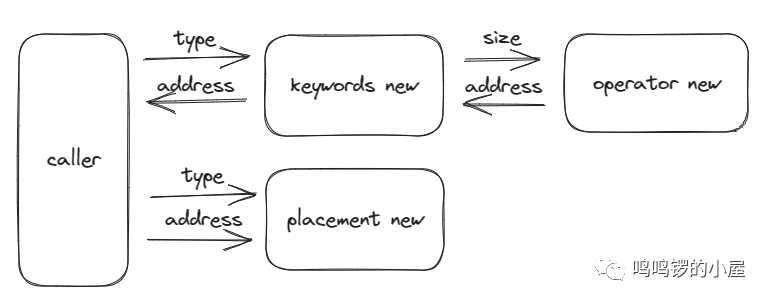

1217SystemVerilog中的類構造函數new

在systemverilog中,如果一個類沒有顯式地聲明構造函數(new()),那么編譯仿真工具會自動提供一個隱式的new()函數。這個new函數會默認地將所有屬性變量。

2022-11-16 09:58:24 2700

2700

2700

27004288A技術概述

A new standard in high-speed measurement solutions for ceramic capacitor production tests

2019-09-06 15:01:05

New Nordic nRF2460 audio streamer IC

into the new nRF2460 chip.”"We have tested a wide range of wireless monoaudio solutions from

2011-07-02 11:42:21

Standard Pad和Standard Plus Pad上支持的S32K344 LPSPI最大總線速率是多少?

Standard Pad 和 Standard Plus Pad 上支持的 S32K344 LPSPI 最大總線速率是多少?

2023-03-29 07:14:30

ATSC Standard:AVC Video Transport Subsystem Characteristics

ATSC Standard:AVC Video Transport Subsystem CharacteristicsIn issuing this standard, the ATSC

2008-10-16 08:36:37

AVS Video Standard

versionof AVS video standard in December 2003 [I],an dexpects to be approved as a national standard in2004.

2008-06-25 09:55:20

Agilent 33220A,Visual C ++簡單的正弦波程序?

am new to programming agilent devices thru VC++.Does anyone have the code to Generate a Standard

2019-05-22 08:18:38

DVB資料大全-EIA STANDARD

of theaudio, video and ancillary data processing standard for Advanced Television. The DTV standard

2009-12-18 12:05:50

Direct Mode Coding For Bi-Predictive Pictures in the H.264 Standard

Direct Mode Coding For Bi-Predictive Pictures in the H.264 StandardThe new H.264 (MPEG-4 AVC) video

2008-06-25 09:58:00

H.264 MPEG-4 White Paper

a new generationof internet-based video applications whilst the ITU-T H.263 standard for video

2008-06-25 10:18:21

IEEE 1394 Standard

4IEEE 1394 Standard1394Open Host Controller InterfaceSpecificationRelease 1.1January 6, 2000

2008-06-26 10:09:41

IEEE Standard for Verilog Hardware Description Language 1364-2005

IEEE Standard for Verilog Hardware Description Language 1364-2005IEEE原版 Verilog HDL 2005標準

2013-01-05 18:47:00

LED球泡燈AS/NZS5341能效測試MEPS證書

`澳大利亞/新西蘭新標準AS/ NZS 5341-2020 ,LED光源測試方法-能效及性能要求Australian/New Zealand New Standard AS/NZS 5341

2021-04-17 08:51:14

LED電源GL8212 /NEW3A 兼容電感鎮流器

保護(OLP)自動恢復-SOT-23-6封裝- 兼容電感鎮流器- 不兼容的電子鎮流器GU10/E14LED燈泡GL8212/NEW3A極限工作范圍VCC 供電電壓30V CT,COMP, CS

2016-02-26 20:44:26

Overview of AVS Video Standard

],an dexpects to be approved as a national standard in2004. This version mainly targets at high definitionand

2008-06-04 13:55:04

SCPI命令在E5070A和E5080A之間有所不同

use this: SENS:SWE:TIME 5 Is this new command set going to be the new standard for ENA analyzers

2018-10-08 14:31:39

The digital Video Standard according to ITU-R BT. 601/656

The digital Video Standard according to ITU-R BT. 601/656Leveldiagram at the input of an A/D converter for theanalogue component signals Y , CB , CR

2009-06-13 00:00:15

Unified Constant-Frequency Integration Control of Three-Phase Standard Bridge Bo

integrationcontroller for PFC is proposed. For the standard bridge boostrectifier, a unity power factor and low

2011-09-10 23:19:15

【轉載消息】Proteus 8.6 - New Features

/whatsnew/#8.6Proteus 8.6 - New FeaturesVersion 8.6 is a significant release in our PCB development

2017-01-22 14:16:01

基于LAN的模塊化儀器

that links individual hardware and software test modules together to emulate standard test instruments in a new compact form factor.

2019-09-26 06:57:00

如何區分3000與3000new

1、2017/1/5默納克系統常見問題之四如何區分3000與3000new | 默者默納克系統常見問題之四如何區分3000與3000new默納克控制系統主要是NICE3000系列, 市面上面主要

2021-09-17 07:03:49

是德科技Medalist 5DX自動X射線檢查AXI系統

A new algorithm family called FET for the Keysight Medalist 5DX automated X-ray inspection (AXI

2019-11-06 15:59:14

求大神講解一下Windows Embedded Standard 7

大神開課了,有關Windows Embedded Standard 7你不知道的知識都在這里。

2021-04-27 06:35:41

精密組件,半導體和材料測量的新標準

A new standard for precise component, semiconductor and material measurements

2019-11-06 14:21:45

請問C++用new和不用new創建類對象區別是什么?

起初剛學C++時,很不習慣用new,后來看老外的程序,發現幾乎都是使用new,想一想區別也不是太大,但是在大一點的項目設計中,有時候不使用new的確會帶來很多問題。當然這都是跟new的用法有關

2020-11-05 07:27:40

镃心耗塤新算法 A New Core Loss Model For Iron Powder Material

镃心耗塤新算法 A New Core Loss Model For Iron Powder MaterialThe total core loss of a material can

2009-10-31 08:47:31

h.264 standard pdf

H.264 video compression standard.New possibilities within video surveillance.

Table of contents1.

2008-06-04 14:09:37 22

22

22

22ieee 802.16 standard (標準)

802.16TM ConformanceIEEE Standard for Conformance to IEEE 802.16Part 1: Protocol

2008-07-24 00:40:43 4

4

4

4Overview of AVS Video Standard

Overview of AVS Video Standard

This paper overviews the AVS video standard interms of basic

2008-08-20 11:48:32 15

15

15

15IEC60730-1 standard

The IEC60730-1 standard describes the requirements of “Automatic ElectricalControls for Household

2008-09-12 10:37:14 102

102

102

102IEEE Std 1076-2002 Standard

1076TM IEEE Standard VHDL Language Reference Manual

IEEE Computer Society Sponsored by the Design

2008-10-21 15:33:38 1

1

1

1IEEE Standard VHDL Language Re

IEEE Standard VHDLLanguage Reference ManualSponsorDesign Automation Standards Committeeof theIEEE

2008-10-21 15:35:02 44

44

44

44IEEE Std 1364-2001 Standard

IEEE Standard Verilog Hardware Description Language SponsorDesign Automation Standards Committee

2008-10-21 15:37:08 24

24

24

24IEEE Standard Verilog Hardware

IEEE Standard Verilog Hardware Description Language

(This introduction is not part of IEEE Std

2008-10-21 15:37:44 0

0

0

0Keysight MSOX6002A雙通道混合信號示波器

MSO / MDO示波器, InfiniiVision 6000 X-Series, 2+16 通道, 1 GHz, 20 GSPS, 4 Mpts, 350 ps**New integration

2022-07-30 14:12:39

The new fieldbus standard in A

Fast “Time to Market”Cheaper than own developmentEasy to configureMFP3 technology

2009-04-11 08:53:16 1

1

1

1D 257-99 (Standard Test Method

Standard Test Methods for DC Resistance or Conductance of Insulating Materials1This standard

2009-08-14 21:35:05 18

18

18

18A New High Gain Low Voltage 1.

A New High Gain Low Voltage 1.45GHz CMOS Mixer:Abstract—A new architecture of CMOS downconversion

2009-09-08 20:41:48 9

9

9

9A New Hybrid Neural System Int

A New Hybrid Neural System Interfacing Neurons and Silicon Hardware for Fast Signal Recognition

2009-09-08 20:42:53 5

5

5

5Research for new method for hi

This paper explores a kind of new method of high-precision non-contactmeasurement of rotate speed

2009-09-09 15:45:39 6

6

6

6Enabling New Infotainment-Equi

Enabling New Infotainment-Equipment Cost Structures With Open-System Architectures:The infotainment

2009-10-06 14:42:27 9

9

9

9A New Three-Phase Power-Factor

A New Three-Phase Power-Factor Correction (PFC) Scheme Using Two Single-Phase PFC Modules:Abstract

2010-03-01 17:42:23 36

36

36

36EPON Ushers In a New Generatio

EPON Ushers In a New Generation of Bandwidth-Intensive Applications白皮書

Based on fiber-optics, EPON

2010-03-24 16:12:59 9

9

9

9What’s New in PADS 9.0

PADS 9.0 introduces exciting new functionality to the PADS flow, including PADSLayout, PADS Router

2010-03-27 08:27:07 0

0

0

0The New Personal International

The New Personal International Language Esata:1. Introduction to Esata2. Esata Alphabet

2010-04-11 08:53:56 44

44

44

44Windows Embedded Standard 7與Wi

Windows Embedded Standard 7與Windows Embedded Standard 2009在組件化、工具和映像創建等方面的對比

本文介紹了Windows Embedded Standard 2009和Windows Embedded Standard 7在組件化、工具

2010-04-15 14:00:00 18

18

18

18New Measurement Requirements f

digitalinformation at higher speeds. This need has put new requirements on transformer manufacturers andpresented new challenges to test equ

2010-06-10 08:19:20 10

10

10

10NEW POLYMERS FOR IMPROVED FLOC

flocculants• Introduce New Family of Flocculants– Description of flocculant chemistry– Laboratory development re

2010-07-01 18:36:45 10

10

10

10New Enhanced Agilent Nano Suit

Features and Benefits• New test method development offers easier, more user-friendly protocol

2010-08-13 09:43:00 6

6

6

6Windows Embedded Standard簡介及在中

1.Windows Embedded Standard簡介

看到Windows Embedded Standard,或許有些人會感到疑惑,但如果說起微軟的XP Embedded (XPE),相信大多數人就明白了。作為Windows三

2009-03-12 14:53:54 1189

1189

1189

1189Brand New XP-8000-CE6 Release:

Brand New XP-8000-CE6 Release: More Powerful, More Attractive

2010-01-06 11:37:21 829

829

829

829什么是ASCII (American Standard Co

什么是ASCII (American Standard Code for Information Interchange)

英文縮寫: ASCII (American Standard Code for Information Interchange)

中文譯名:

2010-02-22 09:57:01 650

650

650

650炬光科技和New Source Technology LLC簽署代理協議

炬光科技宣布,與New Source Technology LLC (NST)正式簽署合作協議,由美國NST公司代理炬光科技全系列半導體激光器產品在美國市場的銷售和技術服務。

2012-01-15 18:10:17 1029

1029

1029

1029TMS320_DSP_Algorithm_Standard_Demonstration_Application

TMS320 DSP Algorithm Standard Demonstration Application。

2016-01-19 14:16:49 6

6

6

6Designing with a New Super Fast

Designing with a New Super Fast Dual Norton Amplifier

2017-03-24 15:48:30 0

0

0

0Topics on Using the LM6181-A New

Topics on Using the LM6181-A New Current Feedback Amplifier

2017-03-23 17:34:50 0

0

0

0612 2.5SSD demo board (Standard version)

612 2.5SSD demo board (Standard version)

2017-11-23 10:14:35 4

4

4

4placement new詳解

placement new是重載operator new的一個標準、全局的版本,它不能被自定義的版本代替(不像普通的operator new和operator delete能夠被替換成用戶自定義的版本)。

2018-03-02 14:24:56 0

0

0

0PADS Standard Plus工具的功能介紹

PADS Standard Plus提供了靈活的兼容性,強大的系統設計和規則設置功能,是高效和易用的PCB工具。

2019-05-15 06:57:00 3754

3754

3754

3754PADS Standard和PADS Standard Plus的功能概括

探討 PADS Standard 和 PADS Standard Plus 所包含的功能。PADS Standard 可滿足專注于原理圖和 PCB 設計的工程師的需求。PADS Standard Plus 則主要提供給要求分析和驗證優勢的硬件工程師使用。

2019-05-15 06:03:00 8373

8373

8373

8373

New IP提出的背景是什么?什么是New IP?

盡管國外媒體已經發現New IP類似6G,是正常的面向未來十年的IP技術演進研究,但國內外還是有不少不明真相(甚至揣著明白裝糊涂)的媒體,將英國金融時報該文翻譯后多地發布,誤導了不少人。

2020-05-18 15:41:53 2859

2859

2859

2859如何讓new操作符不分配內存,只構造

placement new 就可以解決這個問題。我們構造對象都是在一個預先準備好了的內存緩沖區中進行,不需要查找內存,內存分配的時間是常數;而且不會出現在程序運行中途出現內 存不足的異常。所以,placement new非常適合那些對時間要求比較高,長時間運行不希望被打斷的應用程序。

2021-01-19 17:01:16 1770

1770

1770

1770Windows Media Audio (WMA9) Standard Decoder for Blackfin

Windows Media Audio (WMA9) Standard Decoder for Blackfin

2021-02-01 10:50:13 5

5

5

5程序員如何自己new一個對象

https://www.ciphermagic.cn/java8-builder.html 程序員經常會遇到靈魂拷問:你有對象嗎? 沒有,但我可以 new 一個! public class

2021-09-22 09:37:40 2675

2675

2675

2675new[] 和 delete[]能不配對使用嗎

在平時資料中,我們常看到: new和delete,new[]和delete[]一定要配對使用! 也 有人說: 有時候不配對使用也不會出現問題。 也許你也是只知其然,不知其所以然,然而我也有

2021-11-17 10:24:00 1201

1201

1201

1201UVM中類的例化用new還是create

UVM中類的例化用new和create有什么不同?什么時候可以用new?什么時候該用create?

new是OOP自帶屬性,create是UVM override屬性,可以理解成create比new更進階~

2023-03-21 11:26:46 661

661

661

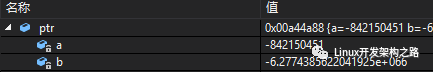

661C++內存管理operator new和placement new

最近在看一些C++資料的過程中,說到在初始化列表中使用關鍵字new來分配新內存不是異常安全的,應該使用運算符new。

2023-07-22 09:58:35 424

424

424

424

new和malloc的區別

1. 申請的內存所在位置 new操作符從自由存儲區(free store)上為對象動態分配內存空間,而malloc函數從堆上動態分配內存。自由存儲區是C++基于new操作符的一個抽象概念,凡是通過

2023-11-11 11:29:10 285

285

285

285

Standard cell是怎么應用到我們的后端設計中的呢?

Standard cell,標準單元,或者簡稱cell,可以說是數字芯片后端最基本的概念之一了,甚至可能沒有接觸過后端的同學也有所耳聞?

2023-12-04 11:44:40 327

327

327

327 電子發燒友App

電子發燒友App

評論